1、display的使用

在verilog中虽然没有system verilog的assertion,但是我们依旧可以使用display打印检查各类错误,在RTL级的仿真中能够快速定位问题。

例如:

检查不合理的配置,不合理的配置组合;

检查不合理的输入数据类型,例如vld/sop/eop 组合缺少了sop或者eop;

案例:

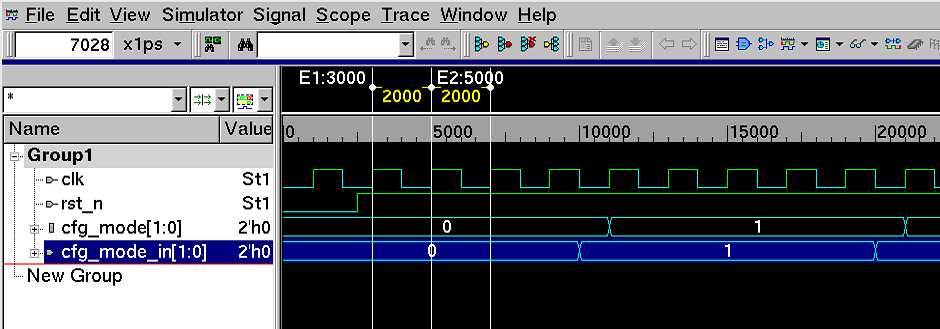

如下案例中,如果复位释放且cfg_mode_in为INVLD_CFG状态,则打印ERROR。%0t表示的是以当前时间格式显示,即仿真中的时间。%0t中的0指的是以数值的真实位宽显示,不会额外再补充0。%m 显示当前模块层级,即下图中的display_exp_top.u_display_exp。$write在屏幕显示时是不换行的,$display自带换行符,显示后换行。

Verilog代码

`timescale 1ns/1ps`define INVLD_CFG 2'b0module display_exp ( input clk , // input rst_n , // input [1:0] cfg_mode_in //); reg [1:0] cfg_mode ; always@(posedge clk or negedge rst_n)if(~rst_n) cfg_mode <= 1'b0;else cfg_mode <= cfg_mode_in; `ifdef WAR_ERR_PRINT always@(posedge clk or negedge rst_n) if((rst_n==1)&&(cfg_mode_in==`INVLD_CFG)) begin $write("%0t ps: %m : ERROR : ", $time) ; $display("cfg_mode not be INVLD CFG when rst_n is release") ; end `endifendmodule

Testbench

module display_exp_top(); reg clk; reg rst_n; reg [1:0] cfg_mode_in ; initial begin clk = 0; forever #1 clk = ~clk; end initial begin rst_n = 1'b0; #2.5 rst_n = 1; end display_exp u_display_exp( .clk(clk), .rst_n(rst_n), .cfg_mode_in(cfg_mode_in) ); initial begin cfg_mode_in = 2'b0 ; #10 cfg_mode_in = 2'b1 ; #10 cfg_mode_in = 2'b10 ; #10 cfg_mode_in = 2'b11 ; end endmodule

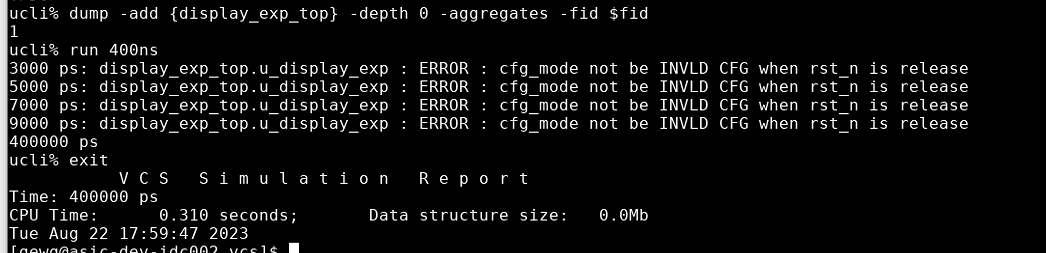

2、打印效果

3、注意事项

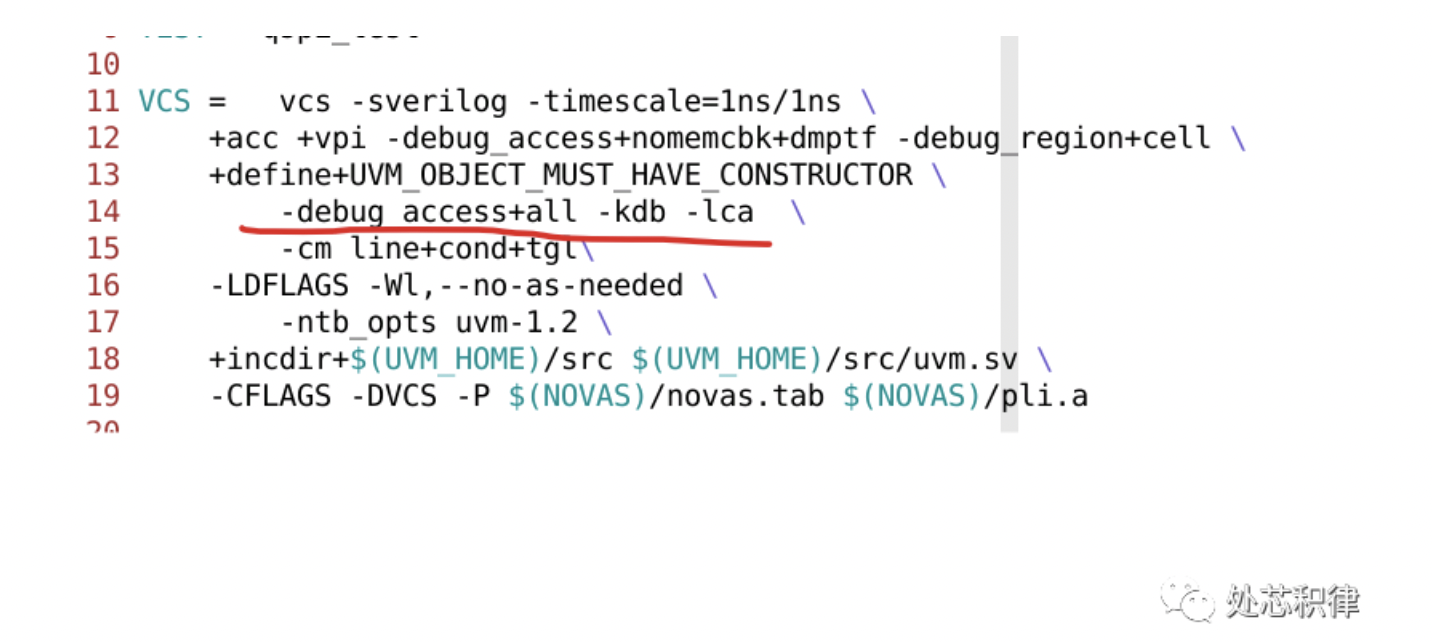

$write和$display是不可综合的语句,因此在设计中,我们通常使用宏定义来生效打印语句。案例中就采用了`ifdef WAR_ERR_PRINT和`endif。在RTL仿真中,可以生效WAR_ERR_PRINT,而在综合时不能生效WAR_ERR_PRINT。

4、打印的优缺点

采用$display的优势在于它不会占用硬件资源,因此设计人员可以添加任意多的检测语句,方便快速定位问题。缺点就是不可综合,在网表中以及芯片中不存在此检测手段,无法像中断,统计计数那样去debug问题。

审核编辑:刘清

-

芯片设计

+关注

关注

15文章

1171浏览量

56775 -

仿真器

+关注

关注

14文章

1052浏览量

88182 -

RTL

+关注

关注

1文章

395浏览量

62867 -

Verilog语言

+关注

关注

0文章

113浏览量

8825

原文标题:Verilog :使用display 提高debug效率

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

提高LED驱动电源效率的八种技巧

提高待机效率的方法

如何提高线性稳压器的效率呢

怎么通过修改电源选项提高cpu使用效率呢

怎么才能提高开关电源的效率呢

如何提高伺服液压机的作业效率

有没有办法像debug RTL代码一样将UVM中变量拉到波形上看呢?

如何使用display提高debug效率呢?

如何使用display提高debug效率呢?

评论