说到本文内容,可能需要先唠唠半导体、微电子和集成电路之间的关系。

半导体产业往往指以半导体材料为基础的整个产业链生态,这里可以包括半导体材料的生产(属于化学产业),利用半导体材料生产加工的产业,帮助半导体材料生产加工的工具设计及生产产业......是一个非常广泛的产业链体系。

微电子从字面理解来看,就是小型电子产品的设计、生产、制造产业,小到多少呢?一般说来我们认为产品的金属线条最宽不要超过10um吧(参考最早的晶体管尺寸看)。

集成电路设计产业,重点是“设计”,是隶属于半导体和微电子产业的一个分支。是利用设计工具,设计一个将不同微小电子器件集合在一个电路,以实现相应功能的过程。微小电子器件,就参考微电子的尺寸吧。而因为现在大部分集成电路设计都是使用半导体材料为硬件载体来实现功能的,所以又隶属于半导体产业。

多说一句,一个比较容易迷惑的概念就是芯片,我们一般将集成电路产品的成品形态叫做芯片,但还有一种生物芯片的概念,与电路没有关系,是纯生物学反应的一块chip上面可以检测出巨大的生物信息,所以叫做芯片。不属于电子学范畴,更不是半导体产业了。

晶圆怎么来的?

集成电路设计的产品,基于半导体材料实现硬件载体,这里要说的是衬底材料,也就是晶圆最原始的材料,一般说这些材料可以分为元素半导体和化合物半导体,其中元素半导体多见于Ge(锗)、Si(硅)这些六价元素。而化合物半导体,是合成半导体材料,如GaAs(砷化镓)、GaN(氮化镓)、Ga2O3(氧化镓)、SiC(碳化硅)等。根据不同材料的电气特性,可以设计不同应用的产品。

- Si元素地球上含量大,具有耐高压、反向漏电流小、效率高、使用寿命长、可靠性好、热传导好,并能在200高温下运行等优点,所以常被应用在大规模集成电路(VLSI,Very Large Scale Integration Circuits)的基底材料。

- GaAs(砷化镓),高频、高温、低温性能好,噪声小、抗辐射能力强,适用于制作转移器件,适用于高频场合,如移动电话、卫星通讯、微波点对点连线、雷达系统等。缺点在于有毒,且生产工艺要求较高,与Si相比,不易于规模化生产(Si晶圆有12寸,但纯GaAs晶圆主流只有6寸)。

- GaN(氮化镓)作为砷化镓的下一代产品,禁带宽度大,可以有更好的线性度和耐压性,并提供较大的电流驱动能力,所以现在常被用于快充设备的充电驱动芯片。

以Si晶圆为例,如果想拿到硅晶圆,则首先需要生产硅晶棒(单晶硅硅锭),具体的生产流程不做赘述,简单说来就是靠高温融化固体硅材料,然后通过旋转晶种,使得其他硅晶体按照整齐的格式重新吸附在晶种周围,越长越大。最后实现硅晶棒,其直径一般就是4寸、6寸(~100mm)、8寸(~200mm)、12寸(~300mm)等。

之后,需要将硅锭切成厚度均匀的薄片,这就是最原始的单晶硅晶圆。

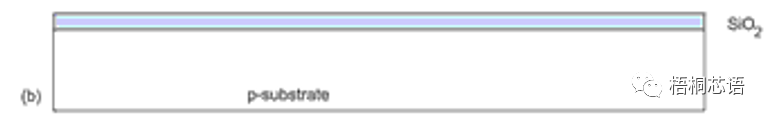

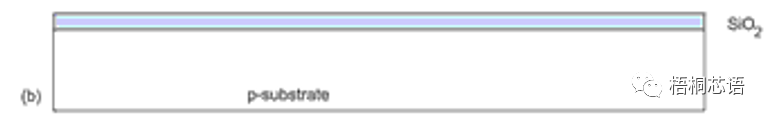

原始的单晶硅晶圆是无法用于生产的,同时由于Si元素无法单独稳定存在于现实环境中,其表面会形成一层二氧化硅(SiO2),如下面蓝色部分。

所以在做生产之前,需要先对单晶硅晶圆进行研磨(把SiO2层去除)、抛光(确保表面光滑,晶格结构整齐)、外延掺杂(外延掺杂三价元素,如硼、镓等,使得晶圆为p型衬底晶圆)(外延掺杂五价元素,如磷、锑、砷等,使得晶圆为n型衬底晶圆)。如下所示黄色部分:

而外延掺杂后的晶圆内部晶格也会发生一些变化,下图中(a)是没有掺杂的单晶硅,(b)是掺杂了砷元素的n型衬底晶圆,(c)是掺杂了硼元素的p型衬底晶圆。一般来说我们主要使用p型衬底晶圆进行生产。

掺杂的工艺很多,比如说电镀工艺、溅射工艺、蒸发工艺、化学沉淀工艺(CVD)等,衬底外延掺杂一般用的就是CVD工艺了。

当然如果外延掺杂其他元素,如GaAs,之后的晶圆也可以用于GaAs衬底进一步生产使用。

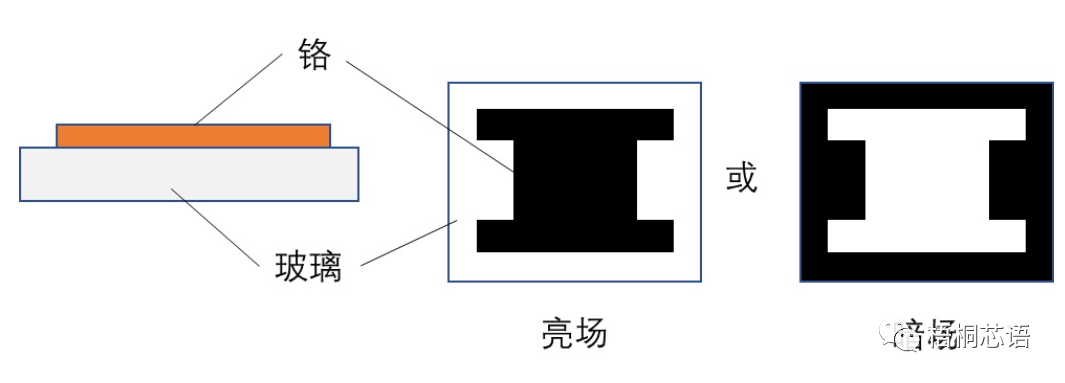

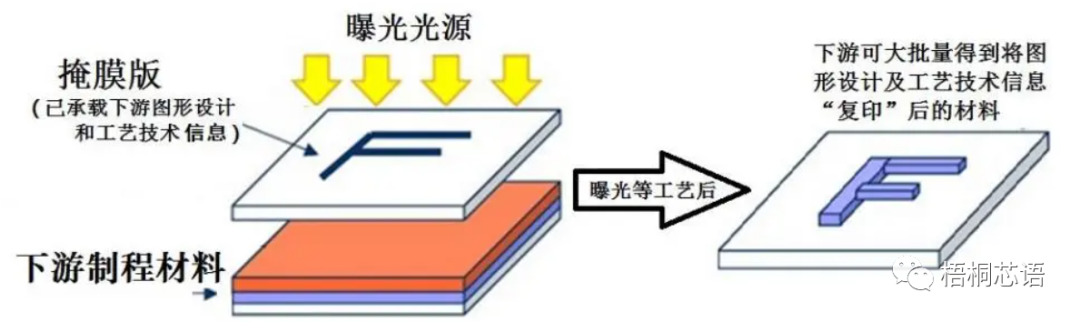

MASK(掩膜板)是什么?

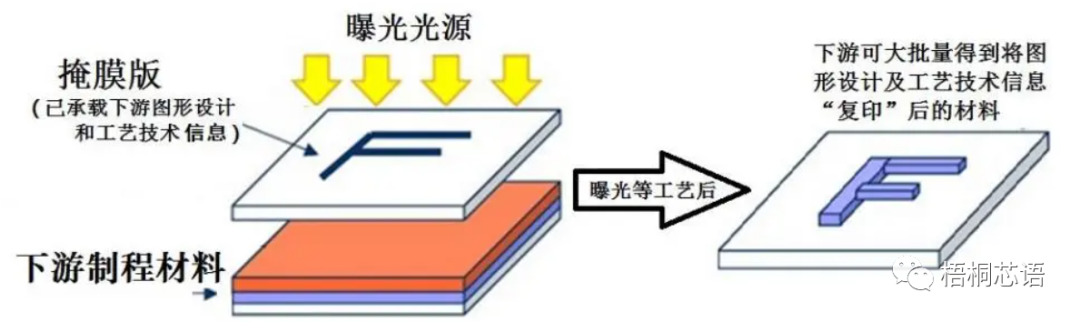

在晶圆上生产芯片的前提,是先做好掩膜板。掩膜板是一种在玻璃(石英板)上利用铬金属实现不同图案的板子。石英板是透光的,而铬金属是阻光的,所以根据铬的形状,光透过板子,就会在板子另一面显影出图形的样子。(这和照相底片的原理是类似的)

实际在生产的时候还会利用缩图透镜缩小尺寸,在晶圆上达到实际芯片的尺寸。

掩膜板是一个大约26mmx32mm的长方形板子,而制造一颗晶圆需要的图形不止一层掩膜板,根据实际工艺的不同,每个芯片所需的掩膜板数量不同,而因为掩膜板制造工艺属于高端工艺,价格不菲,因此越是功能复杂,可靠性要求高,功耗和性能同时有要求,那么掩膜板层数也会比较多,NRE成本(28nm工艺一层mask大约为7万美元)和生产成本也相应提高了。

需要注意的是,一般说来芯片不是非常大,一块掩膜板上可以同时做多个芯片的图形。生产时,需要移动掩膜板多次,才能在一张晶圆上完成该层图形的光刻工作。

*** Photolithography (光刻)是什么?***

通过掩膜板在晶圆上实现光刻,是生产芯片过程中非常重要的动作。每一次光刻都需要做以下步骤的工作:

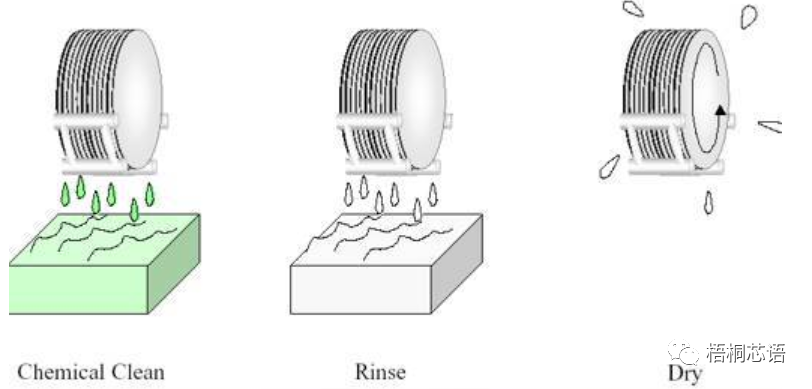

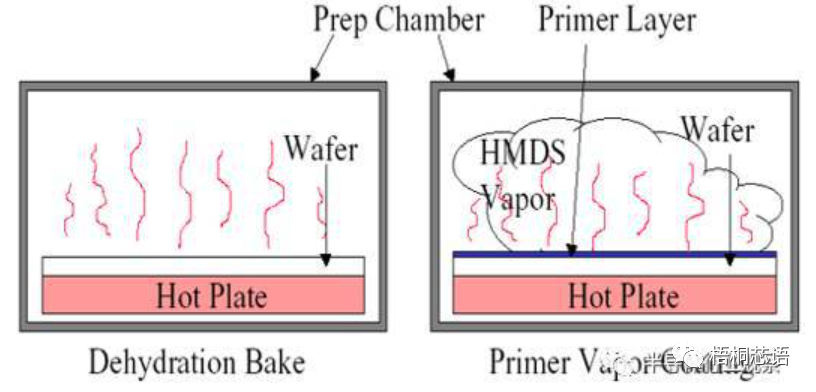

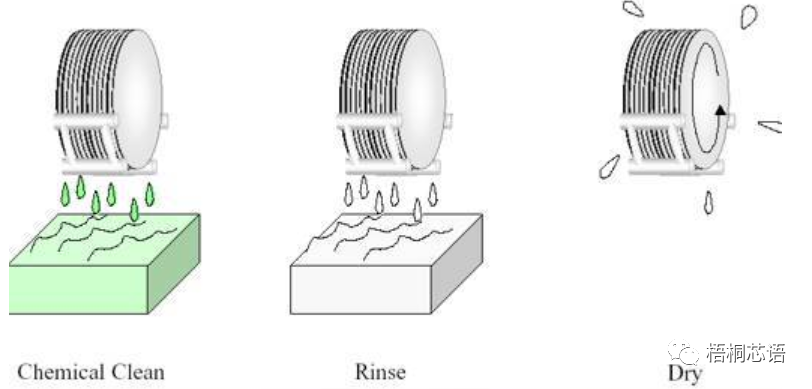

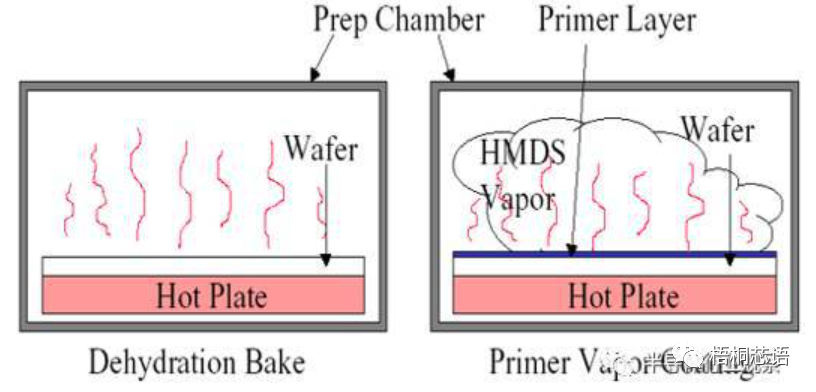

- 表面准备:清洗和烘干表面(清洗硅片的目的是去除污染物去除颗粒、减少针孔和其它缺陷,提高光刻胶黏附性。烘干是为了除去晶圆表面潮气,增加光刻胶和表面黏附性)

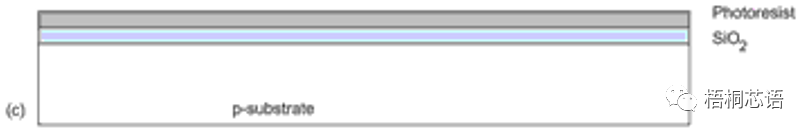

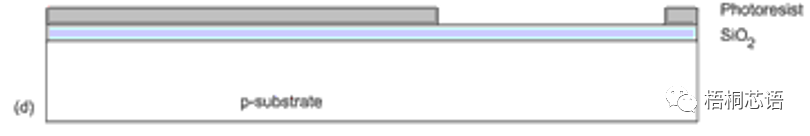

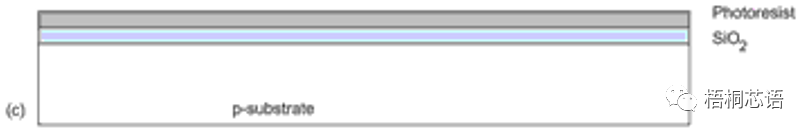

完成以上工作后,晶圆表面干净整齐,准备涂光刻胶。以晶圆第一层光刻工作为例,由于表面氧化,此时SiO2层是晶圆表面层:

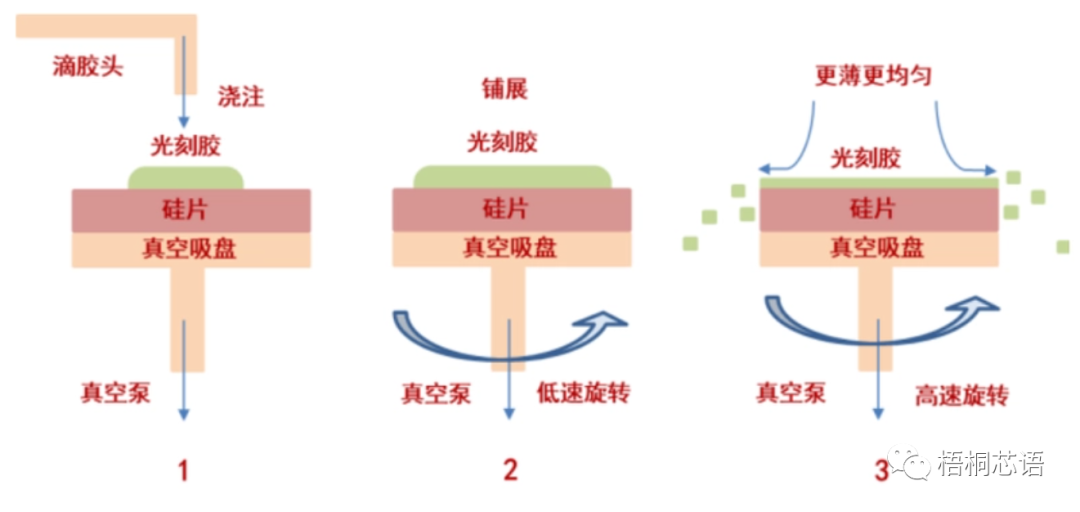

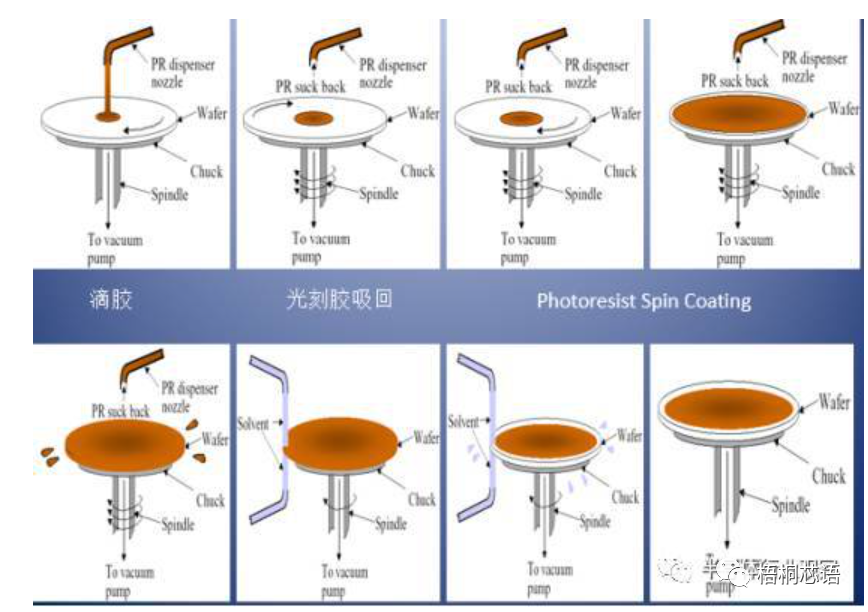

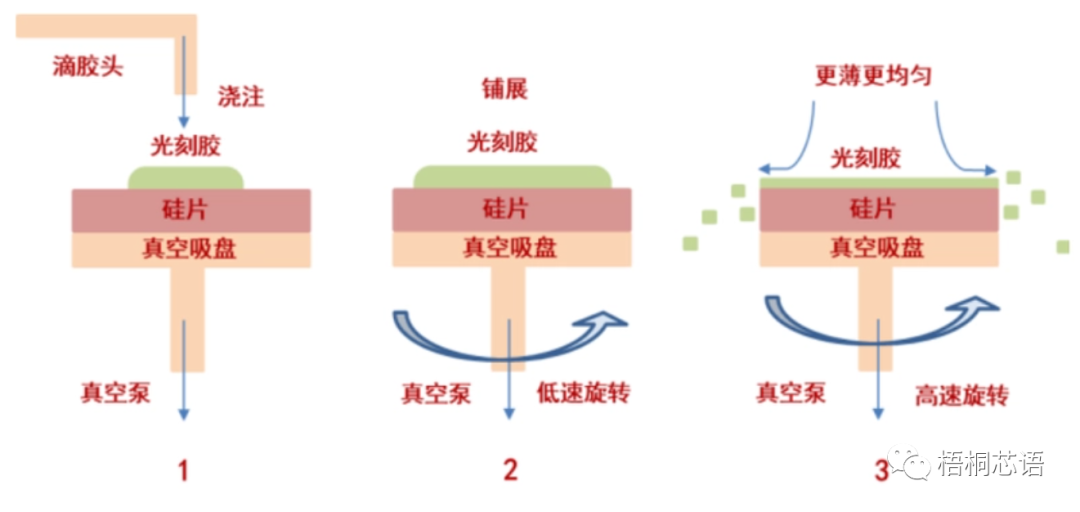

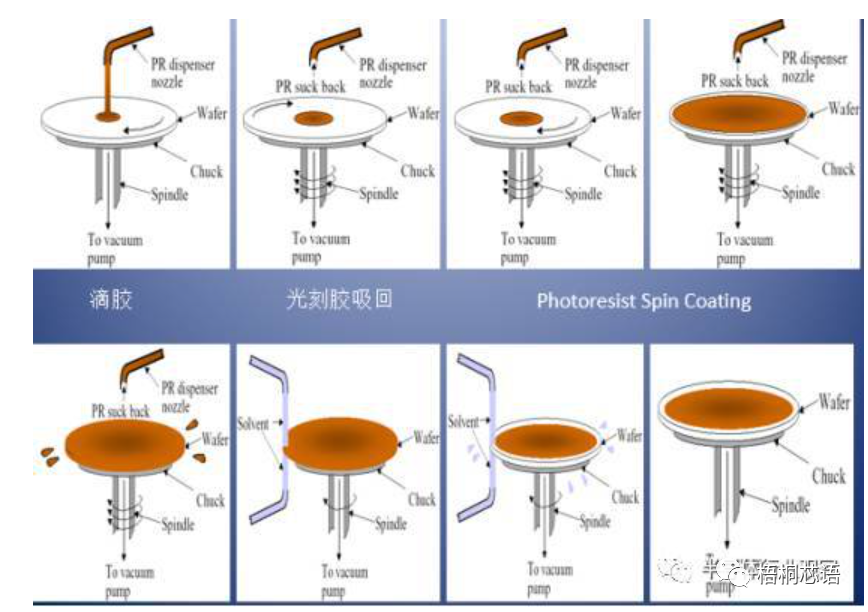

- 涂覆光刻胶:在表面旋转涂覆一层薄光刻胶膜(光刻胶液体滴在硅片中心,通过旋转使得光刻胶均匀的铺在晶圆之上)

在这之后,晶圆上就均匀地覆盖了一层光刻胶。以晶圆第一层光刻工作为例,在SiO2层之上,均匀地覆盖了一层光刻胶。

- 前烘:完成光刻胶的涂抹之后,需要进行软烘干操作,这一步骤也被称为前烘。前烘能够蒸发光刻胶中的溶剂溶剂、能使涂覆的光刻胶更薄。

- 对准:光刻对准技术是曝光前一个重要步骤作为光刻的三大核心技术之一,一般要求对准精度为最细线宽尺寸的 1/7---1/10。随着光刻分辨力的提高 ,对准精度要求也越来越高 ,例如针对 45am线宽尺寸 ,对准精度要求在5am 左右。

- 曝光:使用特定波长的光对覆盖衬底的光刻胶进行选择性地照射。光刻胶中的感光剂会发生光化学反应,从而使正光刻胶被照射区域(感光区域)、负光刻胶未被照射的区域(非感光区)化学成分发生变化。这些化学成分发生变化的区域,在下一步的能够溶解于特定的显影液中。

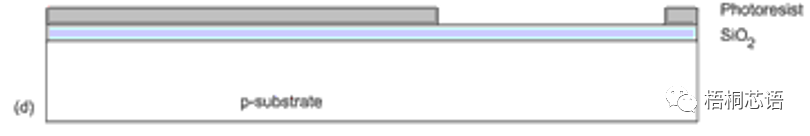

- 显影:去除未聚合的光刻胶。通过在曝光过程结束后加入显影液,正光刻胶的感光区、负光刻胶的非感光区,会溶解于显影液中。这一步完成后,光刻胶层中的图形就可以显现出来。为了提高分辨率,几乎每一种光刻胶都有专门的显影液,以保证高质量的显影效果:(以晶圆第一层光刻工作为例)

- 坚膜:增加光刻胶溶剂挥发。刻胶显影完成后,图形就基本确定,不过还需要使光刻胶的性质更为稳定。硬烘干可以达到这个目的,这一步骤也被称为坚膜。

- 显影检查:检查表面的对准和缺陷

- 刻蚀:穿过光刻胶膜的开口,去除晶圆顶层薄膜。

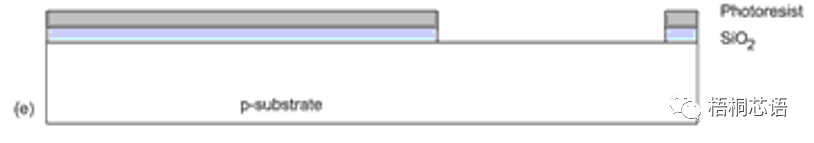

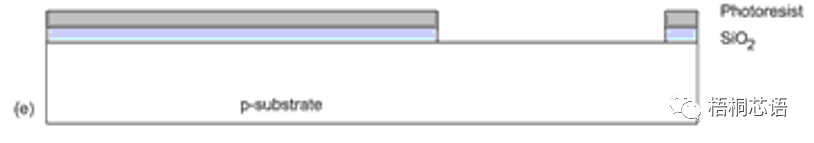

如下以晶圆第一层光刻工作为例,暴露出来的SiO2层,通过刻蚀的方式就被去除掉了。

- 去除光刻胶(剥离):从晶圆上去除光刻胶膜。如下以晶圆第一层光刻工作为例,去掉光刻胶膜后,SiO2层所展示的图形,就与n-well的MASK图形一致了。

- 最终检查:对刻蚀的不规则性和其他问题进行表面检查

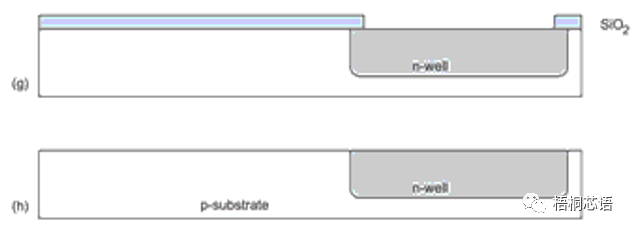

光刻完成后,我们看到光刻胶无法覆盖的区域,表面裸露在外面,在这个裸露的区域,有2种制造工艺。

向上生长,是利用外延、氧化、蒸发、溅射等方式,在裸露区域的上方逐步增加出一块材料。

而向内生长,则是在裸露的区域通过液体扩散,或离子注入的方式在裸露区域内部实现材料的晶体结构改变。

以晶圆第一层光刻工作为例,此时通过离子注入的方式,在SiO2无法覆盖的部分实现n-well,并移除SiO2,并重新做表面氧化即可进入下一层MASK的光刻工作。

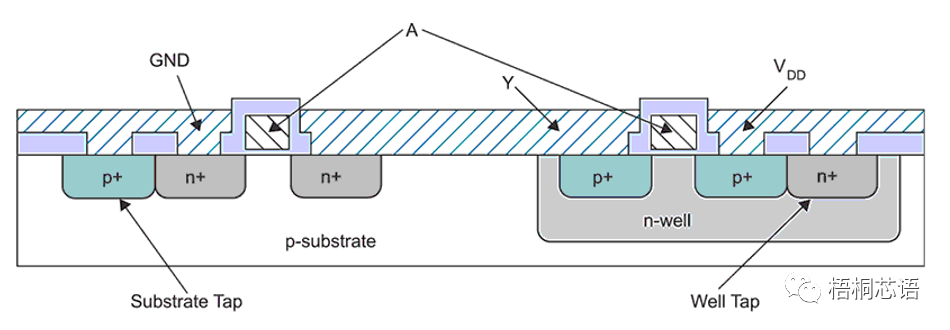

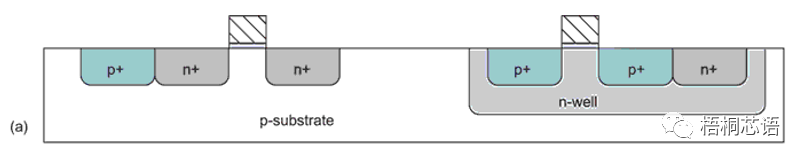

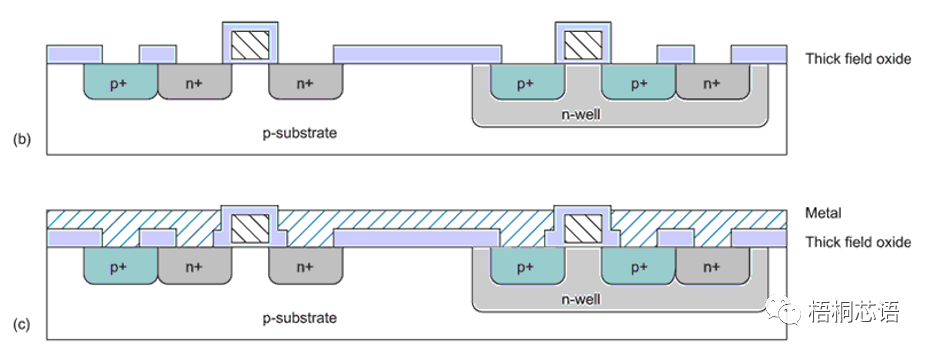

实现一个CMOS反相器

可以看到每一层光刻所需要的步骤是很复杂而且精密的,如果实现一个CMOS反相器电路,那么需要怎么做呢?

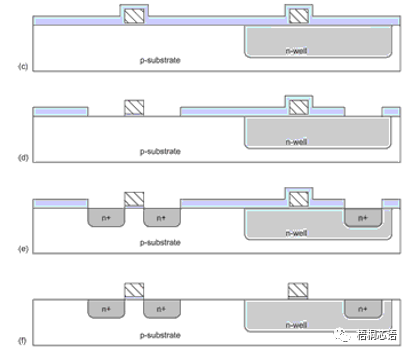

其实第一层n-well的mask图形刻蚀以及离子注入刚才已经说了,连贯起来就是:

接下来是gate poly的生长(这里不是向内生长,而是向上生长),需要注意的是thin gate oxide层需要在干燥环境里做氧化(干氧化),速度慢,但是精度好把控。

接着是n+的注入(向内生长),在这之前需要先在表面进行SiO2氧化,这个可以采用湿氧化,在潮湿的环境中实现,精度不高,但速度快。

下面通过注入的方式,实现p+图形。

最后实现metal 1的向上生长。

以上看来,如果希望简单实现一个CMOS反相器,则需要至少5层MASK(不包含电路连接)。如果2天做3层光刻,则这个电路需要大约4天时间。

不止CMOS

我们常常听到的都是CMOS集成电路,C是互补的意思(Complementary)。其实CMOS不是全部。

因为电子管的发展延续,实际上我们最早理解的开关过程,是通过PN节开始的。而从电子管向晶体管发展,首先出现的是1947年,威廉·肖克利,(William Shockley)利用锗元素,实现的第一个双极性节晶体管(PN节),代表器件包括TTL和ECL等。

1959年贝尔实验室研制金属半导体场效应管(MOSFET),并于1960年发布。在20世纪70年代,电路比较简单,往往都只是纯粹的PMOS器件电路,或NMOS器件电路。但随着生产工艺的提高,利用PMOS和NMOS器件分别在正压差和负压差表现的互补性,20世纪80年代后,互补性金属氧化物电路结构开始盛行,也就是我们所说的CMOS电路。因此CMOS不是器件类型,而是电路结构。

而从生产工艺来说,也有从P阱工艺,到N阱工艺,再到双阱工艺,接着是三阱工艺,等等的发展,以至于我们可以一次又一次的减小器件尺寸,提高电路稳定性,增加芯片性能的可能。

精度的累计

由于一般的芯片,MASK层数都会在十几层以上,多的可以到40多层,生产周期不说,成本不计,如果生产时每一层的精度都有1%的误差,则整个芯片生产出来后就完全不能工作了。

现在的工艺尺寸已经达到5nm以下(金属宽度预计3nm以下),国内也基本能够实现22nm的量产了。再往下,几乎就是对着一个原子大小进行设计和生产了。试想如果发生地震(就算非常轻微的),或者人走过来,我们能不能保证这一个原子跟目标原子的排布与我们的预期一致?

因此,集成电路生产制造工艺是一种非常精密的制造产业,牵扯到光学、化学、物理、机械、工程、电子、数学等大量基础学科的高精尖产业人才培养和积累。作为国内的集成电路设计半导体产业从业者,我们应该知道路还很长,我们还有差距,但未来仍然是光明的,我们仍然需要努力前行。

-

半导体

+关注

关注

336文章

29977浏览量

258086 -

驱动芯片

+关注

关注

13文章

1550浏览量

57655 -

CMOS反相器

+关注

关注

0文章

19浏览量

7182 -

GaN器件

+关注

关注

1文章

50浏览量

8188 -

NMOS管

+关注

关注

2文章

124浏览量

6255

发布评论请先 登录

毕业研究生继续送资料—微电子学概论、半导体集成电路等

【招聘】集成电路IC设计——摩尔精英

射频集成电路半导体和CAD技术讨论

芯片,集成电路,半导体含义

芯片,半导体,集成电路,傻傻分不清楚?

集成电路与半导体

一文让你读懂半导体、微电子和集成电路

半导体,微电子,集成电路都是什么关系?

半导体,微电子,集成电路都是什么关系?

评论