这篇博客展示了在 AMD Zynq 设计中,如何用 Vitis Vision Library 中的函数(remap)导出一个 IP,并基于此 IP 构建一个的硬件平台(XSA),进而基于此平台来运行嵌入式应用。

remap 函数是指从图像的某个位置获取像素信息,并将这些像素信息重新放置到另一个图像的另一个位置。在此示例中,设计将使用 128x128 像素的灰度输入图像,然后在输出端将其水平翻转。

测试采用以下设置:

版本: Vivado 和 Vitis 2023.1

操作系统:Ubuntu 20.04.1 LTS

硬件:Zynq UltraScale+ ZCU104 评估板 (xczu7ev-ffvc1156-2-e)

1. 创建 Vitis HLS IP 项目

在本节中,我们将利用 Vitis Vision L1 库提供的预先存在的 Makefile 来创建和导出 remap 函数,以便在 Vivado 项目中使用。

打开终端选择一个适合的路径位置,并将最新的 Vitis 库克隆到该位置:

git clone https://github.com/Xilinx/Vitis_Libraries

跳转至 Vision L1 中名为 remap 的函数的目录下:

cd Vitis_Libraries/vision/L1/examples/remap

注:专门就 Vision 库而言,需要 OpenCV 库才能编译函数。请使用下面链接中的指令编译 OpenCV,并在运行下一步之前设置所需的环境变量。

https://support.xilinx.com/s/article/Vitis-Libraries-Compiling-and-Insta...

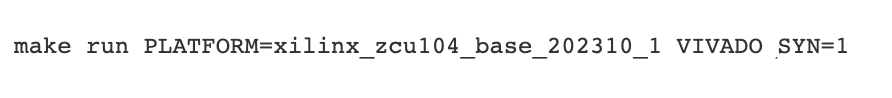

设置 Vitis/Vivado 工具,然后运行 HLS 项目脚本来构建 HLS 设计,并用该设计将函数作为 Vivado IP 导出。

PLATFORM——这是评估板平台名称,通常可以通过 PLATFORM_REPO_PATHS 环境变量或在 /base_platforms 中的 Vitis 安装目录内找到该名称。

VIVADO_SYN——此参数通过 export_design 流程运行 Vitis HLS 项目,该流程提供项目的压缩文件作为 Vivado IP。

您还可以打开 Vitis HLS 项目,通过命令 vitis_hls -p remap.prj 查看结果和报告。

注:由于此 Vitis HLS 项目来自 Makefile,其并不包括在 GUI 环境下直接重新运行 C Simulation 或 Cosimulation 所需的标志和参数。您可以检查 remap 文件夹中的 run_hls.tcl 文件,以查看仿真所需要添加的必要标志和参数。

重新运行上述指令,添加适当的变量,以便从命令行运行仿真(例如:CSIM=1 和/或 COSIM=1)。

2. 创建 Vivado 平台项目

本节将展示如何使用上一节中创建的 Vitis HLS IP 来创建一个以 ZCU104 为目标器件的自定义平台。

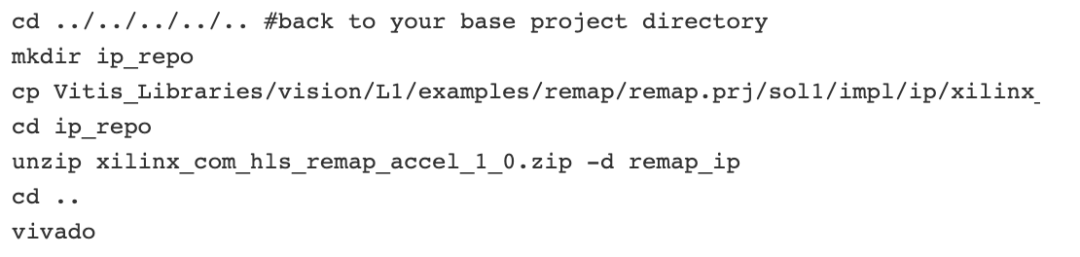

将上一节中创建的导出 IP 复制到它自己的存储库位置,然后打开 Vivado。

按照下列步骤创建项目并对其进行设置:

选择 Create Project,点击 Next:

输入项目名称:remap_vivado,点击 Next

选择 RTL 项目,此时不要指定源文件,点击 Next

在评估板选项卡,选择 Zynq UltraScale+ ZCU104 评估板,点击 Next,然后选择 Finish

打开项目后:

在左侧的流程导航器中选择 Project Manager > Settings

选择 IP > Repository,点击 + 并在此添加 ip_repo 文件夹的位置,然后关闭窗口

我们现在可以添加自定义 IP 及其余的模块:

在左侧的流程导航器中,选择 IP Integrator > Create Block Design

为原理图选择描述性名称,或保留其默认值,然后选择 OK

选择 +(添加 IP),并选择 Remap_accel 模块

选择 +(添加 IP),并选择 Zynq UltraScale+ MPSoC 模块

点击窗口顶部横幅上的 Run Block Automation。

确保勾选 Apply Board Preset,然后选择 OK

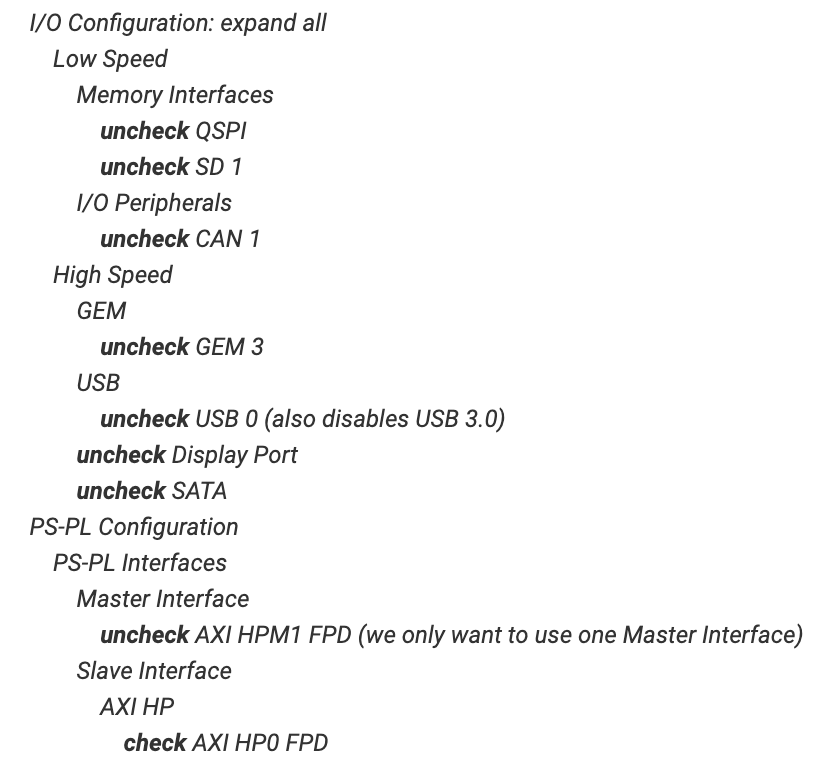

现在,我们将配置 MPSoC 模块,使其具有合适的接口,能够与 IP 进行通信:

双击图中的 MPSoC 模块,并做出以下修改。我们将关闭本设计中不会用到的一些功能。

更改这些设置后,选择 OK 将这些变更应用到 MPSoC 模块上。

我们现在可以使用连接自动化功能将这些模块彼此连接:

点击 Run Connection Automation

勾选全部自动化,然后选择 OK

点击 Run Connection Automation(第二次运行会把 IP 其它的 AXI 接口也链接起来,这些接口是IP互联接口的一部分)

勾选全部自动化,然后选择 OK

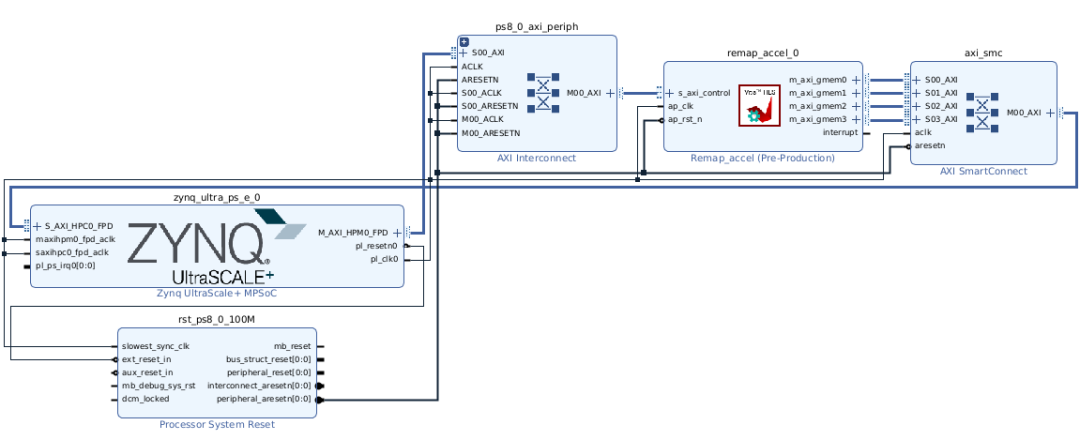

此刻的设计应类似于下图(您可以点击工具栏上的“Regenerate”,可自动对各个模块进行重新排列):

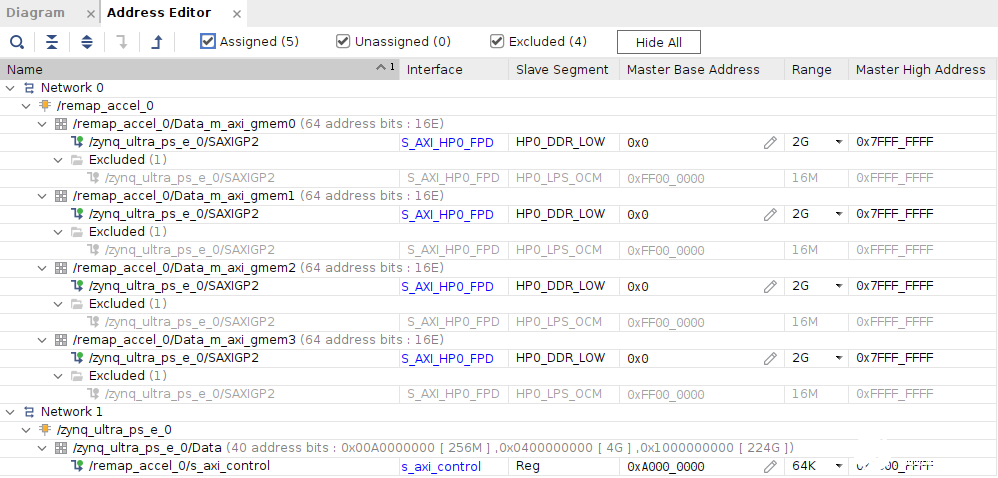

检查 Address Editor 选项卡。请注意,默认自动分配地址,AXI 和 IP 控件的地址空间设置为 0x0 和 0xA000_0000。

返回至图表选项卡,选择工具栏上的 Validate Design 按钮,或者在 Vivado 的主窗口中使用 Tools > Validate Design。确保设计无误。

在 Sources 窗口的 Sources 选项卡中,展开 Design Sources ,右键点击当前模块设计,选择 Create HDL Wrapper(选择 Let Vivado manage wrapper and auto-update),然后点击 OK。

在左侧的 Flow Navigator 中,选择 Generate Block Design,保留默认选项,然后点击 Generate。您可以在 Design Runs 选项卡中监视运行状态。

完成上述步骤后,点击 Generate Bitstream,选择 Yes/OK 来运行生成比特流的必要流程。完成创建后,您可以点击 Cancel 关闭打开的对话框,结束操作。

现在我们可以将硬件平台导出为 XSA 格式,以便 Vitis 与我们的应用一起使用。

在顶部工具栏中选择 File > Export > Export Hardware

选择 Next

选择 Include bitstream,点击 Next

设置 XSA 文件名:remap_platform,点击 Next,然后点击 Finish。输出的 XSA 文件默认保存在项目的根目录

3. 创建 Vitis 应用项目

现在我们已经从 Vivado 导出了一个平台 XSA,我们可以使用这个文件来定义我们的平台,并创建一个应用程序来在平台内通信和运行 IP。

打开 Vitis,然后导入 XSA:

vitis -workspace remap_ws

此操作会打开工作空间为 remap_ws 的 Vitis GUI。

创建应用项目

选择 Next

从顶部的选项卡中选择 Create a new platform from hardware (XSA),然后浏览上一节的 remap_platform.xsa 文件,接着选择 Next

设置应用项目名称:remap_project,选择将 psu_cortexa53_0 用作处理器,然后选择 Next

保留默认域信息(Standalone OS),然后选择 Next

选择“Empty Application (C)”模板,然后选择 Finish

本博文包括参考文件,可供下载(点击阅读全文查看参考文件)。可将这些文件解压到项目的根目录中。

在“Explorer”窗口展开 remap_project_system > remap_project > src,右键点击 src,选择 Import Sources,浏览保存参考文件的目录,选择并导入下列文件:

remap_example_app.c

remap_input_image.h

remap_x_map.h

remap_y_map.h

文件导入后,可随时检查 remap_example_app.c 文件,以查看应用正在执行的操作。总之,应用程序用 DDR 内存中的输入图像和映射数组数据配置 IP,并指示 IP 处理数据并将其写回 DDR 内存。

现在,我们可以构建平台并编译应用,以使其直接在 ZCU104 板上运行。

在助手窗口中:

选择 remap_platform [Platform],并使用 Build 按钮(锤子图标),等待 Build Finished 消息出现

选择 remap_project_system [System],并使用 Build 按钮(锤子图标),等待 Build Finished 消息出现

完成构建过程可能需要一些时间,时间长短取决于您的系统。

4. 在硬件上运行应用

现在,我们可以运行设计并验证 remap 函数的运行。

在助手窗口中,选择 remap_project_system [System],使用绿色运行图标,选择 Launch Hardware。

一旦完成设计运行,且硬件仍在运行时,选择 XSCT 窗口。如果窗口未打开,选择 Vitis > XSCT Console。

在控制台运行以下命令:

xsct% source remap_memory_copy.tcl

注:此脚本是参考文件的组成部分。您也可以指文件的完整路径,或使用“cd”跳转至适当的目录。

此脚本将读取内存中“input_buffer”和“output_buffer”的数据,并将数据分别保存为 input.data和 output.data。在继续操作之前等待完成消息。

在创建完 input.data 文件和 output.data 文件后,您现在可以通过运行 Python 脚本来验证 remap 函数是否已成功执行图像的水平翻转。运行下列 Python 脚本:

python3 remap_convert_image.py

注:运行此脚本需要安装“numpy”和“Pillow” Python 包,通常使用“pip install numpy”和“pip install Pillow”命令来安装这些包。

此脚本将输出两种文件,一个是 input.png,另一个是 output.png,表示发送到硬件的输入图像,以及通过 IP 传递后的输出图像。

责任编辑:彭菁

-

函数

+关注

关注

3文章

4422浏览量

67859 -

Zynq

+关注

关注

10文章

633浏览量

49581

发布评论请先 登录

请问TMS320F2809中的L0/L1/H0 SARAM双重映射数据段和程序段的地址空间能重合吗?

STM32重映射是什么意思

基于映射函数收缩算法的图像去噪方法

利用Vitis HLS tcl shell一键跑通视觉加速例程

华大HC32L110 printf重映射UART

STM32 部分重映射和完全重映射

STM32库函数关于CAN1通讯重映射发生错误问题

视觉L1重映射函数Zynq baremetal设计实例

视觉L1重映射函数Zynq baremetal设计实例

Vitis 库流程:视觉 L1 重映射函数 Zynq baremetal 设计实例

Vitis 库流程:视觉 L1 重映射函数 Zynq baremetal 设计实例

评论