RISC-V、ARM 和x86微处理器之间的许多差异都很细微,并且与内存寻址方式、分支执行方式、异常处理方式等有关。本文将考虑更高层次的差异,并将简要比较精简指令集计算(RISC)和复杂指令集计算(CISC),考虑这些差异对功耗和计算性能之间的权衡的影响,看看安全性和预测性如何执行被处理,虚拟化是如何实现的,最后是对RISC-V、ARM 和 x86 设备的应用程序适用性的概述。

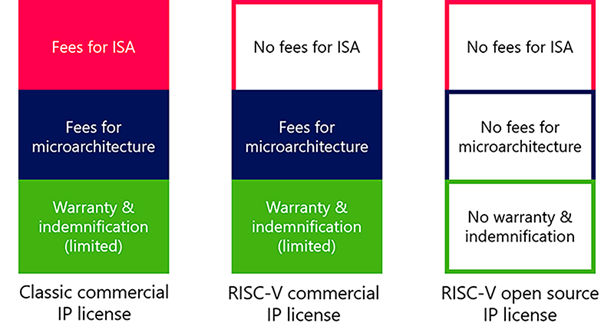

Intel的x86架构也在AMD的CPU上提供,ARM处理器和IP由ArmLimited提供,RISC-V国际组织正在开发RISC-V。英特尔、AMD、ARM 和 RISC-V之间的两个非常显着的区别在于商业模式和计算架构。英特尔、AMD 和 ARM 基于专有 IP,并且这些公司销售和/或许可他们的产品。RISC-V是一个开放的规范和平台;它不是开源处理器。可以使用开源 RISC-V 内核,但也有商业许可的内核。

RISC-V和ARM处理器在计算架构上基于RISC概念,而Intel和AMD的x86处理器则采用CISC设计。

一、RISC与CISC的计算

RISC体系结构具有可以在单个计算机时钟周期内执行的简单指令。因此,完成一项特定任务往往需要执行多条指令。同样的任务可以在CISC处理器上用更少的指令(甚至单个指令)完成。

CISC计算力求用尽可能少的代码行完成一项任务。一条CISC指令可能需要多个计算机时钟周期才能完成。例如,CISC处理器的两个数相乘可以用一条指令完成:

MUL 1200, 1201

“MUL”是一个复杂的指令。它不需要程序员显式使用任何调用、加载或存储函数。它直接在计算机的内存上运行,类似于高级编程语言中的命令。RISC

处理器上的乘法不能用单个命令完成;需要几个更简单的指令来从内存中的特定位置加载每个操作数(下面示例中的 1200 和

1201),将数字相乘,然后存储结果:

Load A, 1200

Load B, 1201

MUL A, B

Store 1200, A

在此示例中,Load指令将来自内存位置1200和1201的数据分别存储到寄存器A和B。MUL指令将两个寄存器中的值相乘。它将结果保存在A中,Store指令将 A 的值存储在内存位置1200(或任何其他指定的内存位置)中。在RISC处理器中,诸如MUL之类的操作仅在寄存器上执行,而不是直接在内存上执行。虽然这增加了指令数,但它允许使用更简单的指令。

二、功率与性能

与CISC指令相比,执行更简单的 RISC 指令消耗的功率更少。CISC

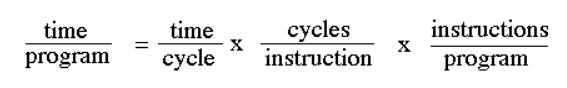

处理器试图以每条指令的计算机时钟周期数为代价来最小化每个程序的指令数。RISC采用相反的方法,使用可以在单个时钟周期内执行的简单指令,但需要更多的指令。以下等式显示了计算机的性能能力(运行程序的时间)与每条指令的周期数以及每条程序的指令数之间的关系:

从这个等式来看,有两种方法可以提高性能,最小化每个程序的指令数或减少每个指令的周期数。一般而言,RISC方法在降低整体功耗方面更为成功,有时会以降低性能为代价。然而,分歧正在缩小。ARM添加了更复杂的指令来提高处理器性能(以更高的功耗为代价)。英特尔将其一些操作码分解为类似于RISC的微操作,以实现更低的功耗。

三、安全性

权限环(有时称为保护环)是为保护数据和功能免受故障、提高容错能力和提高安全性免受恶意操作而建立的分层域。环按照从最高特权或最受信任到最低特权或最不受信任的层次结构设置。零环通常是最高特权级别,直接与

CPU 内核和内存交互。

x86 架构包括四个级别的特权环。ARM v7 架构包括三个特权级别;应用程序、操作系统和管理程序。ARM 和 RISC-V都使用隔离机制的概念。ARM 采用基于硬件的安全性,其中域被硬编码到硬件中,而 RISC-V 使用软件定义的隔离域。

OP-TEE 是实现 ARM TrustZone 技术的开源可信执行环境 (TEE)。OP-TEE 已被移植到许多 ARM 设备和平台,包括 ARMv8。RISC-V MultiZone 安全软件模型很小,因此速度更快。RISC-V内置了多种安全机制,包括四级权限环、安全中断处理和独特的物理内存保护(PMP)机制。RISC-V 还提供了商用安全增强功能,包括加密库、信任根和多域

TEE。

RISC-V 的开源特性导致专有 ISA 缺乏的透明度,并为另一个级别的安全性提供了可能性。RISC-V社区庞大而多样,许多设计人员不断研究安全环境和潜在威胁向量。一旦识别出安全风险,它通常会与开放社区共享,使专家能够快速开发或提出解决方案。

四、预测执行

谓词执行允许某些指令仅在特定的先前条件为真时才执行。例如,先前的结果必须大于零;否则,处理器继续执行下一条指令。ARM 和 x86

支持各种格式的谓词执行。

宏操作融合是一种硬件优化技术,在解码之前或解码过程中,将一系列相邻的宏操作合并为一个宏操作。ARM在其最近的微体系结构中支持许多宏操作融合操作。微操作融合在处理器内部将两条指令合二为一,有效实现无需指令集帮助的谓词执行。

基本的RISC-V指令集不支持谓词执行。然而,实验性的BOOMv3乱序推测RISC-V处理器使用精简指令集与微操作融合的组合来实现预测执行。

五、CPU、内存和I/O的虚拟化

ARM、x86 和 RISC-V 都支持 CPU 和内存的虚拟化。RISC-V ISA 目前不支持 I/O 的虚拟化。在 x86生态系统中,Intel和AMD有自己的虚拟化方法。英特尔被称为虚拟化技术或 VT。VT由 VT-x组成,包含核心侧特征;VT-d,包含输入输出内存管理单元(IOMMU);和 VT-c,它涵盖了网络接口。AMD在标签AMD-V下提供核心端虚拟化,而IOMMU称为AMD-Vi。英特尔和 AMD 的产品在实现细节上有所不同,但与 ARM

的产品相比,彼此的架构更加紧密。

与 x86 处理器采用的方法类似的虚拟化扩展已添加到ARM架构中。ARM虚拟化扩展使硬件方式能够使用管理程序虚拟化 CPU。多个操作系统可以在每个虚拟

CPU 上运行。

RISC-V H(管理程序)扩展 v0.6.1 引入了 CPU 状态的完整副本:一份副本用于来宾,一份副本用于主机(类似于 IntelVT-x)。RISC-V通过将敏感寄存器和指令赋予主机模式特权来支持 CPU 的虚拟化。从预发布版本号可以看出,RISC-V虚拟化是一项正在进行的工作。最近发布了用于嵌入式系统的 Rocket 芯片内核中最新版本的 RISC-V 虚拟机管理程序扩展的首次公开实施和评估。

与x86和ARM架构一样,RISC-V支持使用多阶段页表的内存虚拟化。此外,RISC-V为来宾表和主机表实现了相同的页表条目格式。

I/O虚拟化在RISC-V中留待指定。它主要是IOMMU和平台级中断控制器(PLIC)的一个特性,它位于RISC-VISA的域之外,需要指定。当前指定的 PLIC 不包括用于配置中断注入的寄存器。

六、RISC-V和ISA的扩展

RISC-V

从一开始就设计为不仅支持基本ISA和标准扩展,而且还支持自定义ISA扩展。虽然ARM最初并未设计为使用自定义扩展,但这种情况正在发生变化,并且ARM生态系统开始使用自定义扩展。x86生态系统是封闭的,一般不支持自定义ISA扩展。

RISC-V ISA被组织成指令组(基本 ISA 和标准扩展)。使用对标准ISA的扩展的能力可以为特定应用程序提供支持。例如,最近发布的 RISC-V向量扩展(RVV)使基于RISC-VISA的处理器内核能够与传统标量运算一起处理数据数组,以加速大型数据集上单指令流的计算。适合矢量处理器的任务示例包括:

(1)机器学习。

(2)压缩图像、zip文件等。

(3)密码学。

(4)多媒体:音频、视频。

(5)语音和手写。

(6)奇偶校验、校验和。

(7)散列/连接。

RISC-V

ISA支持自定义扩展的能力可以成为特定用例或应用程序的关键区别。使用自定义扩展不会破坏与主要ISA的合规性。支持自定义扩展的处理器也可以运行通用 RISC-V

软件。

上图显示了RISC-V软件堆栈中的自定义ISA扩展。操作系统(OS)可以是实时操作系统(如embOS、FreeRTOS、LynxOS等),也可以是富操作系统(如Linux、Android、Windows等)。在此示例中,App1

确实需要性能增强并且不使用自定义 ISA 扩展。它可以符合标准编译器。App2 和 App3 使用自定义 ISA 扩展来提高性能,并且必须使用包含自定义 ISA

扩展的编译器进行编译。

所以,x86、ARM和RISC-V微处理器之间的差异很多而且各不相同。这些差异推动了一般应用程序的适用性。来自AMD和Intel的x86处理器在计算机和服务器领域占据主导地位。在平板电脑和智能手机上,苹果和高通的ARM处理器占主导地位。ARM处理器在嵌入式应用中也很强大。随着

-

ARM

+关注

关注

135文章

9596浏览量

393844 -

微处理器

+关注

关注

11文章

2440浏览量

86187 -

X86

+关注

关注

5文章

300浏览量

45590 -

RISC-V

+关注

关注

49文章

2957浏览量

53609

发布评论请先 登录

RISC-V、ARM与x86微处理器之间有什么区别?

RISC-V、ARM与x86微处理器之间有什么区别?

评论