在后仿真过程中经常会遇到关于setup和hold violation的问题,但是关于setup和hold time的产生原因和由来很多人还比较朦胧,为此本文通过解剖一个边沿触发器简要说明setup和hold产生原因。

解剖示例

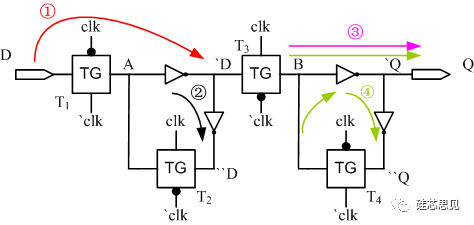

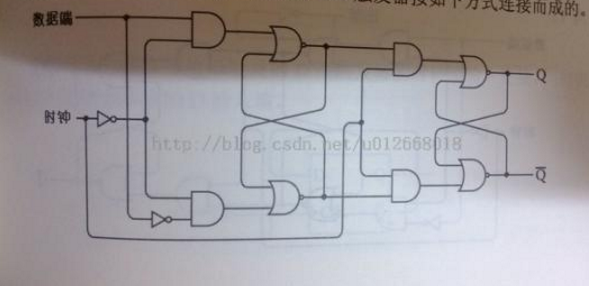

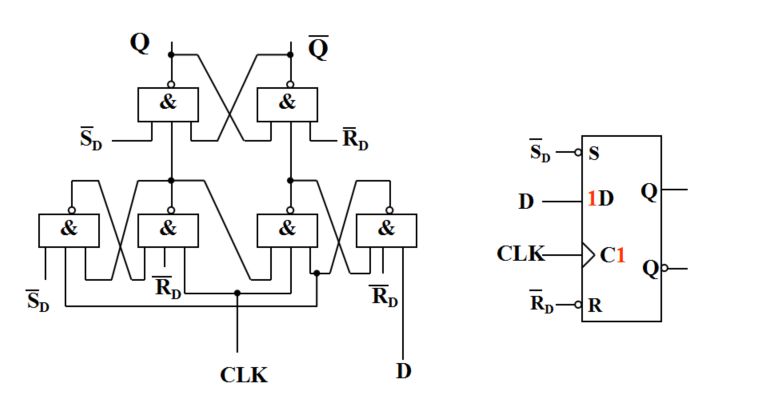

上图为触发器的简要示意图(clk和’clk为反向时钟)。T1和T4同时导通,T2和T3同时导通,且T1、T4和T2、T3导通状况互反。其中T1、T2、T3、T4均为传输门,均为电平敏感,所以所谓的时钟跳变可以理解为高低电平的相互跳变所致。而电路中实际的延时信息主要由于电信号导通时通过电子器件时耗费的时间。

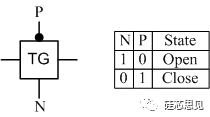

【注】传输门的开关状态如下图所示。

工作过程

clk和’clk互为相反的信号,clk为低电平(’clk为高电平)时,T1和T4导通,此时数据进入到`D和``D,因为此时T4导通,图中绿色箭头线中的数据保持上一拍的数据结果。 当clk高电平(’clk为低电平)到来时,T1和T4关断,T2和T3导通,②中的数据维持稳定,通过T3输出至Q端,同时B点、’Q和’’Q点的数据保持一致稳定;当低电平到来时,T2和T3关断,T1和T4导通,此时B点、’Q(Q)和’’Q点数据一直稳定,因此可以保证绿色箭头线部分有稳定一致的数据通过Q端发送出去。

所以,可以看到在上跳沿采样的数据可以保持一个时钟周期。通过上述分析,我们可以看到一个边沿触发器实际上可以解剖为两个锁存器,后续分析时也会用到这种结构特点。 一般触发器setup和hold的产生,就跟上述触发器的工作过程密切相关,下面一块来看看两者之间的联系。

setup和hold踪迹

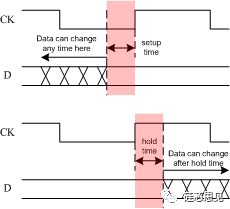

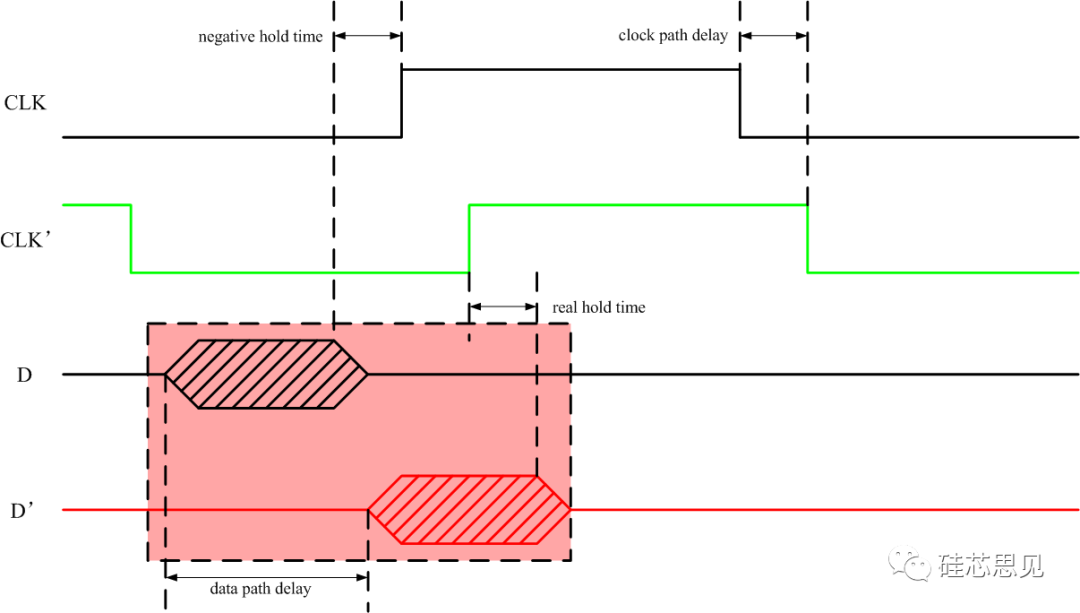

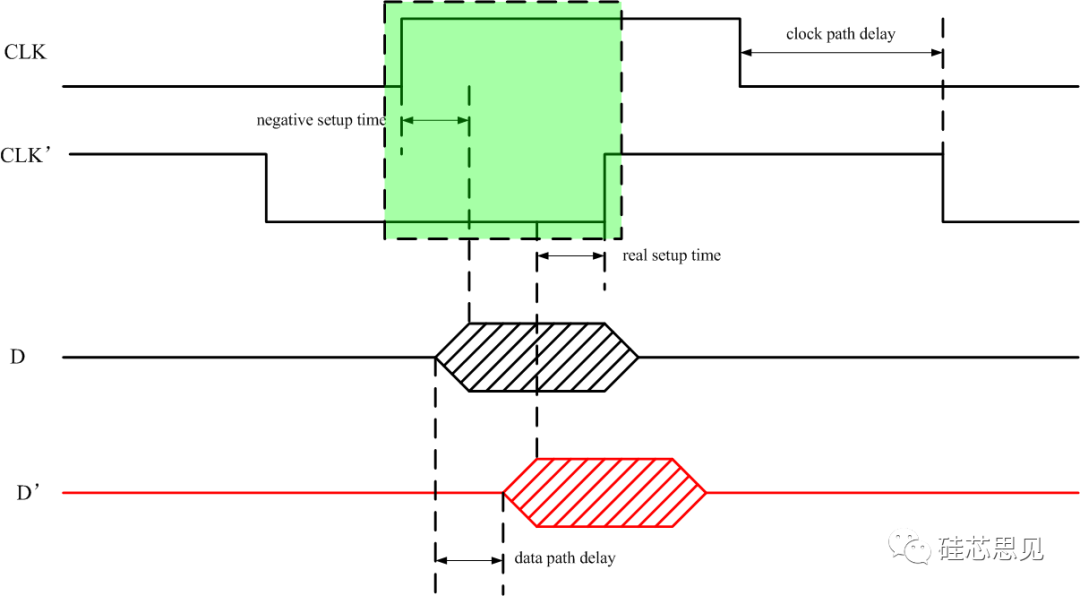

下图为阴影区域为timing violation区。

clk上跳沿之前

setup时间(tsu):输入数据D在时钟上升沿之前必须保持不变的时间。为了得到有效的数据,必须保证A点、`D和``D点的数据保持一致稳定,否则在T2导通时将会形成振荡电路。当T1打开时,输入信号经过T1后分别到达A点、`D和``D点,并且保持一致,耗费的时间为Ts,时钟从低电平跳变到高电平需要耗费时间为Tc,因此,为了保持数据的有效和电路的稳定,输入数据需要保持的时间至少应该为Ts,如果不满足将会在T2导通时,A点、`D和``D点的值不同,从而可能会产生亚稳态。因此,可以这样理解,所谓的建立时间是指输入数据D经过多长时间才能使`D的数据稳定可靠。所以setup指的是数据从D到达``D的时间。

clk上跳沿之后

hold时间(thold):在时钟上升沿到达后,输入数据需要保持稳定的时间。在clk上跳沿发生之后,T1和T4关闭,T2和T3打开,数据从Q端输出。但是需要注意,因为T1关闭需要时间,所以在T1和T4关闭到T2和T3打开输入数据必须保持稳定,如果A点的数据受到D点的影响,从而导致A点和D点数据不一致,也就是在上跳沿发生后,即T2、T3导通时,②中循环的数据不能保持稳定一致,从而导致Q端数据不稳定。因此,thold可以理解为D端数据通过T1,再经过②到达A点,保证A和`D点数据一致稳定的时间。 上面是对setup和hold产生原因的一些简单介绍,有些朋友可能会问,上文中setup和hold感觉都是正值,为什么我在仿真的时候遇到过setup或者hold为负值的情况呢?为了探讨方便,此处以常用到的一种触发器(由两个锁存器组成)为例进行简单的说明。

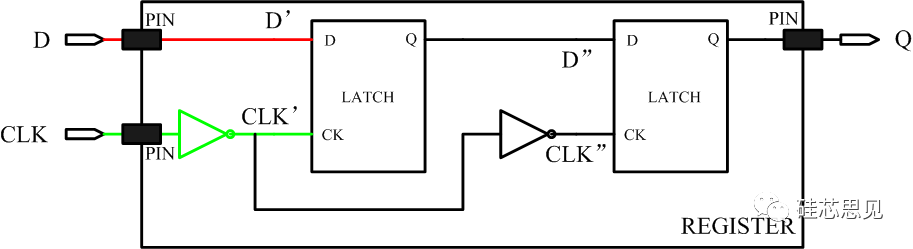

hold time为负值

当data从pin到锁存数据的锁存器的delay时间大于clock从pin到达锁存器CK端的delay时,那么当D结束于CLK上升沿之前,此时从REGISTER层面观测到的hold为负值,而实际上在锁存数据的锁存器端,由于之前data延迟大于clock延迟,CLK'对D'进行控制时,D'相对于CLK'一直保持到CLK'为高电平之后,也就是此时hold为正值,出现在上升沿右侧。

setup time为负值

当data从pin到锁存数据的锁存器的delay时间小于clock从pin到达锁存器CK端的delay时,那么当D开始于CLK上升沿之后,此时从REGISTER层面观测到的setup为负值,而实际上在锁存数据的锁存器端,由于之前data延迟小于clock延迟,CLK'对D'进行控制时,D'出现在了CLK'之前,也就是此时setup为正值,出现在上升沿左侧。

审核编辑:刘清

-

锁存器

+关注

关注

8文章

958浏览量

45475 -

触发器

+关注

关注

14文章

2065浏览量

63559 -

CLK

+关注

关注

0文章

132浏览量

18097 -

边沿触发器

+关注

关注

0文章

34浏览量

4346

原文标题:说说setup和hold violation

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

什么是Setup和Hold时间

CMOS触发器在CP边沿的工作特性研究

边沿触发SR触发器

什么是边沿触发器_边沿D触发器介绍

通过解剖一个边沿触发器简要说明setup和hold产生原因

通过解剖一个边沿触发器简要说明setup和hold产生原因

评论