今天我们要介绍的时序分析基本概念是 clock group,简称时钟组。 定义完时钟后,我们也需要通过设置clock group来确认各个时钟之间的关系。

工具不会对处于不同clock group的时钟检查时序。这是很重要的一步,因为通常我们还需要做cross domain check, 如果clock group设错了, 会导致整个STA检查错误。一般有三种类型的clock group属性选择:

asynchronous

physically_exclusive

logically_exclusive

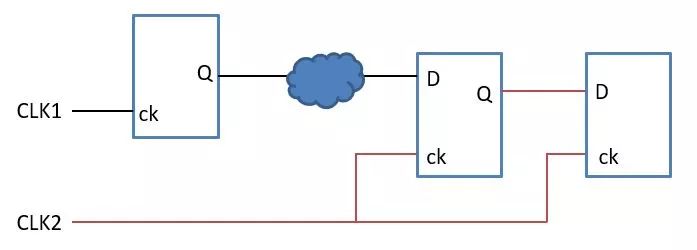

asynchronous代表两个异步的clock group,工具会做正常的SI分析。

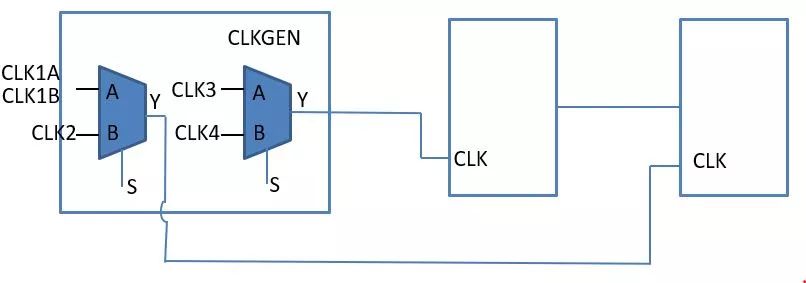

logically_exclusive代表两个clock group在逻辑上相互排斥,比如两个clock经过MUX选择器。工具分析SI时,采用 infinite window(信号全部翻转),而不是看具体的timing window,较为悲观。

physically_exclusive代表两个clock group在物理意义上相互排斥,比如在一个source pin上定义了两个时钟。这时候,工具会禁止分析SI。

一个简单的例子:

set_clock_group -name groupA -physically_exclusive \\

-group "CLK1A" -group "CLK1B"

set_clock_group -name groupB -logically_exclusive \\

-group "CLK1A CLK1B CLK3" -group "CLK2" -group "CLK4"

set_clock_group -name aysnc_group -asynchronous \\

-group CLK1 -group CLK2

-

时钟

+关注

关注

11文章

2005浏览量

135390 -

时序分析

+关注

关注

2文章

130浏览量

24290 -

Mux

+关注

关注

0文章

44浏览量

24230 -

选择器

+关注

关注

0文章

111浏览量

15173 -

CLK

+关注

关注

0文章

132浏览量

18117

发布评论请先 登录

电源管理之clock驱动构架设计解决方案

在PSoC4000的UART Bootloader中不能将引导加载程序时钟资源设置为extCLK吗?

如何让labvew编写的程序运行时,如何让各个vi都运行,各个vi之间不是子vi的关系,有数据传递的关系

请问ad9361各个时钟关系是什么?

过孔直径和线宽有什么关系?它们之间的关系是怎么设置的?

I / O和时钟区域之间是什么关系

输入时钟和采样率之间有什么关系?

STM32微控制器的时钟树和STM32CubeMX Clock Configuration的配置关系是什么?

Vivado时钟分组约束的三类应用

边缘计算与云计算之间是怎样的关系?

时钟子系统中clock驱动实例

怎样通过设置clock group来确认各个时钟之间的关系?

怎样通过设置clock group来确认各个时钟之间的关系?

评论