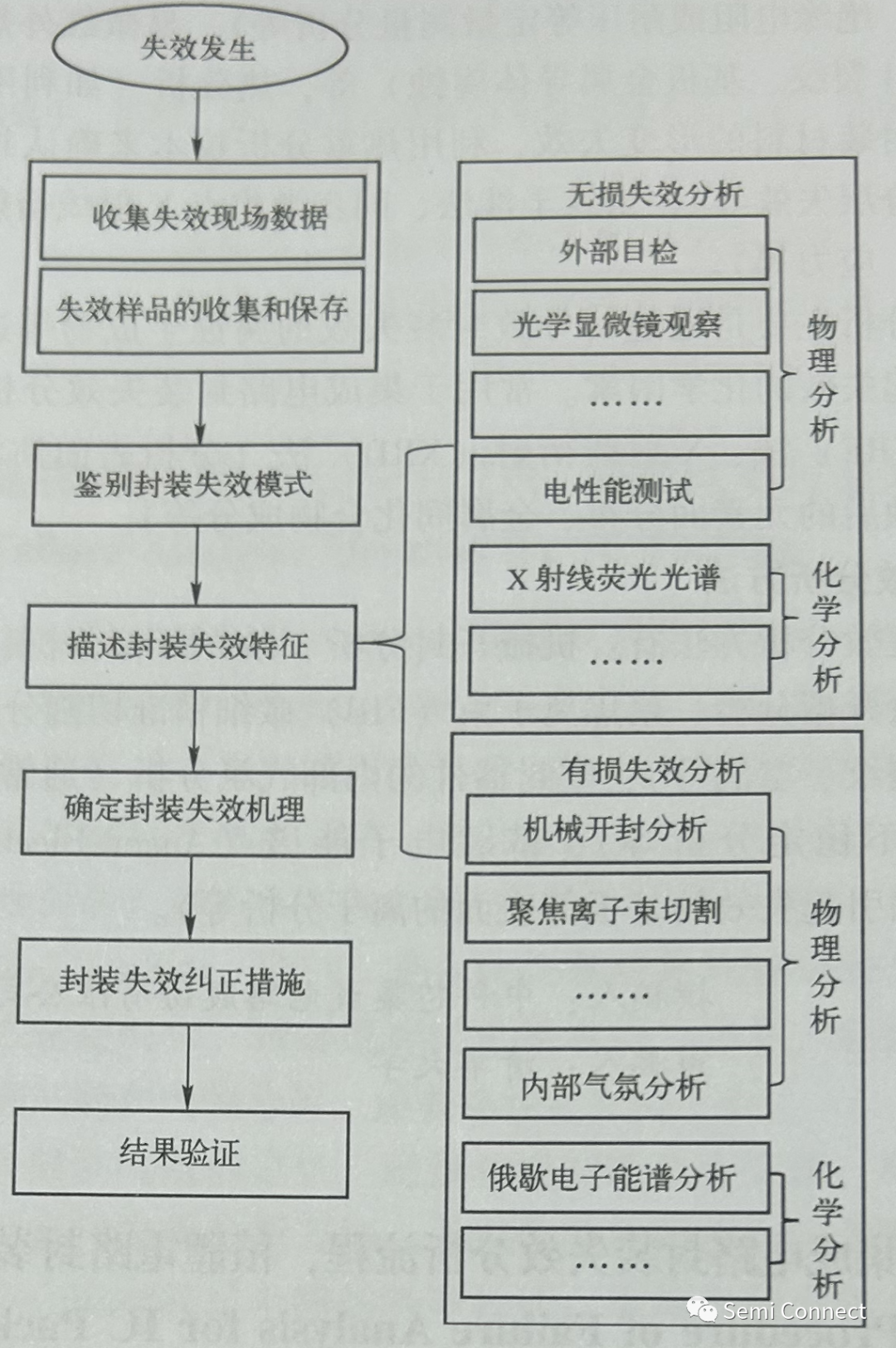

集成电路封装失效机理是指与集成电路封装相关的,导致失效发生的电学、温度、机械、气候环境和辐射等各类应力因素及其相互作用过程。根据应力条件的不同,可将失效机理划分为电应力失效机理、温度-机械应力失效机理、气候环境应力失效机理和辐射应力失效机理等几大类。

1. 电应力失效机理

电应力失效包括封装中的静电放电,集成电路中存在n-p-n-p结构而形成正反馈(月锁效应) 或钝化层介质受潮/污染/损伤 (白道击穿)等过电应力损伤导致内引线熔断,外引出端之间漏电引起参数漂移甚至短路、烧毁开路等功能失效。

当部分金属外壳封装的器件外引脚表面为镇银层或采用银丝作为键合丝时,在水汽、电场的作用下,Ag电离产生 Ag'树枝状迁移,从而导致短路失效的发生。

2.温度-机械应力失效机理

温度-机械应力失效主要包括如下9种情形。

(1) 空腔结构密封过程中挤人内腔的焊料,镀层或封口熔融材料脱落,划槽中工艺控制监测因形 (Process Control Monitor, PCM)剥落等形成腔内多余物,均会引起短路或偶发短路失效。

(2) Au-A1 键合点在高温条件下生成脆性、高阻性的 AuAl, “紫斑”失效和Au,AI “白斑” 失效山。

(3)封装内的芯片、键合引线、引线框架或基板、模塑料 等因热膨胀系数、弹性系数不一致,当温度发生变化时,材料涨缩产生内应力,引起键合引线拉脱拉断、芯片开裂,或者与基板分层失效131。

(4) 底部填料工艺中 Si0,颗粒填充不均匀,填充压力和固化温度不匹配引起填料分层,焊点底部开裂引起的失效,如图1所示;热膨胀系数失配和高温工艺(如回流焊)超过内凸点的熔点,引起凸点熔化产生的互连失效,如图2所示。

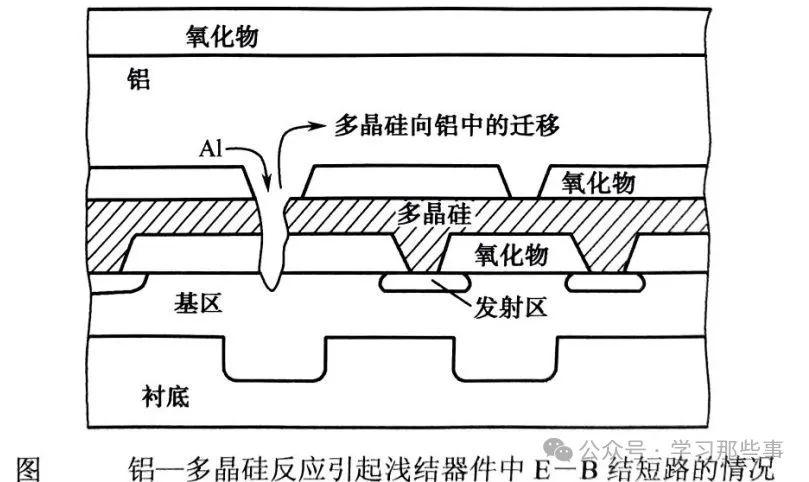

(5)倒装芯片焊接区的Au、Sn、Pb、Cu、 Ag 等焊料生成的金属问化合物(Intermetallic Compound. IMC) 在温度变化、加电发热或机械应力下,与基板焊盘和芯片间的热膨胀系数失配,IMC 龟裂引起焊点 “金脆”开裂失效;焊料焊接温度不匹配,引起焊点内部因各种焊料的相互扩散速率差异出现孔洞,从而破坏焊点的电气连接和机械性能四,如图所示。

(6)周期性温度变化下,2.5D、3D堆叠结构中 TSV 铜填充与硅孔壁、焊盘与焊球、堆叠裸芯片、堆叠封装等因热膨账系数失配产生应力而导致开裂、分层、翘曲失效。

(7)周期性温度变化或机械应力下,键合引线发生形变、碰丝、疲劳断裂,金属.玻璃或陶瓷,模塑料等材料发生蠕变 疲劳裂缝扩展、断裂和密封漏气等失效。

(8) 金属或钎焊材料中的氢向应力集中部位聚集、析出,与材料内部的残留应力及外部应力组合,产生巨大压力导致“氢脆” 断裂失效。

(9)含Sn 焊料、钎焊材料及含 Sn 镀层在过低温度下存储、工作时可导致粉末 Sn 的“锡瘟〞 失效;纯Sn 或 Sn 合金镀层封装因 Sn 层内应力、晶体位错、环境因素等发生 Sn 须生长引起相邻引脚之间的漏电、短路失效。

3. 气候环境应力失效机理

气候环境应力失效主要包括如下3种情形。

(1)模塑料、层压有机基板或底部填料吸湿后,在高温下水分迅速膨账,迫使其与其上附着的其他材料(如芯片、引线框架等)发生分离,引起芯片开裂、内焊接点接触不良或断裂、分层或爆裂失效。

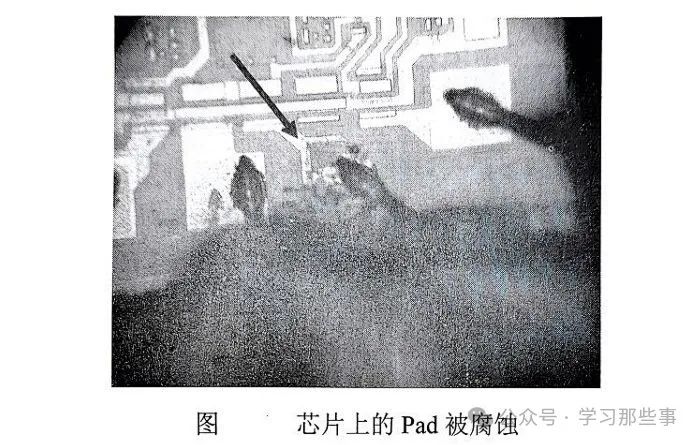

(2)外部离子和污染物、封装料中的杂质离子溶人水汽生成电解液,在内键合引线或曝鐸的 A1 或 Au-AI 结合处发生长期、缓慢的化学腐蚀或电化学腐蚀.生成“白毛”状AI (OH)₃或腐蚀斑。

(3) Sn、Au、Ni 等保护镀层过薄、针孔密度过大或缺损,以及有Na、K、Cl等杂质离子污染存在,金属壳体、盖板和外引脚在水汽、电场作用下,产生电化学腐蚀引起漏电短路、掉脚等。

4.辐射应力失效机理

辐射应力失效是指,封装材料中含有的放射性元素裂变放射出a粒子后,其沿途产生的电子-空穴对在电场作用下,在芯片某些区域被集结,引起DRAM、SRAM 等存储单元中的电荷量发生改变,导致电路发生误翻转的a粒子软失效。

审核编辑:刘清

-

集成电路

+关注

关注

5446文章

12467浏览量

372687 -

PCM

+关注

关注

1文章

207浏览量

55395

发布评论请先 登录

AECQ100的失效机理——基于集成电路应力测试

关于封装的失效机理你知道多少?

集成电路是什么_集成电路封装_集成电路的主要原材料

集成电路封装失效的原因、分类和分析方法

集成电路失效分析

半导体集成电路封装失效机理详解

集成电路封装失效机理

集成电路封装失效机理

评论