Return Path (回流路径)

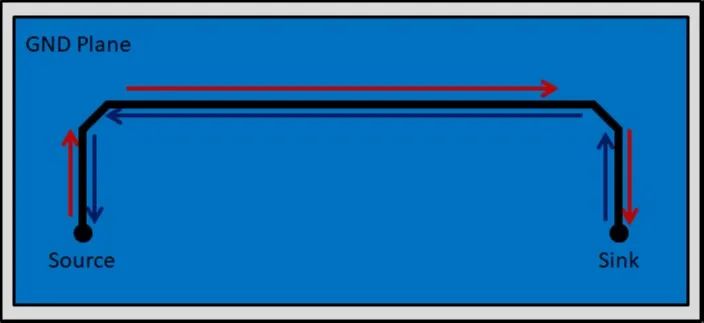

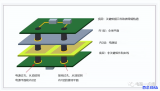

以高频信号而言, 回流(retrun path) 将沿低阻抗路径走, 所以差动信号线参考的是临近的单一Ground plane

如此可以减少差动阻抗的改变及降低EMI的问题

Single Reference Plane

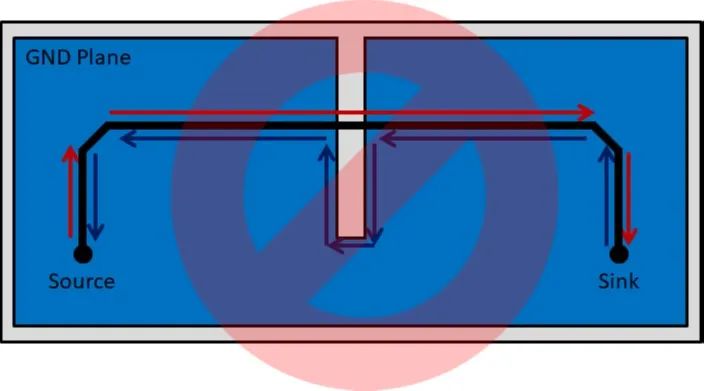

高速差动信号的走线需参考单一的Ground reference 而不是有断裂(Split)或是有捞空(Void) 的ground reference.

若Ground reference 是Split 或 Void 会造成下列问题:

Ø EMI ↟

Ø Signal propagation delay ↟

(Series Induction ↟)

ØSignal Integrity ↓(Jitter ↑, Signal Amplitude ↓)

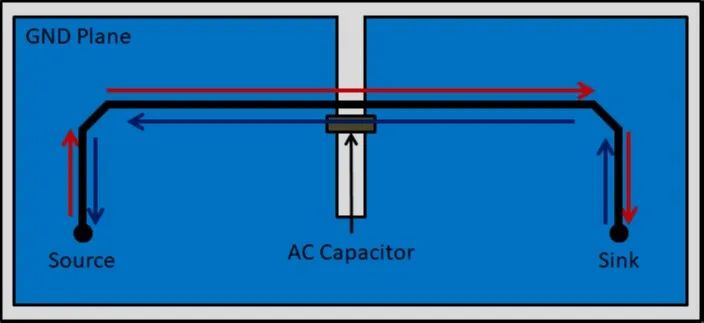

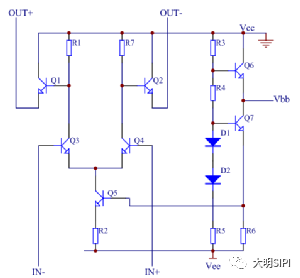

Single Reference Plane –Stitching Capacitor

假使Split-Ground reference 无法避免, 其唯一改善之道是在此split-Ground 加一颗 Stitching Capacitor (缝合电容) , 其目的缩短高速信号的return path.

Stitching Capacitor ≤ 1uF

-

usb

+关注

关注

59文章

7437浏览量

258234

发布评论请先 登录

相关推荐

高速ADC PCB布局布线技巧分享

PCB设计中的高速电路布局布线(上)

关于高速串行信号隔直电容的PCB设计注意点

一文搞定PCB元器件的布局布线

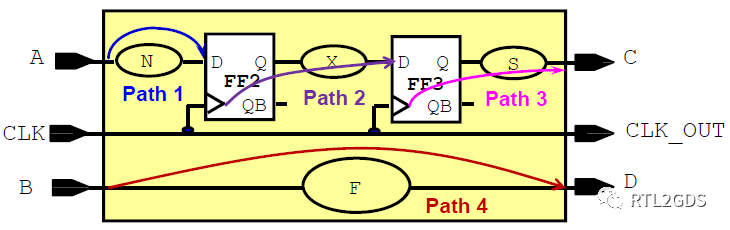

如何做一条合格的path?同一条path在物理设计不同阶段的变化

博文 | USB 4 高速信号布局关键因子 (一 ) : Return Path

博文 | USB 4 高速信号布局关键因子 (一 ) : Return Path

评论