滤波器是信号处理技术绕不过的内容,而在BSPK的实现框图中,也需要用到滤波器。

m序列的时域波形是一个矩形,矩形在频谱上是所有奇次谐波之和,为了节省带宽资源,这里需要使用FIR滤去谐波,留下基波。

本文会讲到Vivado 中FIR IP核的使用方法,会涉及到MATLAB的部分内容。

因为我们不使用太高级的功能,只使用最基础的功能,滤波。所以,最关键的内容就是coe参数文件的生成,可以使用MATLAB帮助我们生成这个文件。

在MATLAB的命令窗口,输入fdatool(新版MATLAB为filterDesigner)回车,

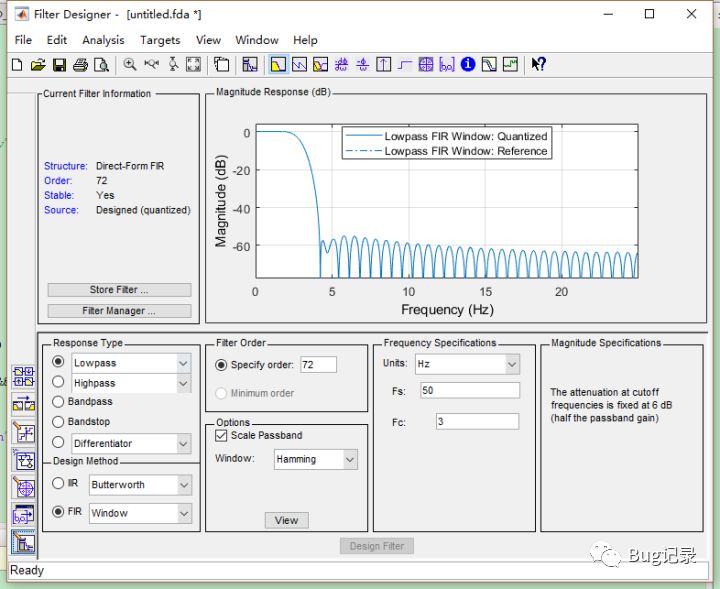

滤波器设置界面

这里选择低通FIR,窗函数选常用的几个,这里选择了汉明窗;滤波器阶数选择72,阶数越高滤波效果越好,但资源占用越多;FS/FC(采样率/截止频率)为50:3,点击Design Filter会显示相应的频率响应图,由于FIR滤波器抽头的特性,当输入的采样率为50M时,滤波器的截止频率为3M,两者之间保持比例关系。

滤波器数值表示

点击如上图红框内的图标,将Filter arithmetic修改为Fixed-point,将滤波器的参数数值表示修改为定点数表示,方便FPGA处理,也只有这样能生成coe文件。

滤波器生成coe文件

点击上图菜单栏的Target,然后生成coe文件。

在Vivado中IP Catalog中找到FIR IP核,

FIR IP核界面

在Filter Coefficient里面选择使用COE FILE,文件选择刚才生成的COE文件。

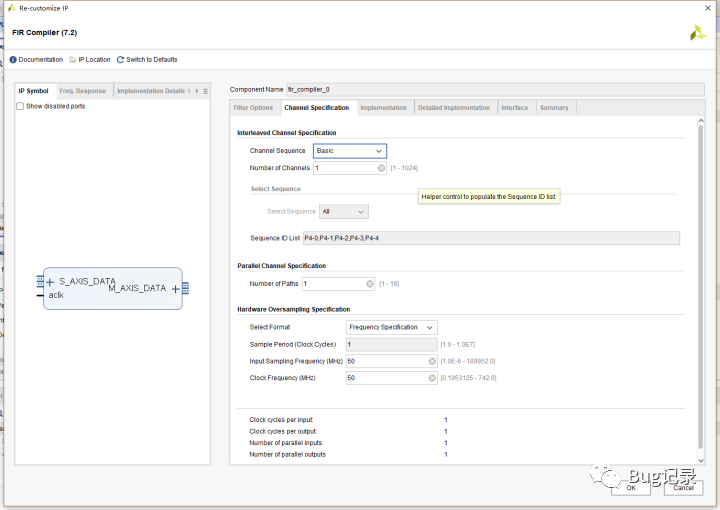

FIR IP核界面

在Channel Specification,设置输入的采样率为50M。

FIR IP核界面

Implementation里面,滤波器系数类型选择有符号型,输入数据也是有符号型,输入数据位宽选择2位,小数部分位数为0,GUI显示出输入数据位宽21位,这些数值后面有用。

一路默认,FIR IP核生成后,可以看到相关的端口定义。

fir_compiler_0 your_instance_name (

.aclk(aclk), // input wire aclk

.s_axis_data_tvalid(s_axis_data_tvalid), // input wire s_axis_data_tvalid

.s_axis_data_tready(s_axis_data_tready), // output wire s_axis_data_tready

.s_axis_data_tdata(s_axis_data_tdata), // input wire [7 : 0] s_axis_data_tdata

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata) // output wire [23 : 0] m_axis_data_tdata

);

可以看到,输入数据位宽为8位,而我们在FIR GUI界面设置的是2位,为了不影响最终的输入数据,需要对输入数据进行符号位扩展。

而输出数据位宽有24位,但是FIR GUI界面显示输出数据位宽为21位,这说明FIR的输出数据也进行了符号位扩展,这里可以截取符号位。

相关的符号位扩展和截取符号位可以见下代码块。

fir_compiler_0 fir_inst (

.aclk(clk_50m), // input wire aclk

.s_axis_data_tvalid(1'b1), // input wire s_axis_data_tvalid

.s_axis_data_tready(), // output wire s_axis_data_tready

.s_axis_data_tdata({{6{code_c[1]}},code_c}), // input wire [7 : 0] s_axis_data_tdata

.m_axis_data_tvalid(), // output wire m_axis_data_tvalid

.m_axis_data_tdata(fir_out) // output wire [23 : 0] m_axis_data_tdata 19-8

);

xbip_dsp48_macro_0 dsp_product_inst (

.CLK(clk_50m), // input wire CLK

.A(fir_out[19:8]), // input wire [11 : 0] A

.B(cos_o[13:2]), // input wire [11 : 0] B

.P(duc_data) // output wire [23 : 0] P

);

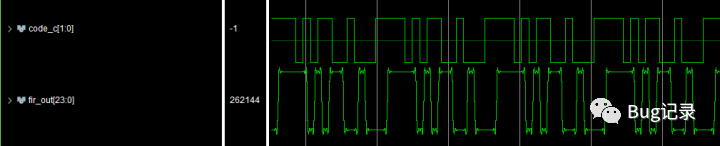

最后的滤波效果如图:

滤波效果图

滤波效果可以继续调节,这里可以看到图里的滤波效果确实达到了,但可能效果不是那么好,实际的滤波参数需要仿真后看效果才可以确定。

FIR滤波相对于IIR滤波而言,没有极点或者说极点与零点抵消了,更加稳定。但如果有时候我们想用IIR滤波器怎么办呢,后续会谈到如何实现IIR滤波器。

-

滤波器

+关注

关注

162文章

8352浏览量

184766 -

MATLAB仿真

+关注

关注

4文章

176浏览量

20765 -

GUI

+关注

关注

3文章

693浏览量

42852 -

FIR滤波

+关注

关注

0文章

6浏览量

10050 -

Vivado

+关注

关注

19文章

846浏览量

70475

发布评论请先 登录

Vivado FIR IP核实现

FIR IP核的基础功能使用总结

FIR IP核的基础功能使用总结

评论