引言

纳米线(NWs)已经为气体和生物传感提供了一个极好的平台, 从而研究如何使纳米线的表面功能化,由于纳米尺度尺寸与分子尺寸兼容性,导致我们需要考虑如何使纳米线的表面功能化,从而以良好的选择性检测特定的气体分子。

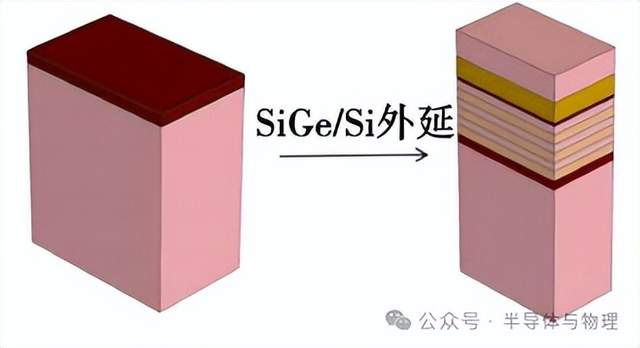

在这种情况下,可以设计NW晶体管,其响应于气体分子的“吸收”或“相互作用”,通过沟道的载流子传输受到影响并被发送信号。对于场效应晶体管来说,为了降低器件尺寸缩小带来的短沟道效应(SCE)和功耗,横向和纵向栅环绕(GAA)场效应晶体管已经成为取代FinFet的趋势。因此,制造精确和可控尺寸的纳米线或纳米片已经成为一项重要的技术。

实验与讨论

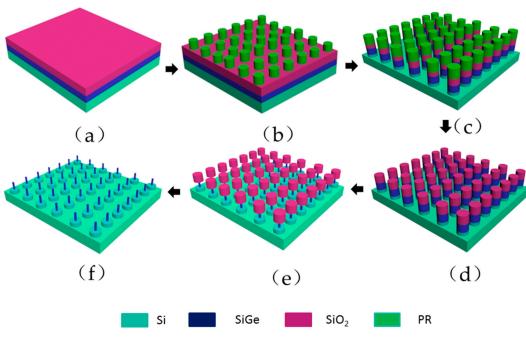

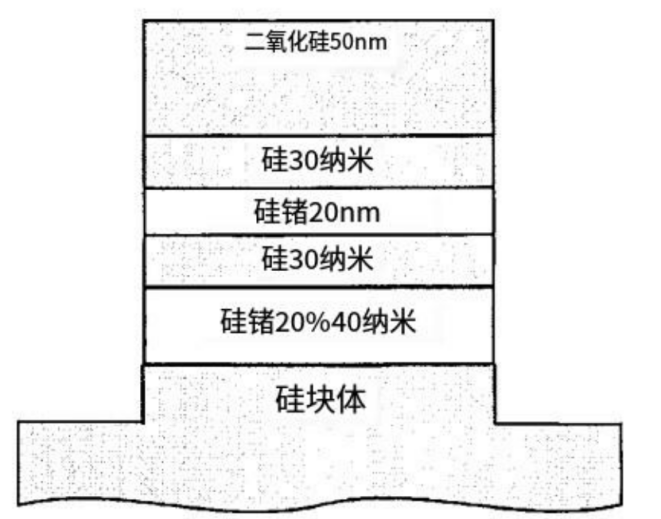

图1:纳米柱制作流程

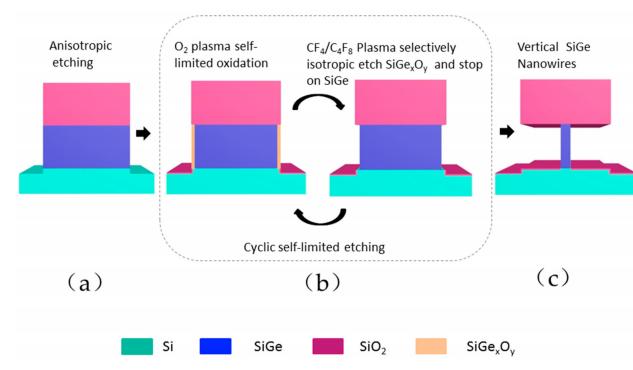

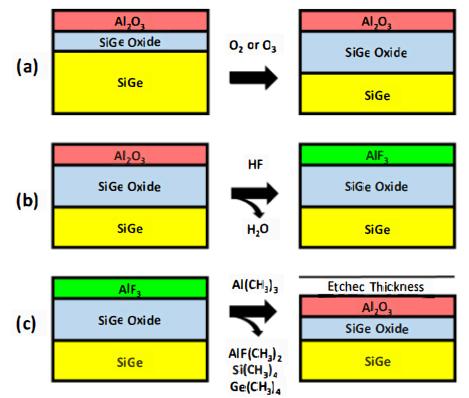

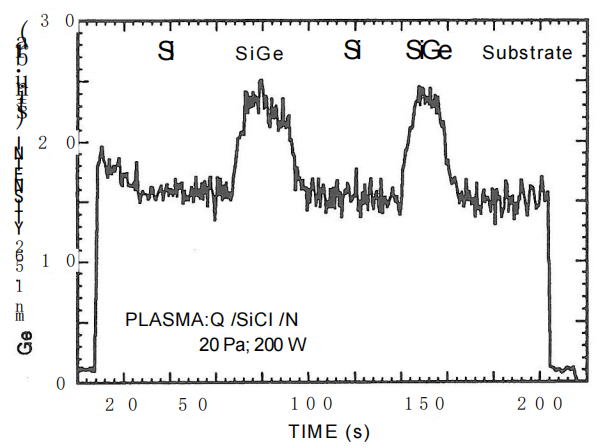

所有材料都是在8英寸(100)硅片上进行的,纳米柱的制造流程如图1,我们通过图2所示的循环蚀刻过程进行实验。这主要是两个自限过程:(1)O2等离子体自限氧化:150sccm O2,500 W源RF/0W偏置功率,处理可达到氧化饱和状态;(2)SiGexOy选择性刻蚀:200 sccm CF4/x sccmC4F8/500W源射频功率/0W偏置功率,用于SiGexOy的选择性刻蚀和SiGe表面的自限停止。重复步骤(1)和(2),直到SiGe纳米线的直径达到预期值。

图2:垂直纳米线的蚀刻过程

自限制顺序反应是原子层蚀刻的主要特征,SiGe的氧化在某些条件下是自限制的。因此,本研究的重点是如何实现SiGexOy的自限性去除(见图2)并自动停止在SiGe层上。我们知道SiGe在O2等离子体下可以氧化成SiGexOy,Si可以氧化成SiO2,但是在形成这些之前,氧化物需要打开原来的共价键。

Si–Si键能(2.31 eV)> Si–Ge键能(2.12 eV),因此SiGe合金比纯Si更容易发生键氧化,Si–O键能(9.0 eV)大于Ge–O键能(5.0 eV),Si–O–Ge键能的值介于两者之间,所以使用CF基气体刻蚀氧化物会形成挥发性的SiFx和GeFx以及CO或CO2。从图中可以看出当CF4流速固定在200sccm并且C4F8比率超过20sccm时,SiGe蚀刻已经被完全抑制,从而实现了SiGexOy层选择性蚀刻的自限制效应。

结论

通过ALE蚀刻,英思特获得了一种制造纳米线的创新方法。根据研究结果表明,纳米线的直径可以在60 ~ 16.5nm范围内灵活调节,形貌精确可控,微结构完整,界面上也没有明显的刻蚀残留物污染。ALE方法可以与先进的光刻(如初始线宽控制到<45nm)技术相结合,未来将有望获得更小的高密度纳米线。这种技术在传感器方面将有非常广泛和有前途的应用。

江苏英思特半导体科技有限公司主要从事湿法制程设备,晶圆清洁设备,RCA清洗机,KOH腐殖清洗机等设备的设计、生产和维护。

审核编辑:汤梓红

-

半导体

+关注

关注

336文章

29980浏览量

258265 -

晶体管

+关注

关注

78文章

10252浏览量

146279 -

蚀刻技术

+关注

关注

0文章

24浏览量

7995

发布评论请先 登录

雷尼绍测头为什么具有各向同性

《炬丰科技-半导体工艺》CMOS 单元工艺

各向同性和各向异性工艺如何用于改善硅湿蚀刻

常见的各向同性湿法刻蚀的实际应用

【虹科方案】如何提高电场探头测量精度?——各向同性的重要性(2)

【虹科EMC测试系列】如何测量各向同性场?

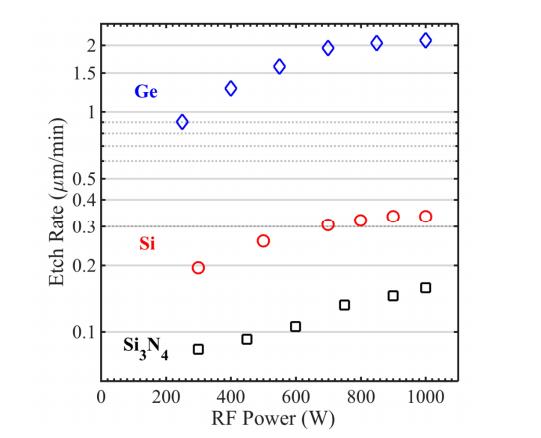

锗、硅、SiNx薄膜的各向同性等离子体蚀刻

锗化硅(SiGe)和硅(Si)之间的各向同性和选择性蚀刻机制

一种新型的锗化硅(SiGe)干式选择性各向同性原子层蚀刻技术

一种新型的锗化硅(SiGe)干式选择性各向同性原子层蚀刻技术

评论