绪论

该项目的目标是展示 HLS 在设计数字系统方面的能力。为此,本文展示如何在 HLS 中描述数字时钟。

时钟在 7 段数码管上显示小时、分钟和秒。

它有两种操作模式:时钟和设置。时钟模式是标准模式,在此模式下,当前时间显示在数码管上。在设置模式下,可以使用按钮设置时间。

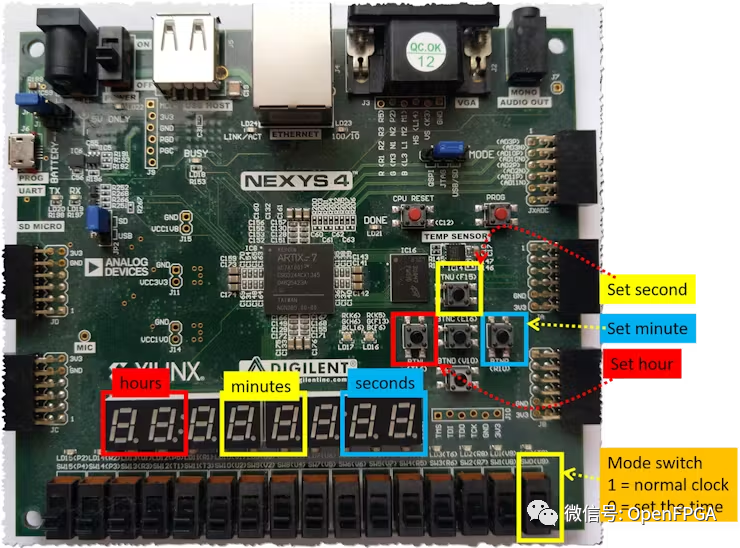

下图显示开发板上的时钟配置。

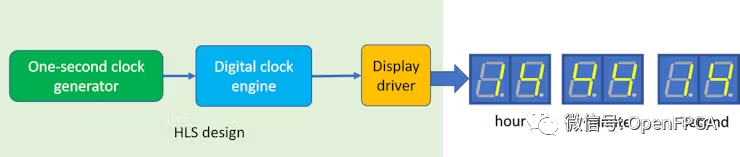

如下图所示,该设计主要分为三个模块:秒时钟发生器、数字时钟引擎和显示驱动。

下面的流水线循环用于实现秒时钟发生器。

booldelay(longlongintn){

#pragmaHLSINLINEoff

staticbooldummy=0;

for(longlongintj=0;j< n; j++) {

#pragma HLS pipeline

dummy = !dummy;

}

return dummy;

}

void one_second_clock_generator(bool &second) {

#pragma HLS INTERFACE ap_none port=second

#pragma HLS INTERFACE ap_ctrl_none port=return

static bool s = 0;

s=!s;

second = s;

delay(50000000L);

}

数字时钟引擎主要是跟踪小时、分钟和秒,并在收到来自秒时钟发生器模块的时钟节拍时更新它们。以下代码完成上诉功能。

voiddebounce(boolpulse,bool&out){

#pragmaHLSINLINEoff

staticboolout0=0;

staticboolout1=0;

staticboolout2=0;

staticboolstate=0;

if(state==0){

out2=out1;

out1=out0;

out0=pulse;

state=1;

}else{

delay(2500000);

state=0;

}

out=out0&out1&out2;

}

voidset_time(

ap_uint<6>&seconds,

ap_uint<6>&minutes,

ap_uint<5>&hours,

boolset_second,

boolset_minute,

boolset_hour)

{

//--------------------------------------------------

staticboolsecond_state=0;

if(second_state==0&&set_second==1){

seconds++;

if(seconds==60){

seconds=0;

}

second_state=1;

}

if(second_state==1&&set_second==0){

second_state=0;

}

//---------------------------------------------------

staticboolminute_state=0;

if(minute_state==0&&set_minute==1){

minutes++;

if(minutes==60){

minutes=0;

}

minute_state=1;

}

if(minute_state==1&&set_minute==0){

minute_state=0;

}

//----------------------------------------------------

staticboolhour_state=0;

if(hour_state==0&&set_hour==1){

hours++;

if(hours==24){

hours=0;

}

hour_state=1;

}

if(hour_state==1&&set_hour==0){

hour_state=0;

}

//----------------------------------------------------

}

voidclock_ticking(

ap_uint<5>&hours,

ap_uint<6>&minutes,

ap_uint<6>&seconds)

{

seconds++;

if(seconds==60){

seconds=0;

minutes++;

if(minutes==60){

minutes=0;

hours++;

if(hours==24)

hours=0;

}

}

}

voiddigital_clock(

boolset_time_sw,

bool&set_time_led,

boolset_second,

boolset_minute,

boolset_hour,

boolone_second_delay,

ap_uint<6>&seconds_out,

ap_uint<6>&minutes_out,

ap_uint<5>&hours_out

)

{

#pragmaHLSINTERFACEap_noneport=set_time_sw

#pragmaHLSINTERFACEap_noneport=set_time_led

#pragmaHLSINTERFACEap_noneport=set_minute

#pragmaHLSINTERFACEap_noneport=set_hour

#pragmaHLSINTERFACEap_noneport=seconds_out

#pragmaHLSINTERFACEap_noneport=minutes_out

#pragmaHLSINTERFACEap_noneport=hours_out

#pragmaHLSINTERFACEap_ctrl_noneport=return

staticap_uint<6>seconds=0;

staticap_uint<6>minutes=0;

staticap_uint<5>hours=0;

ap_uint<8>segment_data;

ap_uint<8>segment_enable;

staticboolstate_clock=0;

boolone_second=one_second_delay;

boolset_time_flag=set_time_sw;

if(one_second==1&&set_time_flag==0&&state_clock==0){

clock_ticking(hours,minutes,seconds);

state_clock=1;

}

if(one_second==0&&set_time_flag==0&&state_clock==1){

state_clock=0;

}

if(set_time_flag==1){

boolset_minute_debounce;

boolset_hour_debounce;

boolset_second_debounce;

debounce(set_minute,set_minute_debounce);

debounce(set_hour,set_hour_debounce);

debounce(set_second,set_second_debounce);

set_time(seconds,minutes,hours,set_second_debounce,set_minute_debounce,set_hour_debounce);

}

seconds_out=seconds;

minutes_out=minutes;

hours_out=hours;

set_time_led=set_time_sw;

}

最后一个 HLS 代码在 7 段数码管上显示当前时间。

#includeconstap_uint<8>seven_segment_code[10]={ 0b11000000, 0b11111001, 0b10100100, 0b10110000, 0b10011001, 0b10010010, 0b10000010, 0b11111000, 0b10000000, 0b10010000 }; booldelay(longlongintn){ #pragmaHLSINLINEoff staticbooldummy=0; for(longlongintj=0;j< n; j++) { #pragma HLS pipeline dummy = !dummy; } return dummy; } void seven_segment_display( ap_uint<5>hours, ap_uint<6>minutes, ap_uint<6>seconds, ap_uint<8>&seven_segment_data, ap_uint<8>&seven_segment_enable) { #pragmaHLSINTERFACEap_noneport=hours #pragmaHLSINTERFACEap_noneport=minutes #pragmaHLSINTERFACEap_noneport=seconds #pragmaHLSINTERFACEap_noneport=seven_segment_data #pragmaHLSINTERFACEap_noneport=seven_segment_enable #pragmaHLSINTERFACEap_ctrl_noneport=return ap_uint<4>second_digit_1=seconds%10; ap_uint<4>second_digit_2=seconds/10; ap_uint<4>minute_digit_1=minutes%10; ap_uint<4>minute_digit_2=minutes/10; ap_uint<4>hours_digit_1=hours%10; ap_uint<4>hours_digit_2=hours/10; ap_uint<8>segment_data; ap_uint<8>segment_enable; staticap_uint<3>state=0; switch(state){ //second case0: segment_data=seven_segment_code[second_digit_1]; segment_enable=0b11111110; delay(250000L); state=1; break; case1: segment_data=seven_segment_code[second_digit_2]; segment_enable=0b11111101; state=2; delay(250000L); break; //minutes case2: segment_data=seven_segment_code[minute_digit_1]; segment_enable=0b11110111; state=3; delay(250000L); break; case3: segment_data=seven_segment_code[minute_digit_2]; segment_enable=0b11101111; state=4; delay(250000L); break; //hours case4: segment_data=seven_segment_code[hours_digit_1]; segment_enable=0b10111111; state=5; delay(250000L); break; case5: segment_data=seven_segment_code[hours_digit_2]; segment_enable=0b01111111; state=0; delay(250000L); break; default: segment_data=seven_segment_code[0]; segment_enable=0b11111111; state=0; delay(250000L); break; } seven_segment_data=segment_data; seven_segment_enable=segment_enable; }

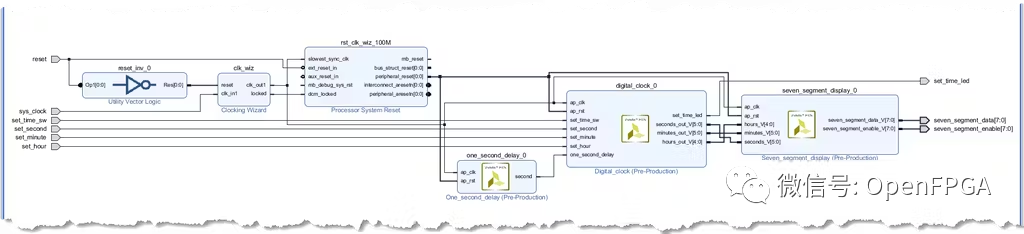

综合这些代码后,使用 Vivado 工具将它们连接在一起并生成 FPGA 比特流。

对电路板编程后,可以看到下图:

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22502浏览量

639128 -

数码管

+关注

关注

32文章

1894浏览量

94415 -

时钟发生器

+关注

关注

1文章

358浏览量

70160 -

数字时钟

+关注

关注

2文章

156浏览量

21650 -

HLS

+关注

关注

1文章

135浏览量

25976

原文标题:HLS 设计数字时钟

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

如何在Unified IDE中创建视觉库HLS组件

Vivado IP 流程(Vitis Unified),在这篇 AMD Vitis HLS 系列 3 中,我们将介绍如何使用 Unified IDE 创建 HLS 组件。这里采用“自下而上”的流程,从

如何在HLS 14.3中编写pow功能?

嗨〜 如何在HLS 14.3中编写pow功能? HLS 14.3不支持exp和pow功能。我在我的代码中写了“#include math.h

发表于 03-05 13:40

合成中的Vivado HLS中的Pragma错误怎么解决

模拟过程完成没有0错误,但在合成期间显示错误。我无法找到错误。我在合成期间在HLS工具中收到这样的错误“在E中包含的文件:/thaus / fact_L / facoriall

发表于 05-21 13:58

【正点原子FPGA连载】第一章HLS简介-领航者ZYNQ之HLS 开发指南

的ARM处理器或MicroBlaze软核处理器)中的软件代码是截然不同的。在HLS中,所有的C设计都是要在可编程逻辑中实现的,也就是说,我们仍然是在进行硬件设计,只不过使用的不再是硬件

发表于 10-10 16:44

数字时钟设计功能描述

数字时钟设计功能描述1、初始化1)关闭蜂鸣器、继电器等无关外设;2)DS1302设备初始化时钟为 23 时 59 分 50 秒。2、显示功能3、按键功能1)按键 S4 定义为

发表于 02-18 06:09

FPGA高层次综合HLS之Vitis HLS知识库简析

1、HLS最全知识库介绍高层次综合(High-level Synthesis)简称HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。对于AMD Xi

发表于 09-07 15:21

使用Vitis HLS创建属于自己的IP相关资料分享

1、使用Vitis HLS创建属于自己的IP高层次综合(High-level Synthesis)简称HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过

发表于 09-09 16:45

Vivado环境下如何在IP Integrator中正确使用HLS IP

testbench来验证设计。 Integrate带有Xilinx IP Block的 HLS IP 这里展示了在IP Integrator中,如何将两个HLS IP blocks跟Xilinx IP FFT结合在一起 ,并且

发表于 02-07 17:59

•4840次阅读

FPGA设计中的HLS 工具应用

HLS,高层综合)。这个工具直接使用C、C++或SystemC 开发的高层描述来综合数字硬件,这样就不再需要人工做出用于硬件的设计,像是VHDL 或Verilog 这样的文件,而是由HLS

发表于 06-04 01:43

•7808次阅读

关于Vivado HLS错误理解

尽管 Vivado HLS支持C、C++和System C,但支持力度是不一样的。在v2017.4版本ug871 第56页有如下描述。可见,当设计中如果使用到任意精度的数据类型时,采用C++ 和System C 是可以使用Viv

HLS协议实现

HLS,Http Live Streaming 是由Apple公司定义的用于实时流传输的协议,HLS基于HTTP协议实现,传输内容包括两部分,一是M3U8描述文件,二是TS媒体文件。

如何在Vitis HLS GUI中使用库函数?

Vitis™ HLS 2023.1 支持新的 L1 库向导,本文将讲解如何下载 L1 库、查看所有可用功能以及如何在 Vitis HLS GUI 中使用库函数。

HLS设计中的BRAM使用优势

高层次综合(HLS)是一种将高级编程语言(如C、C++或SystemC)转换为硬件描述语言(HDL)的设计方法。在FPGA设计中,设计者可以灵活地利用FPGA内部的资源,如块RAM(BRAM)。虽然

如何在HLS中描述数字时钟?

如何在HLS中描述数字时钟?

评论