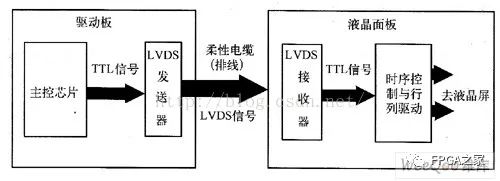

1.1.1 LVDS接口分类

1.1.1.1 单路6bit LVDS

这种接口电路中,采用单路方式传输,每个基色信号采用6位数据,共18位RGB数据,因此,也称18位或18bit LVDS接口。此,也称18位或18bit LVDS接口。

1.1.1.2 双路6bit LVDS

这种接口电路中,采用双路方式传输,每个基色信号采用6位数据,其中奇路数据为18位,偶路数据为18位,共36位RGB数据,因此,也称36位或36bit LVDS接口。

1.1.1.3 单路8bit LVDS

这种接口电路中,采用单路方式传输,每个基色信号采用8位数据,共24位RGB数据,因此,也称24位或24bit LVDS接口。

1.1.1.4 双路8bit LVDS

这种接口电路中,采用双路方式传输,每个基色信号采用8位数据,其中奇路数据为24位,偶路数据为24位,共48位RGB数据,因此,也称48位或48bitLVDS接口

1.1.2 LVDS发送芯片介绍

典型之LVDS发送芯片分为四通道、五通道和十通道几种,下面简要进行介绍。

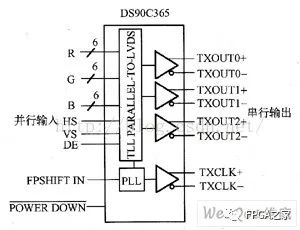

1.1.2.1四通道LVDS发送芯片

图2 所示为四通道LVDS发送芯片内部框图。包含了三个数据信号(其中包括RGB、数据使能DE、行同步信号HS、场同步信号VS)通道和一个时钟信号发送通道。

4通道LVDS发送芯片主要用于驱动6bit液晶面板。使用四通道LVDS发送芯片可以构成单路6bit LVDS接自电路和奇/偶双路6bit LVDS接口电路。

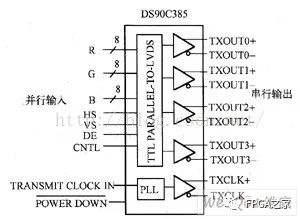

1.1.2.2 五通道LVDS发送芯片

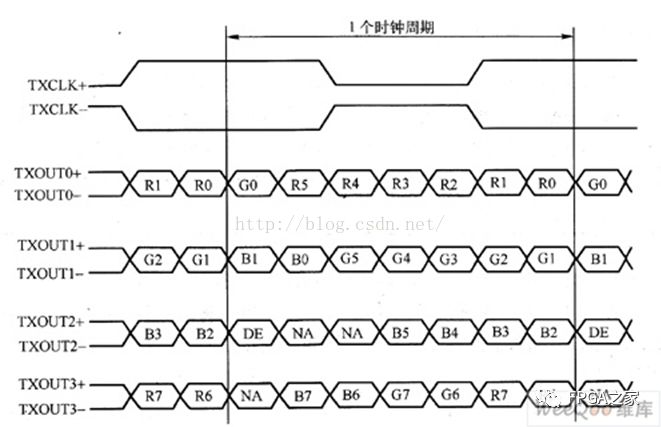

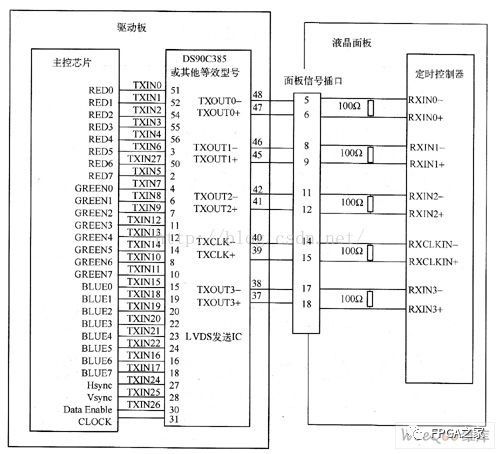

图3 所示为五通道LVDS发送芯片(DS90C385)内部框图。包含了四个数据信号(其中包括RGB、数据使能DE、行同步信号HS、场同步信号VS)通道和一个时钟信号发送通道。

五通道LVDS发送芯片主要用于驱动8bit液晶面板。使用五通道LVDS发送芯片主要用来构成单路8bit LVDS接口电路和奇/偶双路8bitLVDS接口电路。

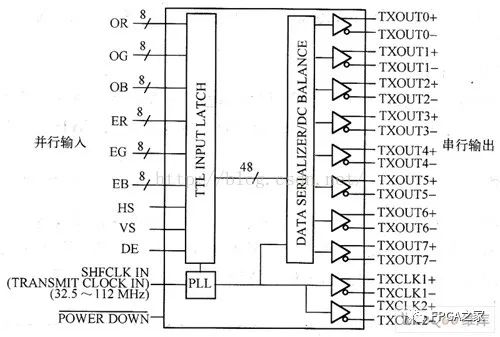

1.1.2.3 十通道LVDS发送芯片

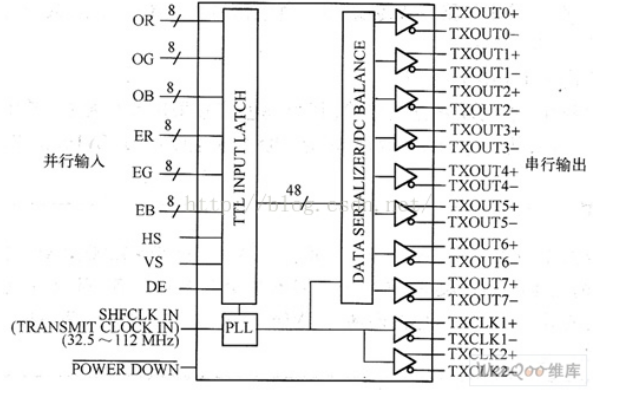

图4所示为十通道LVDS发送芯片(DS90C387)内部框图。包含了八个数据信号(其中包括RGB、数据使能DE、行同步信号HS、场同步信号VS)通道和两个时钟信号发送通道。

十通道LVDS发送芯片主要用于驱动8bit液晶面板。使用十通道LVDS发送芯片主要用来构成奇/偶双路8bit LVDS位接口电路。

在十通道LVDS发送芯片中,设置了两个时钟脉冲输出通道,这样做之目之是可以更加灵活之适应不同类型之LVDS接收芯片。当LVDS接收电路同样使用一片十通道LVDS接收芯片时,只需使用一个通道之时钟信号即可;当LVDS接收电路使用两片五通道LVDS接收芯片时,十通道LVDS发送芯片需要为每个LVDS接收芯片提供单独之时钟信号。

1.1.3LVDS发送芯片之输入与输出信号

1.1.3.1 LVDS发送芯片之输入信号

LVDS发送芯片之输入信号来自主控芯片,输入信号包含RGB数据信号、时钟信号和控制信号三大类。为了说明之方便,将RGB信号以及数据选通DE和行场同步信号都算作数据信号。

输入数据信号

在供6bit液晶面板使用之四通道LVDS发送芯片中,共有十八个RGB信号输入引脚;一个显示数据使能信号DE(数据有效信号)输入引脚;一个行同步信号HS输入引脚;一个场同步信号VS输入引脚。也就是说,在四通道LYDS发送芯片中,共有二十一个数据信号输入引脚。

在供8bit液晶面板使用之五通道LVDS发送芯片中,共有二十四个RGB信号输入引脚;一个显示数据使能信号DE(数据有效信号)输入引脚;一个行同步信号HS输入引脚;一个场同步信号VS输入引脚;也就是说,在五通道LVDS发送芯片中,共有二十八个数据信号输入引脚。

应该注意的是,液晶面板的输入信号中都必须要有DE信号,但有的液晶面板只使用单一的DE信号而不使用行场同步信号。因此,应用于不同的液晶面板时,有的LVDS发送芯片可能只需输入DE信号,而有的需要同时输入DE和行场同步信号。

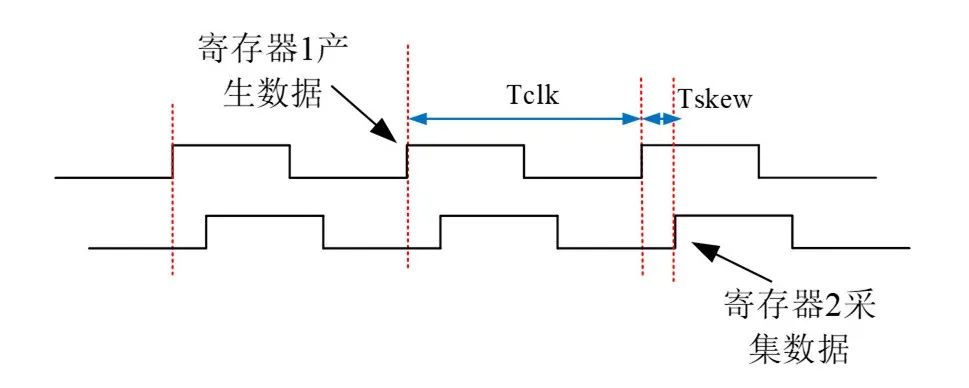

输入时钟信号:即像素时钟信号,也称为数据移位时钟(在LVDS发送芯片中,将输入之并行RGB数据转换成串行数据时要使用移位寄存器)。像素时钟信号是传输数据和对数据信号进行读取之基准。

待机控制信号(POWER DOWN):当此信号有效时(一般为低电平时),将关闭LVDS发送芯片中时钟PLL锁相环电路之供电,停止IC之输出。

数据取样点选择信号:用来选择使用时钟脉冲之上升沿还是下降沿读取所输入之RGB数据。有之LVDS发送芯片可能并不设置待机控制信号和数据取样点选择信号,但也有之除了上述两个控制信号还设置有其他一些控制信号。

1.1.3.2LVDS发送芯片之输出信号

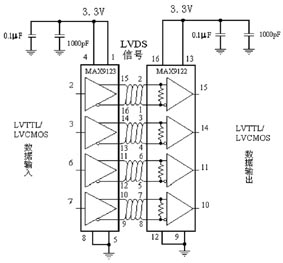

LVDS发送芯片将以并行方式输入的TTL电平RGB数据信号转换成串行之LVDS信号后,直接送往液晶面板侧之LVDS接收芯片。

LVDS发送芯片的输出是低摆幅差分对信号,一般包含一个通道的时钟信号和几个通道的串行数据信号。由于LVDS发送芯片是以差分信号的形式进行输出,因此,输出信号为两条线,一条线输出正信号,另一条线输出负信号。

时钟信号输出:LVDS发送芯片输出之时钟信号频率与输入时钟信号(像素时钟信号)频率相同。时钟信号的输出常表示为:TXCLK+和TXCLK-,时钟信号占用LVDS发送芯片的一个通道。

LVDS串行数据信号输出:对于四通道LVDS发送芯片,串行数据占用三个通道,其数据输出信号常表示为TXOUT0+、TXOUT0-,TXOUT1+、TXOUT1-,TXOUT2+、TXOUT2-。

对于五通道LYDS发送芯片,串行数据占用四个通道,其数据输出信号常表示为TXOUT0+、TXOUT0-,TXOUT1+、TXOUTI-,TXOUT2+、TXOUT2-,TXOUT3+、TXOUT3-。

对于十通道LVDS发送芯片,串行数据占用八个通道,其数据输出信号常表示为TXOUT0+、TXOUT0-,TXOUT1+、TXOUT1-,TXOUT2+、TXOUT2-,TXOUT3+、TXOUT3-,TXOUT4+、TXOUT4-,TXOUT5+、TXOUT5-,TXOUT6+、TXOUT6-,TXOUT7+、TXOLT7-。

注意:

如果只看电路图,是不能从LVDS发送芯片的输出信号TXOUT-、TXOUT0+中看出其内部到底包含哪些信号数据,以及这些数据是怎样排列的(或者说这些数据的格式是怎样额)。事实上,不同厂家生产的LVDS发送芯片,其输出数据排列方式可能是不同的。因此,液晶显示器驱动板上的LVDS发送芯片的输出数据格式必须与液晶面板LVDS接收芯片要求的数据格式相同,否则,驱动板与液晶面板不匹配。这也是更换液晶面板时必须考虑的一个问题。

如果表示明白,你就数带 “+-”的这种信号线一共有几对,

有10对的减掉2对(时钟信号)就是双8。

有8对的减掉2对 (时钟信号)就是双6。

有5对的减掉1对(时钟信号)对是单8。

有4对的减掉1对 (时钟信号)是单6。

如果既无资料,也看不清标识,最简单的办法就是看看里面的电路,一般每对数据线之间都有一个100欧姆的电阻,数电阻的个数,看到4个的话就是单口6位颜色的屏,看到8个的话就是双口六位,5个的话一般是单口8位,有10个一般就是双口8位。

1.1.4LVDS数据输出格式

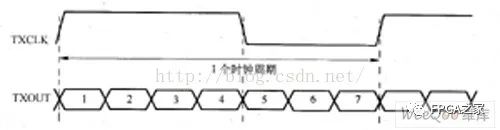

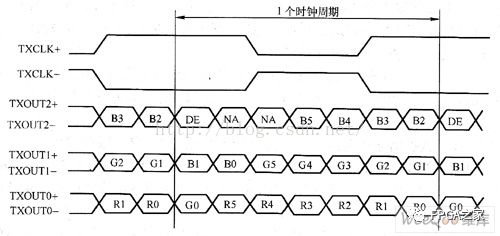

LVDS发送芯片在一个时钟脉冲周期内,每个数据通道都输出7bit的串行数据信号,而不是常见的8bit数据,如图5所示

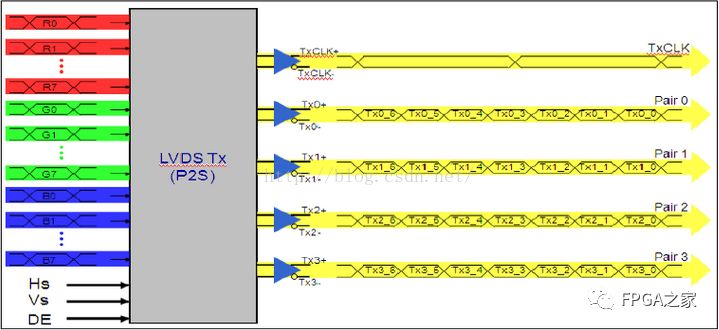

在LCD液晶屏中,需要输出到显示屏的信号是并行的图像信号和控制信号,而LVDS信号是串行传输的,所以在发送端需要将并行数据转换为串行数据。以8bit RGB显示屏接口为例,每个显示周期需要传输8bit的R信号,8bit的G 信号,8bit 的B信号,及VS,HS,DE信号,总共为27 BIT。而每对LVDS信号线在一个TX周期里只能传输7BIT数据,所以需要4 对数据线,外加一对时钟线。LVDS并串转换如下图所示:

上图中的每一组对线称为一个Pair,4组数据线加一对时钟线称为一个Channel,LVDS发送器总是将一个像素数据映射到(remapping)一个Channel的一个发送周期(TX CLK)中。

如果是6BIT 显示屏,则并行数据有21位(18位RGB加3位控制信号),因此LVDS 接口每个Channel只需要 3对数据线和一对时钟线。

如果是10BIT 显示屏,则并行数据有33位(30位RGB 加3位控制信号),因此LVDS 接口每个Channel需要 5对数据线和一对时钟线。

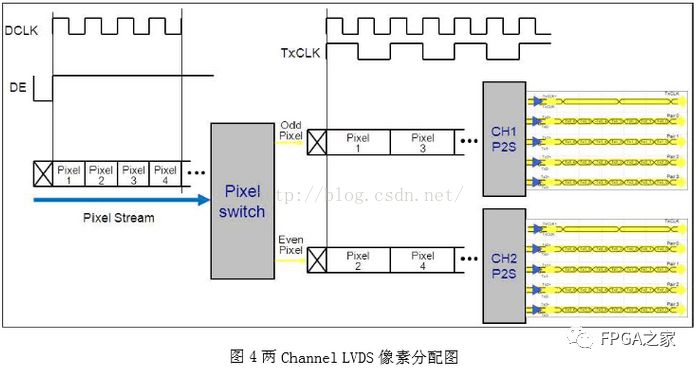

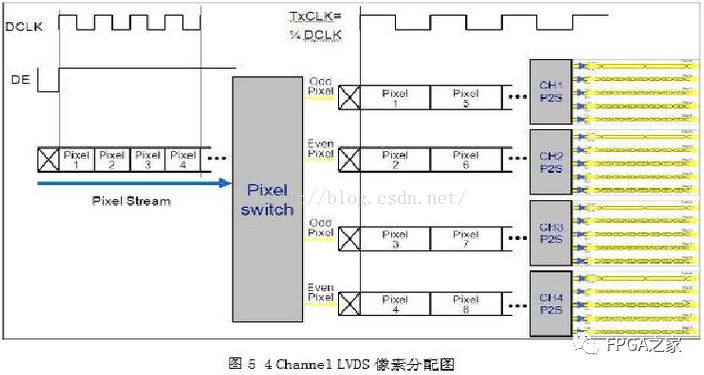

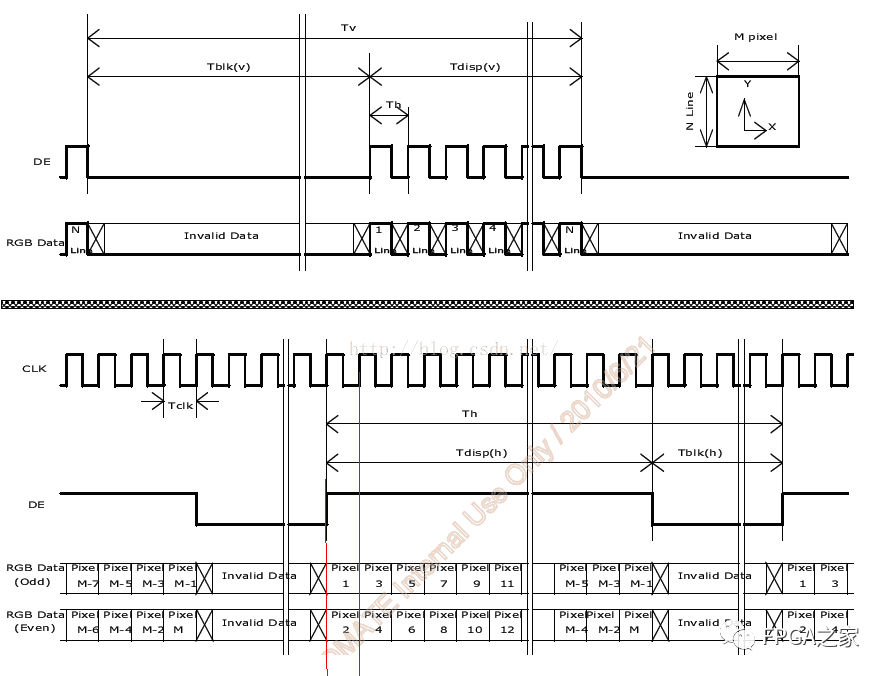

通常,LVDS接口的时钟为20MHz 到85MHz,因此对于输出像素时钟低于85MHz的信号,只需一个Channel就可以;而对于输出像素时钟高于85MHZ的信号,比如1080P/60HZ的输出,像素显示时钟为148.5MHz,就不能直接用一个Channel传输,而是将输出的像素按顺序分为奇像素和偶像素,将所有的奇像素用一组LVDS 传输,所有的偶像素用另外一组LVDS 传输。也就是说,需要两个Channel来传输1080P/60HZ 的信号。对于像素显示时钟更高的信号,比如1080P/120HZ显示,则需要4个Channel来传输。两Channel、4Channel的像素分配分别如图4、图5所示:

1.1.5 LVDS 数据映射标准

LVDS数据映射(MappingMapping)标准

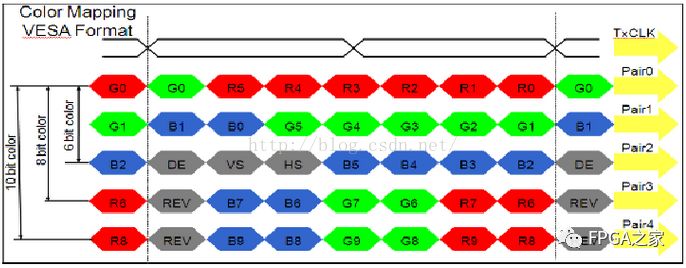

LVDS接口电路中,将像素的并行数据转换为串行数据的格式主要有两种标准:VESA和JEIDA

VSEA标准如下图所示:

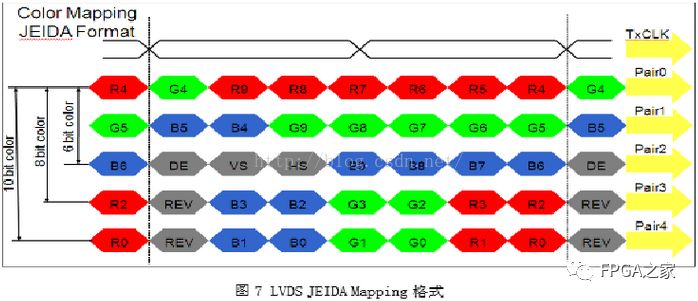

JEIDA标准是由日本电子行业开发协会(JAPANELECTRONIC INDUSTRY DEVELOPMENT ASSOCIATION)制定的标准,其格式如下

对于JEIDA格式,需要注意的是,如果像素为6bit RGB,则每个通道只需要最上面的3对数据线,其中的R9…R4, G9…G4, B9…B4 对应实际的R5…R0, G5…G0, B5…B0;同样,如果像素是 8 bit RGB,则每个通道只需要靠上面的4对数据线,其中的R9…R2, G9…G2, B9…B2 对应实际的R7…R0, G7…G0, B7…B0。

另外,COLOR MAPPING 也可以采用自定义格式,只要LVDS 发送端和接受端采用相同的映射顺序,就可以显示正确的色彩

1.1.6 LVDS 数据传输模式

LVDS信号传输分为DE MODE和SYNC MODE,DE mode需连接DE信号(data enable有效数据选通),SYNC mode还需连接HS(HSYNC行同步)、VS(VSYNC场同步)。

SYNC mode在现在的panel中已很少使用。下面是DE mode的数据形式。

1.1.7LVDS 数据格式详解

LVDS发送芯片输出信号的格式:即LVDS发送芯片输入的RGB数据,以及行同步信号HS、场同步信号VS、有效显示数据使能信号DE在各个输出通道中数据位的排列顺序。

由于几个大的LYDS芯片生产厂家制定了不同的标准,因此,存在着几种不同的LVDS发送芯片数据输出格式;

1.1.7.1单路 6BIT LVDS输出

单路6bit LVDS发送芯片数据输出格式:单路6bit LVDS发送电路使用四通道LVDS发送芯片,输出信号格式如图6所示。

图中NA的意思是未使用。此例为控制信号仅使用DE的模式,未使用行同步信号HS和场同步信号VS。关于DE、IIS、VS信号的使用问题。当控制信号为DE+行场同步信号模式时,图中的两个NA更换为场同步信号VS和行同步信号HS。

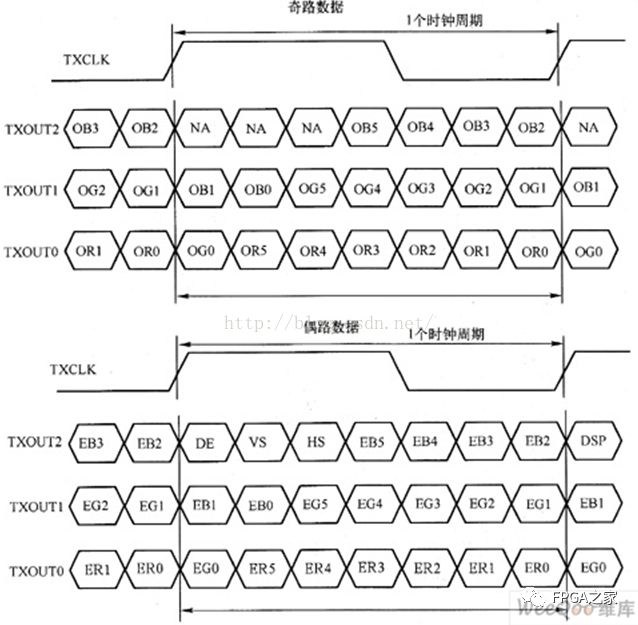

1.1.7.2双路6BIT LVDS输出

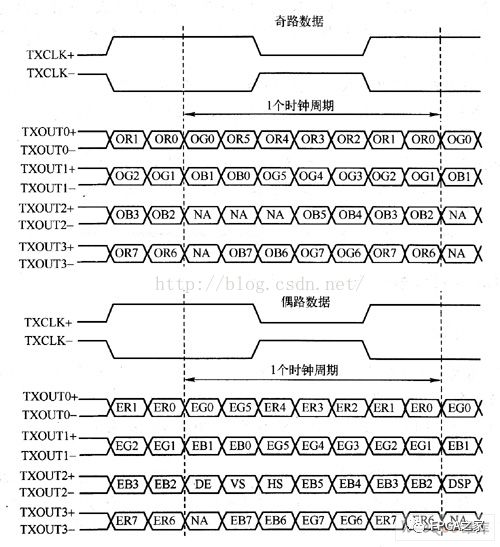

双路6bit LVDS发送芯片数据输出格式:双路6bit LVDS发送电路使用两片四通道LVDS发送芯片,输出信号格式如图7所示。

从图中可以看出,双路6bit LVDS发送芯片数据输出格式与单路6bit LVDS发送芯片数据输出格式是相同的,只不过一路传送奇数像素RGB数据,另工路传送偶数像素RGB数据。OR0、OR1、…中的“O”代表奇数像素,ER0、ER1、…中的“E”代表偶数像素。

1.1.7.3单路 6BIT LVDS输出

单路8bit LVDS发送芯片数据输出格式:单路8bit LVDS发送电路使用五通道LVDS发送芯片,输出信号格式有多种,下面只介绍其中的两种。

下图所示为单路8bitLVDS发送芯片的另一种数据输出格式。

所示格式中的控制信号仅使用DE模式,当控制信号为DE+行场同步信号模式时,第二数据通道TXOUT2中的两个NA应更换为场同步信号VS和行同步信号HS(通过对驱动板编程可改写)。

从以上两种输出格式中可以看出,数据信号的排列顺序差别很大,不过,要想让其排列一致,完全可以通过对驱动板编程来完成。

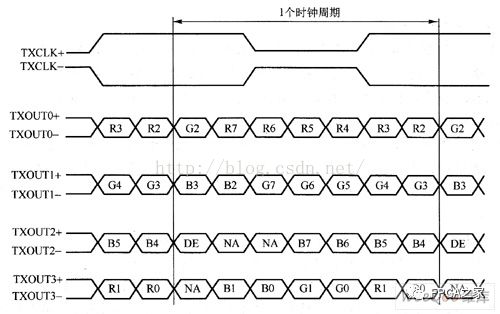

1.1.7.4双路8BIT LVDS输出

双路8bit LVDS发送芯片数据输出格式:双路8bit LVDS发送电路使用两片五通道LVDS发送芯片或一片十通道LVDS发送芯片,双路8bit LVDS发送芯片数据输出格式也有多种形式,所示是其中的一种。

审核编辑:汤梓红

-

芯片

+关注

关注

463文章

54441浏览量

469421 -

接口

+关注

关注

33文章

9601浏览量

157628 -

RGB

+关注

关注

4文章

836浏览量

62235 -

lvds

+关注

关注

2文章

1244浏览量

70233 -

时序

+关注

关注

5文章

411浏览量

39006

原文标题:LVDS,接口,时序讲解,非常好的文章

文章出处:【微信号:Hack电子,微信公众号:Hack电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何调整LVDS时钟频率和时序?

基于FPGA的LVDS接口应用

LVDS接口有哪些分类

高速ADC与FPGA的LVDS数据接口中避免时序误差的设计考虑

LVDS、接口和时序讲解

LVDS、接口和时序讲解

评论