引言

等离子体蚀刻是氮化镓器件制造的一个必要步骤,然而,载体材料的选择可能会实质上改变蚀刻特性。在小型单个芯片上制造氮化镓(GaN)设备,通常会导致晶圆的成本上升。在本研究中,英思特通过铝基和硅基载流子来研究蚀刻过程中蚀刻速率、选择性、形貌和表面钝化的影响。

实验与讨论

我们实验中使用的晶片依次通过丙酮、甲醇和异丙醇进行超声清洗5分钟,然后在3:1硫酸和30%过氧化氢(食人鱼)的自热溶液中清洗15分钟。采用二氧化硅作为硬掩模,在等离子体热沉积系统中利用等离子体来增强化学气相沉积(PECVD)。除了氮化镓晶圆,裸硅晶圆也在相同的等离子体增强化学气相沉积运行中被涂层,以创建具有相同二氧化硅层的硅见证体。

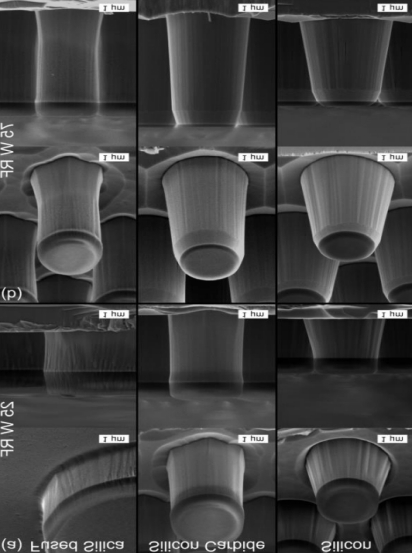

图1:在(a) 25 W射频功率和(b) 75 W射频功率下使用硅基载流子时,腐蚀了在45°和90°下倾斜的氮化镓柱的扫描电子显微图。

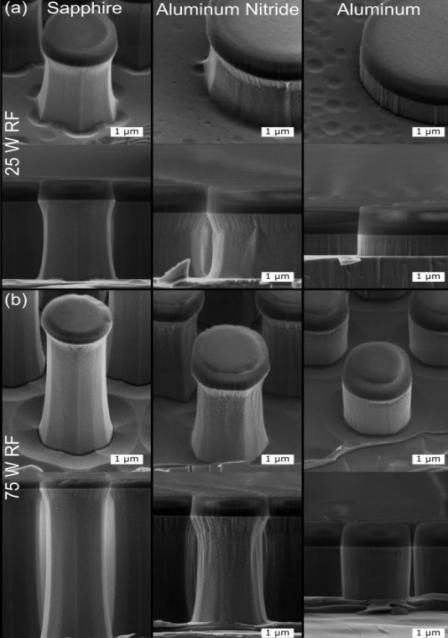

用硅基和铝基蚀刻氮化镓柱后的电镜图分别如图1和图2所示。芯片在25W和75W的射频功率下进行了蚀刻。在两种射频功率下,蚀刻形态都受到载体材料选择的强烈影响。硅(一种常用的载体晶片),与其他载体相比,对柱状形态有显著影响。值得注意的是,熔融二氧化硅、氮化铝和铝载体的掩模侵蚀最小,硅和碳化硅载流子的附带载体蚀刻中的蚀刻产物,引起了二氧化硅掩模中蚀刻的增强。

图2:在(a) 25 W射频功率和(b) 75 W射频功率下使用铝基载体时,在45°和90°下倾斜的氮化镓柱的扫描电镜图。

结论

英思特研究表明,蓝宝石是最惰性的载体,可以最佳控制氮化镓蚀刻条件,同时也可以产生最高的氮化镓蚀刻率。由氮化铝或铝掩模释放出的铝,由于与二氧化硅掩模的表面反应增加了选择性。我们发现铝和二氧化硅的再生作用具有钝化的潜力,并且后续还需要我们进一步探索。

江苏英思特半导体科技有限公司主要从事湿法制程设备,晶圆清洁设备,RCA清洗机,KOH腐殖清洗机等设备的设计、生产和维护。

审核编辑黄宇

-

半导体

+关注

关注

336文章

29985浏览量

258286 -

晶圆

+关注

关注

53文章

5344浏览量

131690 -

蚀刻

+关注

关注

10文章

428浏览量

16463

发布评论请先 登录

晶圆湿法刻蚀技术有哪些优点

wafer晶圆厚度(THK)翘曲度(Warp)弯曲度(Bow)等数据测量的设备

wafer晶圆几何形貌测量系统:厚度(THK)翘曲度(Warp)弯曲度(Bow)等数据测量

wafer晶圆几何形貌测量系统:厚度(THK)翘曲度(Warp)弯曲度(Bow)等数据测量

提供半导体工艺可靠性测试-WLR晶圆可靠性测试

晶圆高温清洗蚀刻工艺介绍

什么是高选择性蚀刻

湿法刻蚀:晶圆上的微观雕刻

芯片湿法蚀刻工艺

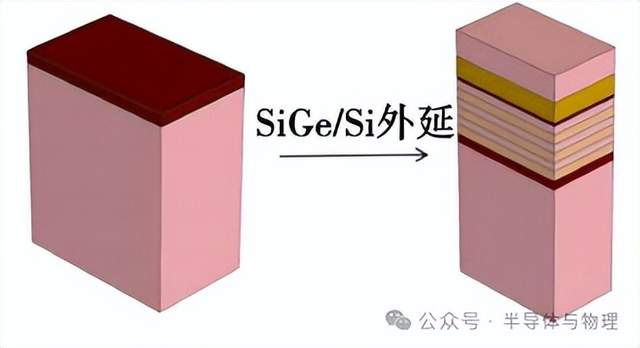

SiGe与Si选择性刻蚀技术

载体晶圆对蚀刻速率、选择性、形貌的影响

载体晶圆对蚀刻速率、选择性、形貌的影响

评论