在 CXL 生态系统中,主机软件使用枚举作为发现系统中连接的 CXL 设备的第一步。

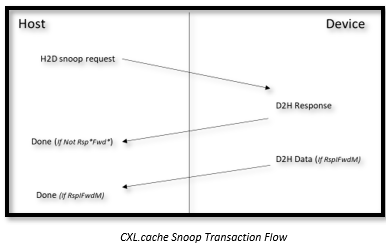

在此过程中,它会识别 CXL 生态系统中的连接设备是否是以下设备类型之一 – PCIe、CXL 1.1 或 CXL 2.0。它根据 PCIe 配置空间和 CXL 规范定义的功能和配置寄存器确定这一点。

本博客将重点介绍 CXL 2.0 设备发现。

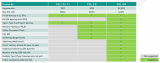

CXL 2.0 规范在 PCIe 配置空间映射寄存器中定义了多个新的 PCIe 指定供应商特定扩展功能 (DVSEC)。以下是 CXL 2.0 设备的一些强制性 DVSEC。

用于 CXL 设备的 PCIe DVSEC

用于 CXL 设备的 GPF DVSEC

用于柔性总线端口的 PCIe DVSEC

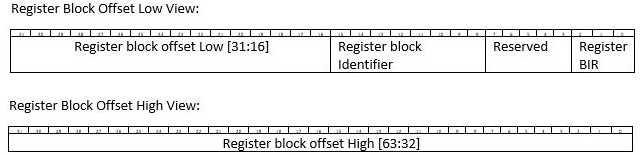

注册定位器 DVSEC

CXL 1.1 设备在枚举层次结构中显示为 RCiEP(根复杂集成终结点)设备。要使 CXL 2.0 设备对操作系统可见,必须将它们作为具有 Type0 标头的标准 PCIe 端点被发现。DVSEC ID 为“1”的 CXL DVSEC(供应商 ID 98e0)的存在有助于区分 PCIe 端点或 CXL 2.0 设备。

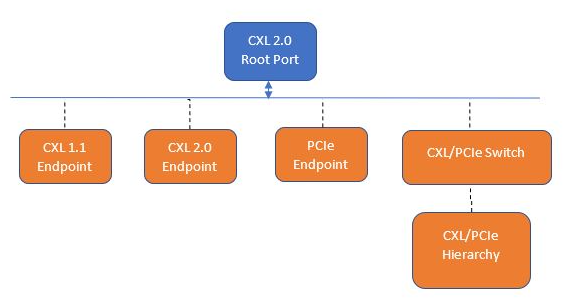

下图显示了复杂的 CXL 2.0 拓扑的示例,其中显示了 CXL 根端口可以连接到以下任何命名设备:

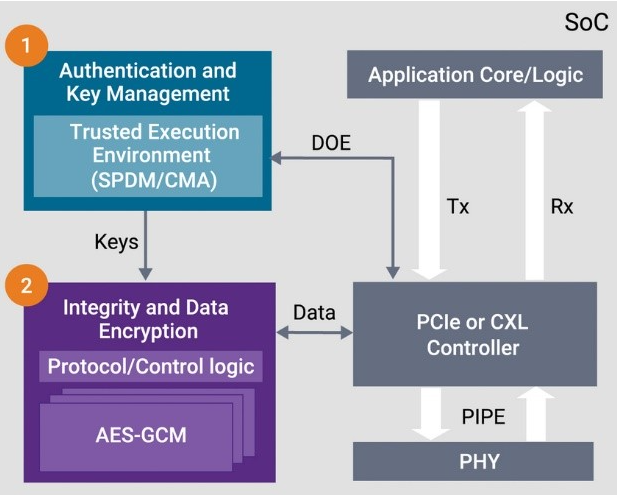

CXL 2.0 控制和状态寄存器 (CSR) 还利用 PCIe 配置空间和 BAR(基址寄存器)进行内存映射寄存器,从而增加了功能发现以及随后的配置控制和状态监控的复杂性。

总体而言,CXL 1.1/2.0 设备配置和状态寄存器空间非常多样化。

审核编辑:郭婷

-

操作系统

+关注

关注

37文章

7328浏览量

128602 -

总线

+关注

关注

10文章

3014浏览量

91286 -

PCIe

+关注

关注

16文章

1420浏览量

87527

发布评论请先 登录

澜起科技PCIe 5.0/CXL 2.0 Retimer芯片实现量产

CXL内存协议介绍

一文详解CXL链路层格式的定义

澜起科技PCIe 5.0/CXL 2.0 Retimer芯片实现量产

关于CXL的功能与特性详解

CXL 2.0设备发现的迷人路径

CXL 2.0设备发现的迷人路径

评论