您的电子设计空间是否受限?需要进入一个小外壳,但仍然有很多功能?PCB技术是否值得关注成本?

是的?好。我们应该谈谈,所以请继续阅读。

故事始于拥有适合您设计的低功耗 FPGA。基于Microchip闪存的PolarFire® FPGA就是这种设备,它通常设计为在没有任何散热器的情况下工作,也可以在高环境温度下工作。PolarFire还有一个较老的兄弟,Igloo2和SmartFusion2 FPGA和SoC,低功耗主题也适用。

在本文中,我不会详细介绍FPGA本身,但会看一下封装故事。

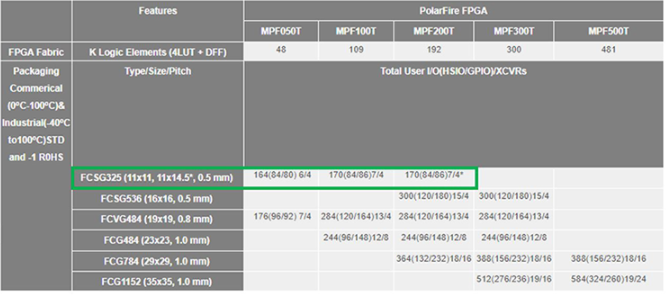

看看PolarFire的产品表,包装故事看起来相当无害。一些读者甚至因为0.5毫米的间距尺寸而害羞。

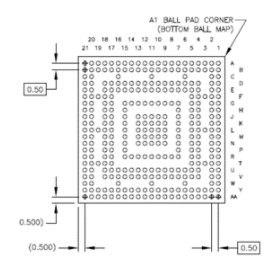

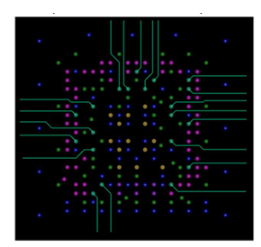

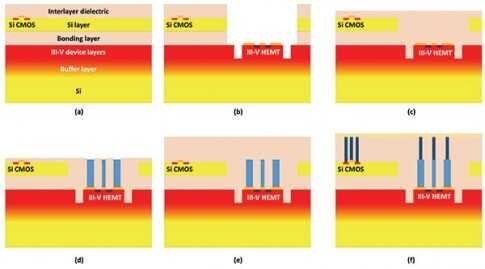

这就是美丽的开始。FCSG325封装建立在0.5 mm间距上,是的,但是它在球栅阵列上也有几个空白区域:

封装的内部区域填充有用于电源和接地的引脚,外环是用户IO和收发器引脚。这意味着,路由用户信号仅通过包的一小部分。

放在这个包上并作为示例列出的几个用例:

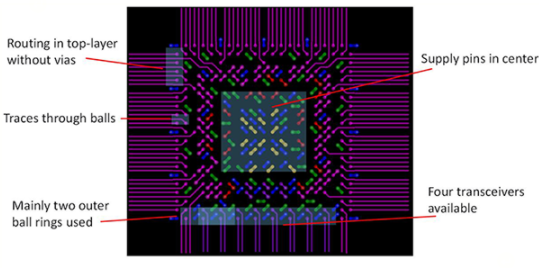

1) 所有引脚的通用布局

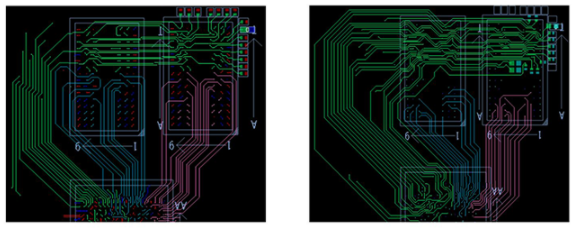

顶层用于从外环路由所有 IO,包括映像底部的收发器。这些信号根本不需要过孔。

底层从中间环接收信号。由于外圈的布线没有过孔,因此不存在障碍物,并且可以轻松带出信号。封装中间显示了用于电源的过孔,以及其独立层的接地。

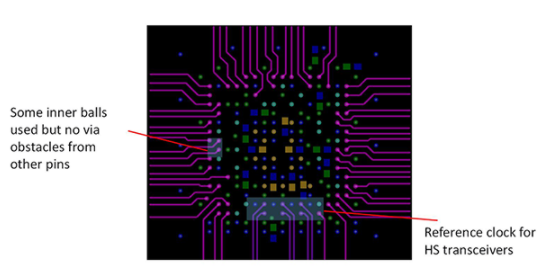

剩下几个引脚,需要第三层,信号很少才能路由出去:

这里使用的过孔为0.1 mm,其余布局可以通过0.8 mm间距的典型规则来实现。不需要埋孔/盲孔。

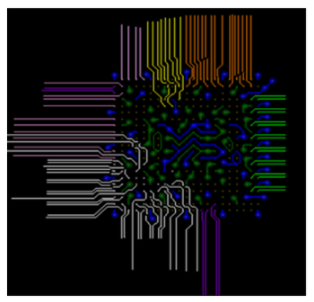

2) DDR4 带 32 位数据路径

FCSG325封装具有两个针对DDR4存储器的预定义建议,允许在FPGA内部进行非常快速和简单的引脚分配。这是灵活性较低的缺点还是好处?显然是一个好处!为DDR4选择优化的引脚排列而没有任何拥塞是一个交互过程。使用预定义的布局将引脚变成SEP(其他人的问题),可以节省您的层数,并节省时间和白发。

DDR4 接口是根据此建议进行布局的,并且仅基于两个信号层进行路由。这两层包括所有 32 个数据和地址/命令行。同样,这里不必使用埋孔/盲孔。

现在,在某些情况下,由于某些侧面限制,此建议的布局可能不起作用。在您必须偏离建议布局的情况下,Microchip提供付费服务,以帮助您或通过设计服务检查您的布局。有关此产品的详细信息,请访问我们的网站。

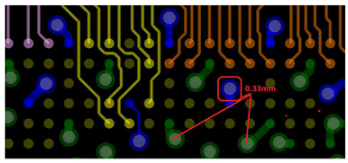

3) 成本优化布局

如果仅使用包外环中的 IO,则可以进行额外的成本优化。该图显示了在顶层向外路由的几个独立接口。这样可以保持封装下方的空白空间,并允许使用直径为0.33 mm的过孔。

放大电源引脚可显示空闲空白空间中较大的过孔。

在所有用例中,走线宽度为4 MIL / 0.1 mm,走线和焊盘之间的距离为3.1 MIL / 0.08 mm。

此包和其他包的布局建议也在此处和此处在线发布。

从本质上讲,这些布局建议对您和您的设计有什么帮助?这些指针向您展示了如何结合两个领域的优势, 小封装间距和经济高效的 PCB 技术,并解决您的空间限制.

审核编辑:郭婷

-

FPGA

+关注

关注

1655文章

22283浏览量

630140 -

soc

+关注

关注

38文章

4514浏览量

227575 -

PCB

+关注

关注

1文章

2264浏览量

13204

发布评论请先 登录

双无线电连接:在物联网应用中实现两全其美

tas5548的工作温度在50到60度以上时有非常明显的爆破杂音,怎么解决?

段码式显示屏和背光电路怎么设计?

MEMS惯性传感器的优势是什么?

动态Flash的可行性

nuc140 ISP下载波特率是否可以改变?

USB Type-C耳机的尴尬:三星不爱、苹果不用

区块链R3首次发布,区块链应用防火墙

大朋E3-C体验 功能全面性价比出众

基于区块链数字令牌技术的石油生产CryptoEnergy项目介绍

使用Google提供的平台实用程序的iPhone的私密性?

两全其美:真正的时间延迟和移相器

两全其美:小尺寸FPGA和高性价比的PCB技术

两全其美:小尺寸FPGA和高性价比的PCB技术

评论