数字低通滤波器模块,做平滑滤波

//*********************************************************************

//

// 'Box' Average

//

// Standard Mean Average Calculation

// Can be modeled as FIR Low-Pass Filter where

// all coefficients are equal to '1'.

//

//*********************************************************************

module box_ave (

clk,

rstn,

sample,

raw_data_in,

ave_data_out,

data_out_valid);

parameter

ADC_WIDTH = 8, // ADC Convertor Bit Precision

LPF_DEPTH_BITS = 4; // 2^LPF_DEPTH_BITS is decimation rate of averager

//input ports

input clk; // sample rate clock

input rstn; // async reset, asserted low

input sample; // raw_data_in is good on rising edge,

input [ADC_WIDTH-1:0] raw_data_in; // raw_data input

//output ports

output [ADC_WIDTH-1:0] ave_data_out; // ave data output

output data_out_valid; // ave_data_out is valid, single pulse

reg [ADC_WIDTH-1:0] ave_data_out;

//**********************************************************************

//

// Internal Wire & Reg Signals

//

//**********************************************************************

reg [ADC_WIDTH+LPF_DEPTH_BITS-1:0] accum; // accumulator

reg [LPF_DEPTH_BITS-1:0] count; // decimation count

reg [ADC_WIDTH-1:0] raw_data_d1; // pipeline register

reg sample_d1, sample_d2; // pipeline registers

reg result_valid; // accumulator result 'valid'

wire accumulate; // sample rising edge detected

wire latch_result; // latch accumulator result

//***********************************************************************

//

// Rising Edge Detection and data alignment pipelines

//

//***********************************************************************

always @(posedge clk or negedge rstn)

begin

if( ~rstn ) begin

sample_d1 <= 0;

sample_d2 <= 0;

raw_data_d1 <= 0;

result_valid <= 0;

end else begin

sample_d1 <= sample; // capture 'sample' input

sample_d2 <= sample_d1; // delay for edge detection

raw_data_d1 <= raw_data_in; // pipeline

result_valid <= latch_result; // pipeline for alignment with result

end

end

assign accumulate = sample_d1 && !sample_d2; // 'sample' rising_edge detect

assign latch_result = accumulate && (count == 0); // latch accum. per decimation count

//***********************************************************************

//

// Accumulator Depth counter

//

//***********************************************************************

always @(posedge clk or negedge rstn)

begin

if( ~rstn ) begin

count <= 0;

end else begin

if (accumulate) count <= count + 1; // incr. count per each sample

end

end

//***********************************************************************

//

// Accumulator

//

//***********************************************************************

always @(posedge clk or negedge rstn)

begin

if( ~rstn ) begin

accum <= 0;

end else begin

if (accumulate)

if(count == 0) // reset accumulator

accum <= raw_data_d1; // prime with first value

else

accum <= accum + raw_data_d1; // accumulate

end

end

//***********************************************************************

//

// Latch Result

//

// ave = (summation of 'n' samples)/'n' is right shift when 'n' is power of two

//

//***********************************************************************

always @(posedge clk or negedge rstn)

begin

if( ~rstn ) begin

ave_data_out <= 0;

end else if (latch_result) begin // at end of decimation period...

ave_data_out <= accum >> LPF_DEPTH_BITS; // ... save accumulator/n result

end

end

assign data_out_valid = result_valid; // output assignment

endmodule

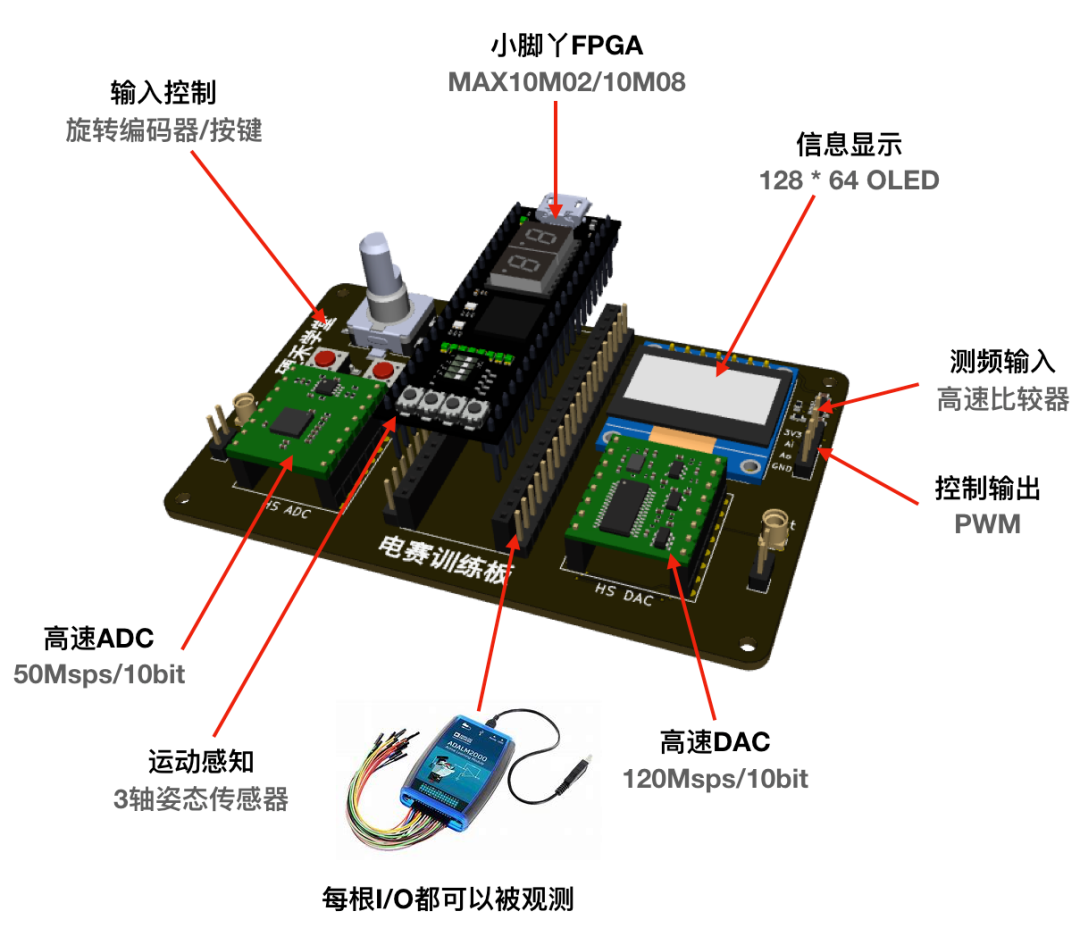

有FPGA的小朋友不妨可以试一下,只需要搭配一颗比较器、一个电阻R、一个电容C,只需要FPGA的两根管脚,你就可以拥有ADC的功能了。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22503浏览量

639279 -

芯片

+关注

关注

463文章

54429浏览量

469377 -

adc

+关注

关注

100文章

7946浏览量

556896

发布评论请先 登录

相关推荐

热点推荐

fpga开发板使用教程之在K7上用Ibert实现基本的GTX测试

测试,而且基本上可以达到不用敲代码就可以完成测试的目的。 下面按步骤,一步一步实现。重点的地方我

发表于 12-31 15:36

•9441次阅读

ADC实现一个IO上挂多个按键

有时候做设计时,我们会遇到外部按键比较多,IO口不够用的情况。这时大部分人会考虑通过其它芯片扩展IO,或者直接换一个IO口足够的MCU。其实,还有个方法可以

发表于 09-01 13:25

•3849次阅读

可以用FPGA做些什么

我刚买了新的NEXYS4 DDR板,我已经安装并使用了Vivado套件。我的问题是我可以用FPGA做些什么?我是一名计算机/电气学生,我之所以采用这种逻辑与实验课是因为我已经参加了我学校提供的常规

发表于 05-05 07:28

我可以用STM32实现什么?为什么使用STM32而不是8051

你问,如何系统地入门学习STM32?本身就是一个错误的问题。假如你会使用8051 , 会写C语言,那么STM32本身并不需要刻意的学习。你要考虑的是, 我可以用STM32实现

发表于 02-25 06:43

用matlab来实现fpga功能的设计

用matlab来实现fpga功能的设计

摘要:System Generator for DSP是Xilinx公司开发的基于Matlab的DSP开发工具?熗?时也是

发表于 01-16 18:10

•1.2w次阅读

编写一个可以用GRUB来引导的简单x86内核

我们将从零开始,动手编写一个可以用GRUB来引导的简单x86内核,该内核会在屏幕上打印一条信息,然后——挂起!

FPGA上可以用一个比较器实现ADC的功能?2

FPGA上可以用一个比较器实现ADC的功能?2

评论