来源:《半导体芯科技》杂志

作者:John Chang, Corey Shay, James Webb, Timothy Chang; ONTO INNOVATION INC

异构集成技术集成了多个来自不同制程与功能各异的芯片来达到更优越的效能。在大尺寸的面板级封装中,现存的步进式曝光机有着最大单一照射场(Exposure Field)尺寸的限制,迫使图形化制程中需要使用多个光罩图形结合来达到更大的封装尺寸,这导致了较低的生产吞吐量,并增加了制造成本。昂图科技的新型JetStep®X500曝光机的每单位照射场最大可达到250mmx250mm,大幅降低了每片基板所需的曝光次数,从而进一步降低了扇出型面板级封装(FOPLP)的制造成本。

高性能电脑,5G,智能手机,数据中心,智能汽车,人工智能与物联网这些终端应用,大部分都需要使用异构集成技术来达到下一世代的效能需求。为了在单个封装中集成更多的芯片,单一封装尺寸将从75mm×75mm成长到150mm×150mm,抑或是更大的尺寸。异构集成是一个重要的技术,引领着我们更接近下一个世代,此世代将各种科技融入了我们的生活之中,不论是智慧型的工厂,或是在城市中穿梭的各种自动驾驶车辆与载具,抑或是将人们更紧密的连接在一起的移动设备和让人们变得更健康的可穿戴设备,等等。

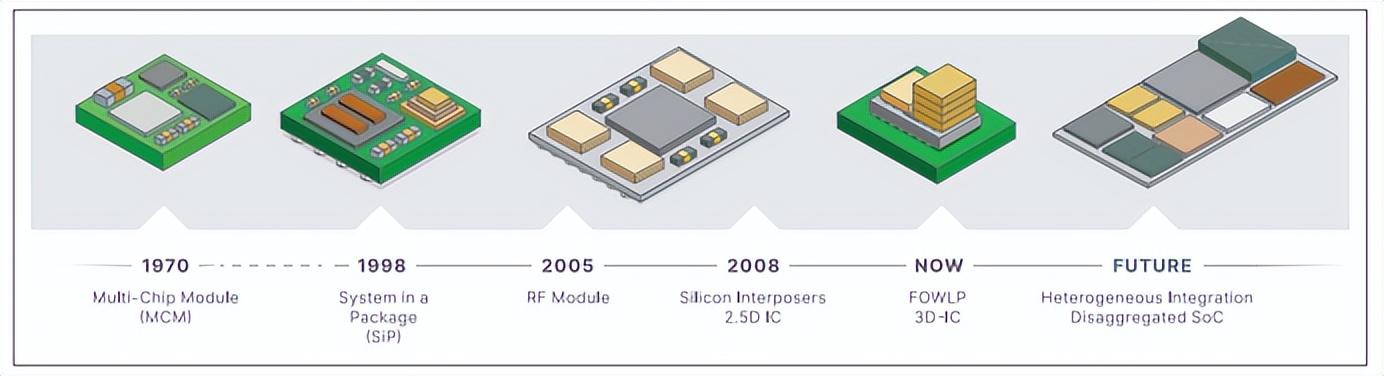

不论如何,为了更接近下一世代,将带来一些对于现存科技的挑战。其中之一便是对于各种终端装置的效能与功能的要求越来越严格。下一世代的异构集成技术,扇出封装技术与面板级封装技术便是常用来达成这些要求的技术,这些要求将需要结合更大的封装尺寸,更小的芯片连结通道与更大的封装基板,为了同时满足这些需求,更严格的套刻(Overlay)规格将会成为封装中光刻制程中主要的挑战之一。(图1)

△图1:异构集成(Heterogenous Integration)结合了多个不同的芯片与组件集成,在单一封装中来达成下一世代的装置效能需求,所以封装尺寸可以预期会有显著的成长。(Source:Cadence)

当重布线层(RDL)一层一层叠加的过程中,或会对封装基板的表面与内部造成不同的应力影响,这些应力的存在将会导致封装基板的形变与翘曲。假如封装基板因为高温,高压与其他制程产生形变与翘曲,该状况将会引起基板上的图形或芯片偏离原本所应当在的位置,并进而影响光刻制程中套刻的结果,而且此情形在越大的基板尺寸上会更加的严峻。当这些图形或芯片偏移在光刻制程中没有被完整的认知并矫正,这最终将会导致严重的套刻误差(Overlay Error)进而影响到产品良率。

与此同时,在不久的将来,为了满足更先进的性能需求,先进封装(Advanced Package,AP)将会需要1µm线宽的制程,而先进基板封装(Advanced IC Substrate,AICS)将会需要3µm线宽的制程,并且套刻预算(Overlay Budget)将会变得更加的紧缩。举例来说,现今的AICS典型的套刻良率(Overlay Yield)只有95%到97%,在更先进的小线宽制程中,我们可以预期套刻良率会更低。

那么,一个极大单位照射场,高分辨率(Extremely Large Exposure Field Fine Resolution)的光刻系统要如何应对这些异构集成所带来的挑战呢?为了更好的了解这类系统的性能,例如昂图科技(ONTO INNOVATION INC.)的JetStep®X500,我们将分析使用光刻系统所收集的图形与芯片的偏移计量与位移检测数据,并结合第三方套刻分析程序(Overlay Analysis Algorithm)去分析并了解偏移图形的误差项(Error Term)与形变组件(DistortionComponents),进而找出一个可行解决方案或是一套光刻策略来克服这些芯片位移误差或是图形形变。为了克服这些种种的挑战,并且同时满足大量量产(HVM)的需求,需要设计一个全新的光刻系统:如昂图科技的JetStep®X500。在此篇研究中,我们成功的展示了如何使用JetStep®X500去克服这些挑战并达到异构集成中严格的套刻需求。

图形拼接(stitching)的挑战

异构集成为了增加更多功能或是达到更高的性能,需要集成多个芯片在75mm×75mm,150mm×150mm或者更大的单一封装之中。针对异构集成的大尺寸封装,现今先进封装(Advanced Packaging)步进式曝光机面临着一个挑战;最大单位照射场尺寸(Exposure Field Size)只有59mm×59mm的这个限制。对大部分的步进式曝光机而言,因为这个单一照射场的尺寸限制,需要使用多个的曝光步骤来完成上述的封装尺寸甚至更大的单一封装尺寸。这种光刻方式就是所谓的“拼接(Stitching)”。

拼接需要多种不同的光罩图形,高精度需求所带来的低错误容许率而且有低产量的缺点,进而导致生产费用的提高。无论如何,将单一照射场尺寸增大(至少大于150mm×150mm)到不须使用拼接的光刻方式可以排除上述提到的问题,并且可以有效的增加产能。

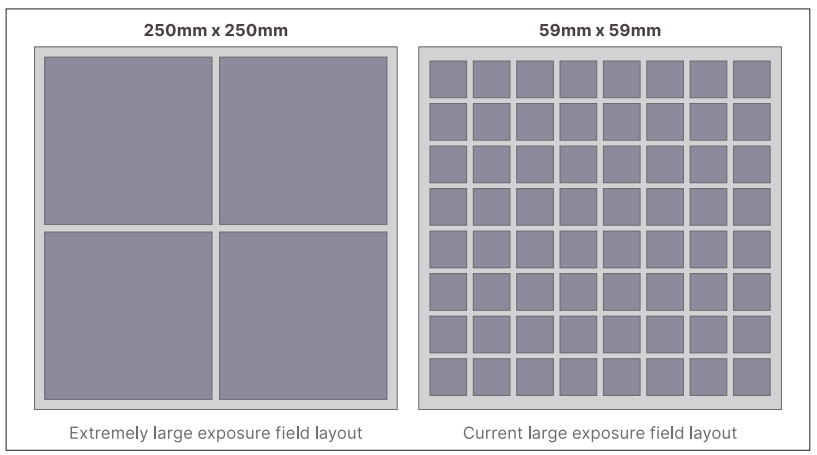

举例来说,现今的先进封装步进式曝光机在使用59mm×59mm的照射场尺寸进行光刻制程,需要64次曝光步骤才能完成一个510mm×515mm基板大小。当我们使用极大照射场曝光机,只需要4个曝光步骤便能完成一个510mm×15mm大小的基板,这实现了不需要拼接光刻方式,并且排除了拼接光刻所需的高精准度与严格的均匀度需求。(图2)

△图2:在510mm×515mm的面板基板上使用极大单位照射场(250mm×250mm)的曝光布局与使用传统单位照射场(59mm×59mm)的曝光布局。如图中所示,使用极大单位照射场的光刻制程只需4次曝光步骤便能完成整片基板,但是使用传统单位照射场(59mm×59mm)的光刻制程需要64次曝光步骤才能完成整片基板。

JetStep®X500所提供的250mm×250mm单位照射场光刻性能允许用户在单一次曝光中完成一个或多个大尺寸封装。相对于传统的单位照射场光刻方式,有着显著性的产能提升。这个极大照射场高分辨率的光刻系统装备了一个可将光罩图形放大2.2倍的投影镜组,这使得250mm×250mm极大尺寸照射场成为可能,并且同时具备了3µm的线宽线距解析性能。另外此系统也具备了±400ppm场放大(Magnifification)补偿性能与±100ppm单向场变体(Anamorphic Magnification)补偿性能,与标准套刻性能可以小于1µm。为了展示该光刻系统的高分辨率性能,我们选择了尺寸为510mm×515mm的ABF(Ajinomoto Build-up Film)+覆铜板(Copper Clad Laminate)以及铜籽晶层(Copper Seed Layer)晶圆为测试载具,并贴合了10µm的干膜光阻来进行3µm分辨率的展示。

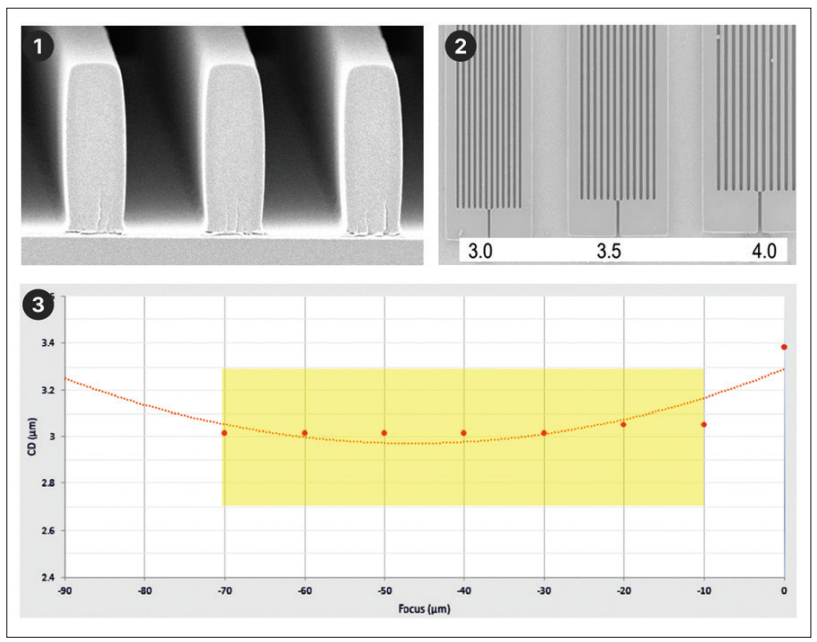

图3所示的测试结果为JetStep® X500仅使用四次曝光去完成该测试载体的光刻制程,用来展示该系统在使用极大照射场的条件下,3µm线宽线距的性能。图3展示了在3µm的线宽线距下,该系统可以提供高达60µm的景深(Depth of Focus)性能,这表示该极大照射场高分辨率的光刻系统是可以达成小线宽线距且大尺寸单一封装的制程,并且同时使用大型尺寸面板为基板来实现大量量产的需求。

△图3:极大照射场高分辨率光刻系统的分辨率性能(Resolution Performance)展示。(1)在铜籽晶层晶圆上,3µm线宽线距基于10µm厚度的干膜光阻上(深宽比1:3.3)的横切面结果。(2)3µm,3.5µm与4µm低密度与高密度图形区域的解析性能结果与比较。(3)3µm线宽在10µm干膜上的泊松曲线(Bossung Curve)分析。X轴为焦距(单位µm),Y轴为关键尺寸(CD,单位µm)。从图中我们可以观察到在510mmx515mm的测试载具上,3µm线宽线距的景深达到了60µm。

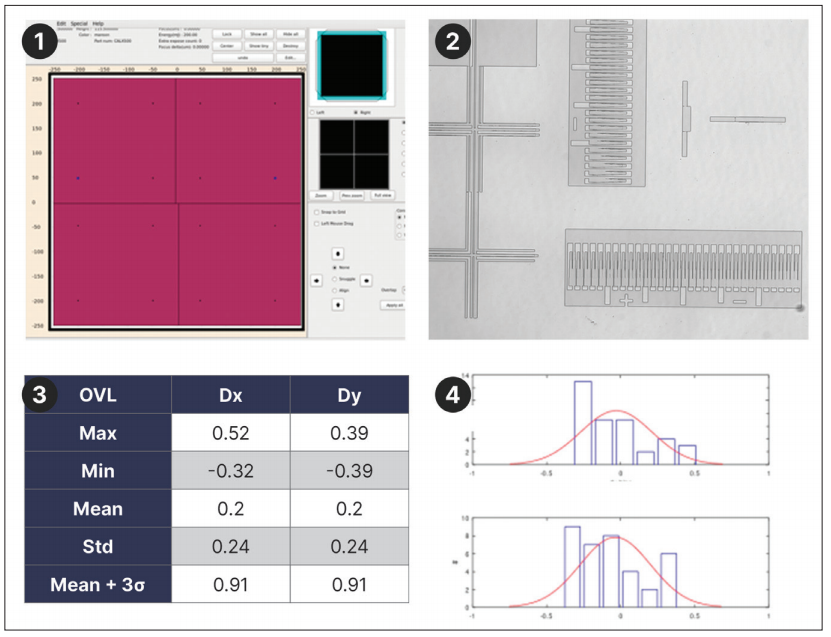

为了测试该光刻系统的标准套刻性能,我们选择了一个510mm×515mm的玻璃基板,并涂布1.4µm厚的液态光阻薄膜为测试载具。在进行第二层套刻层的图形化工艺中,每一次曝光皆会使用区域对准校正(Site by Site Correction),如图4所示。我们将确认第一层图形与第二层图形之间套刻误差去决定最终的套刻结果。套刻误差值是由判读区域中的重叠尺标(Overlapped Verniers)来决定的。

△图4:极大照射场高分辨率光刻系统的标准套刻性能(Standard Overlay Performance)展示。(1)套刻性能展示的曝光布局图。由四个250 mm×250 mm的曝光照 射场来完成510 mm×515 mm的测试载体的光刻工艺,每个曝光场区域包含了四个对准图形来进行曝光时的区域对准效正(Site By Site Correction)。(2)图中 的重叠尺标(Overlapped Vernier)图形是由第一层光刻图形与第二层光刻图形交叠而成,藉由读取重叠尺标可以决定该区域的套刻结果。(3)套刻结果统计表格。(4)X轴套刻误差与Y轴套刻误差分布图。由图中可看到套刻误差平均值接近0,并且没有明显峰值被观察到。

在此套刻性能的展示测试中,每一照射场区域皆包含3×3个量测点,测试载具包含了2×2照射场区域,这代表了我们在测试载具上共量测了36点来决定最终的套刻结果。根据上述的套刻性能结果与分析,极大照射场高分辨率的光刻系统的X轴套刻误差的平均值+3倍标准差0.91µm,而Y轴套刻误差的平均值+3倍标准差的结果为0.91µm。这些数字验证了极大照射场,高解析的光刻系统确实可以达到一个非常极限的套刻数字:小于1µm。而这将是未来先进封装光刻制程的关键之一。

套刻误差矫正

为了展示极大照射场,高分辨率的光刻系统的图形误差矫正性能,我们使用了该系统的场矫正(IntraField Correction)性能与整体矫正(Global Correction)性能来进行这次展示。该光刻系统的整体矫正性能包含了XY方向的平移(Translation),旋转(Rotation),单轴放大(Scale)和正交(Orthogonality)误差矫正,而该系统的场矫正性能包含了XY方向的平移(Translation),旋转(Rotation),场放大(Magnification),辐射歧变(RadialDistortion)和梯形(Trapezoid)误差矫正。结合场矫正与整体矫正性能可以实现单向场变体(Anamorphic Magnifification)与图形歪斜(Skew)误差的矫正性能。该光刻系统装备了反射式对准系统,该系统可以用来认知对准图形在基板上的位置,结合该光刻系统的网格式移动平台的位置信息,我们可以得到该基板上所有图形的误差值。将此图形误差数据结合昂图科技的图形分析算法:StepperMatch和Dolana,我们便可以了解并分析出存在基板中的图形的误差项与形变组成组件。

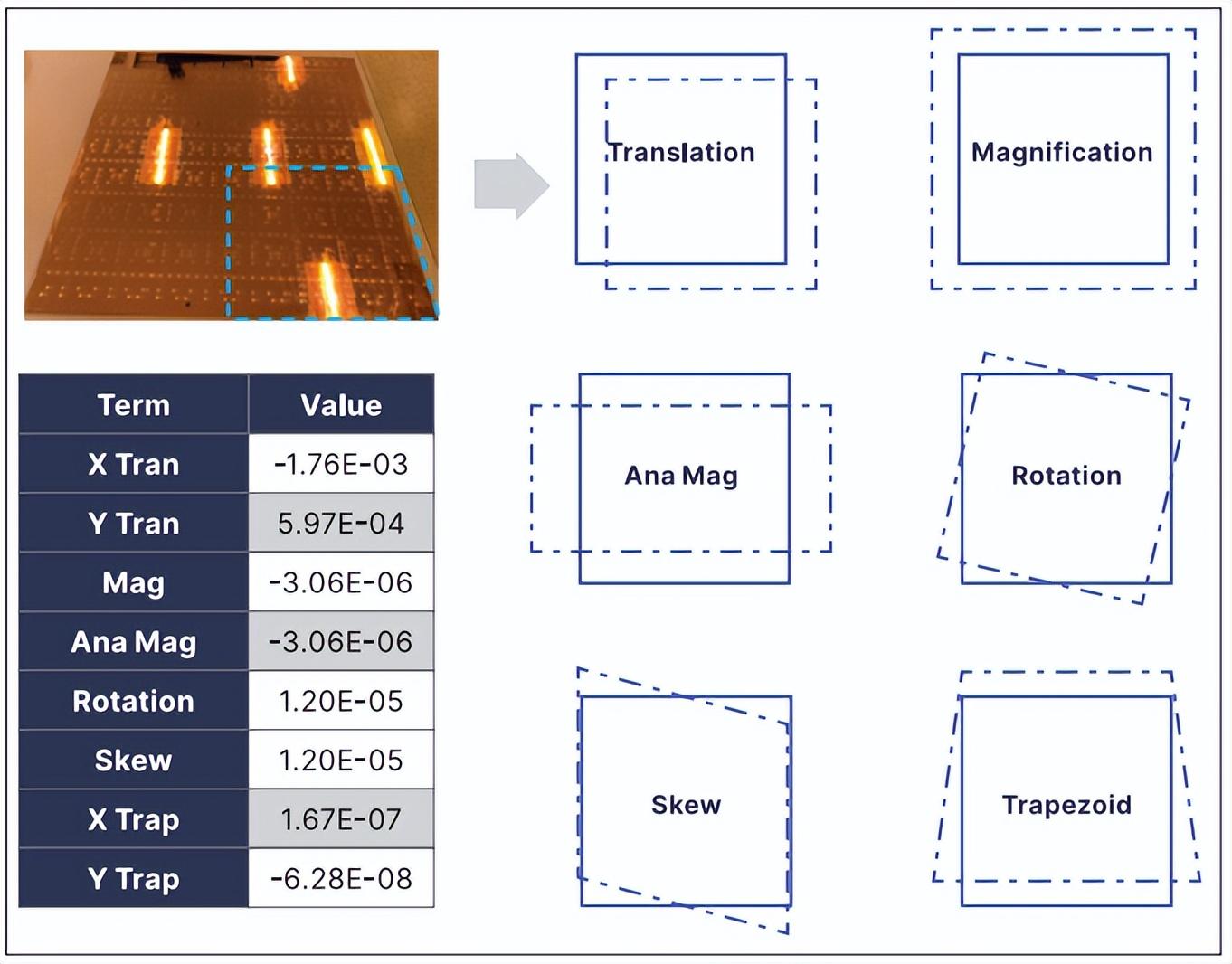

当我们使用StepperMatch与Dolana 分析由光刻系统所收集的图形误差数据,我们可以得到该测试基板或载体中的图形误差项与形变组成组件。如图5所示,我们在测试载体上的单一象限区域发现了平移误差,旋转误差,场放大误差,单向场变体误差,梯形误差和歪斜误差,与单一象限区域不同的是,在测试载体的整体形变中多出了单向桶形变(Anamorphic Pincushion)与辐射歧变(Radial Distortion)形变等。

△图5:在一个510 mm×515mm尺寸的测试载体上,其中一象限(Quadrant)的误差项(Error Term)与形变组成组件(Distortion Component)。在此图表中的数字为分析算法在公式中用来描述每个误差项用的系数。

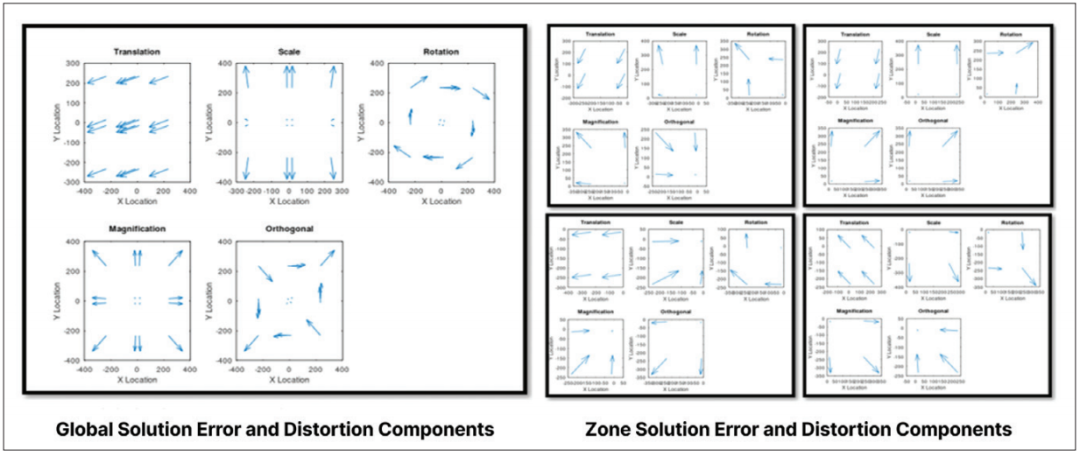

我们发现510mm×515mm的测试载具上的每一象限区域皆拥有不同形式的误差项与形变组件,这代表着整体对准校正(Global Alignment Correction)无法完全的矫正测试载具上存在的位置误差与形变。每个象限区域都需要独特补偿值去矫正他独特的位置误差与形变。这代表了在光刻工艺中,当我们可以针对每个象限区域去矫正该区域独特的形变与误差的补偿时,那我们将能达到更佳的套刻良率。图6展示了整体对准校正的误差形变组件矢量图与区域对准校正的误差形变组件矢量图。这两张图皆是由同一个测试载具的数据中分析得出的。从图6的整体对准校正的平移误差矢量图(Translation Error Vector Map)中我们可以观察到,该误差方向往左下方偏移,但是在使用区域对准校正的第三象限区域的平移误差矢量图,我们可以观察到该误差方向往左上方偏移,这整体对准校正的误差方向是完全相反的,并且在其他的误差项矢量图也可以观察到同样的状况。

△图6:使用整体对准校正(Global Alignment Correction)的误差形变组件矢量图与使用区域对准校正(Site By Site Alignment Correction)的误差形变元件矢量图的比较。

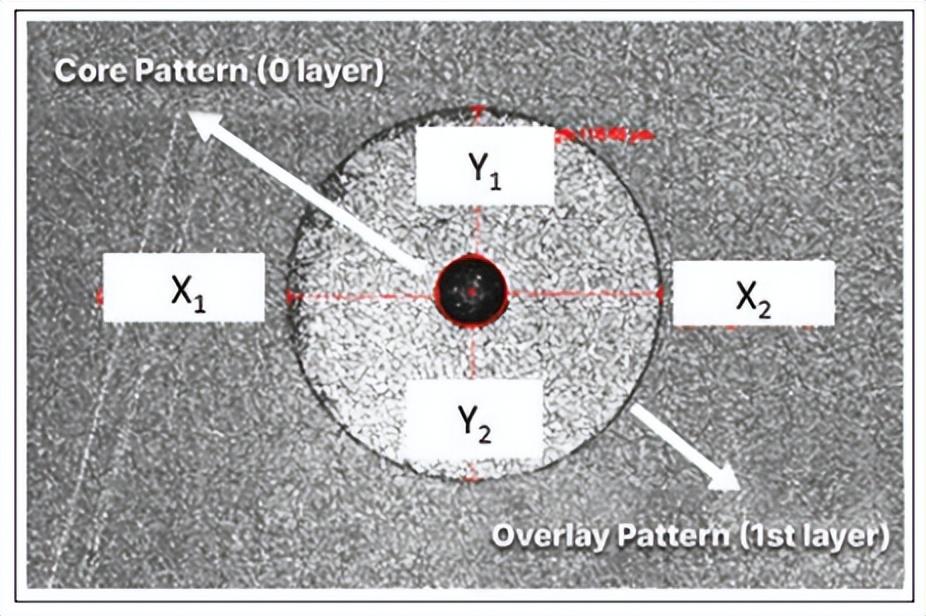

我们在测试载具涂布上了液态光阻,并应用这篇研究中提及的算法去分析测试载具上的误差项与形变组件,并针对测试载具上的每一象限区域算出相对应的补偿矫正值并应用在曝光制程之中,然后再将该测试载具拿去完成整个图形化制程。之后我们使用光学显微镜与相对应的量测软件来量测测试载具上套刻的结果。每个象限区域量测左上,左下,右上,右下,并在中间的区域量测2点,所以每个象限区域皆量测6点,测试载具上共有四个象限区域,所以总共量测24点来决定最终套刻的结果。图7描述了我们如何量测并定义套刻的结果。

△图7:套刻量测方法,用来决定套刻的X方向误差,Y方向误差与矢量。中心的黑点为第0层的核心图形,较大的圆为第一层的套刻图形,X方向误差=X1-X2,Y方向误差=Y1-Y2,套刻误差向量=√(X1-X2)²+(Y1-Y2)²。

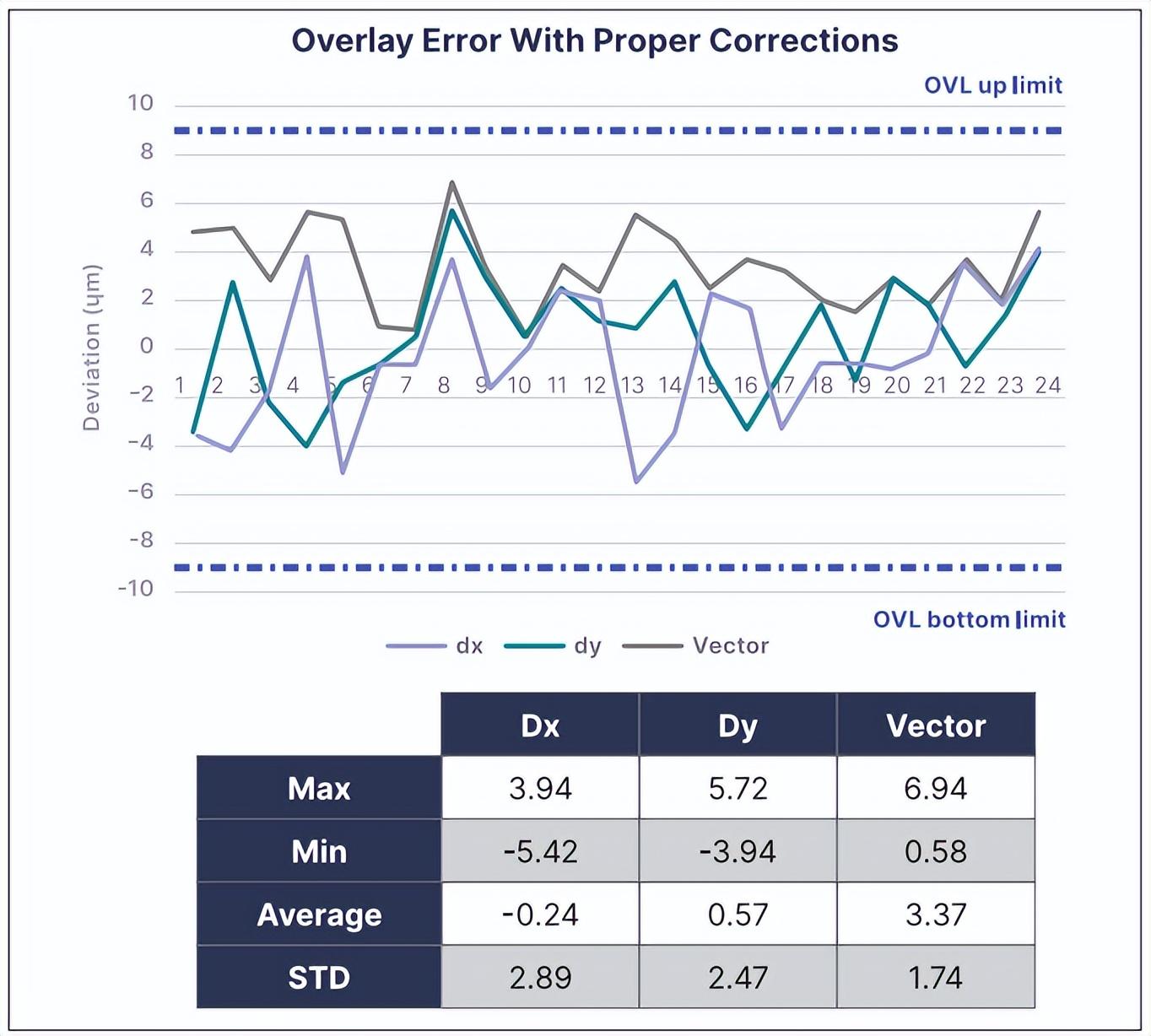

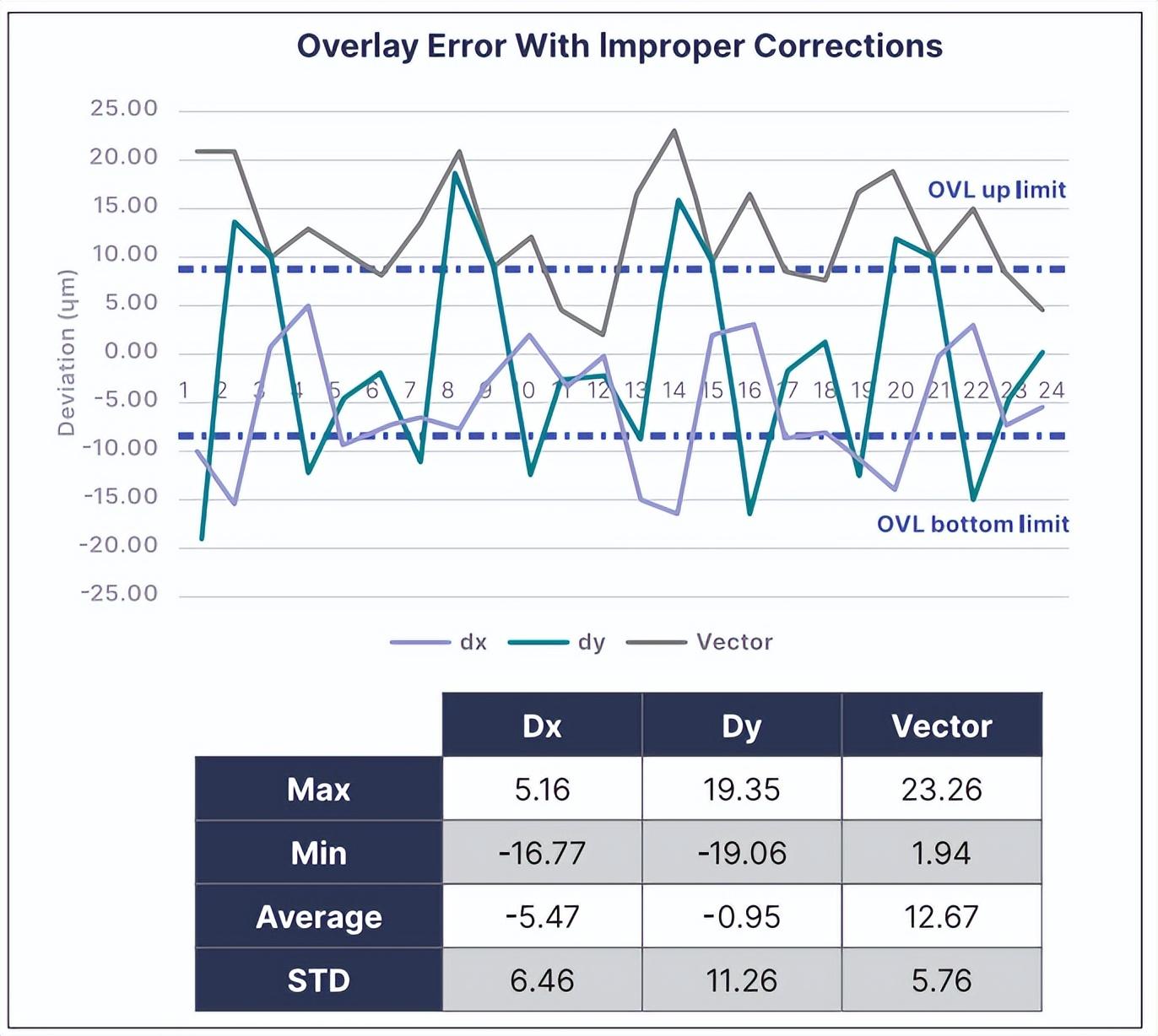

图8显示了测试载具的最终套刻结果。最大的X方向误差为5.42µm,最大的Y方向误差为5.72µm。基于测试载具提供者的数据库,假如图形形变或偏移有正确的被认知并在曝光制程中使用适当的补偿值,我们可以预期最终的套刻结果会小于10µm。根据图中的资料,套刻误差的最大矢量值小于7µm,并且X误差与Y误差值皆小于6µm。这代表了在此展示中,测试载具上的图形形变和偏移皆被有正确的认知出来并且被正确的矫正。假如测试载具上的图形形变和偏移没有使用适当的补偿值矫正的话,那么最终的套刻误差将会高达20µm或者更高,如图9所示。

△图8:使用了适当补偿值与矫正方法的套刻结果。图中单位为µm。最大的套刻误差小于7µm。

根据前述的研究,我们在测试载具上发现了平移(Translation),旋转(Rotation),单轴放大(Scale),场放大(Magnification),单向场变体(Anamorphic Magnification),梯形(Trapezoid)和正交(Orthogonality)误差。这指出了为了得到好的套刻结果。光刻系统能去矫正这些种类的误差项将会是关键之一。

△图9:没有使用适当的补偿和矫正方式的套刻结果。图中单位为µm。最大的套刻误差为23.26µm。这个结果验证了在光刻工艺中,若没有使用适当的补偿值和矫正方式将会导致极大的套刻误差进而影响到光刻制程良率。

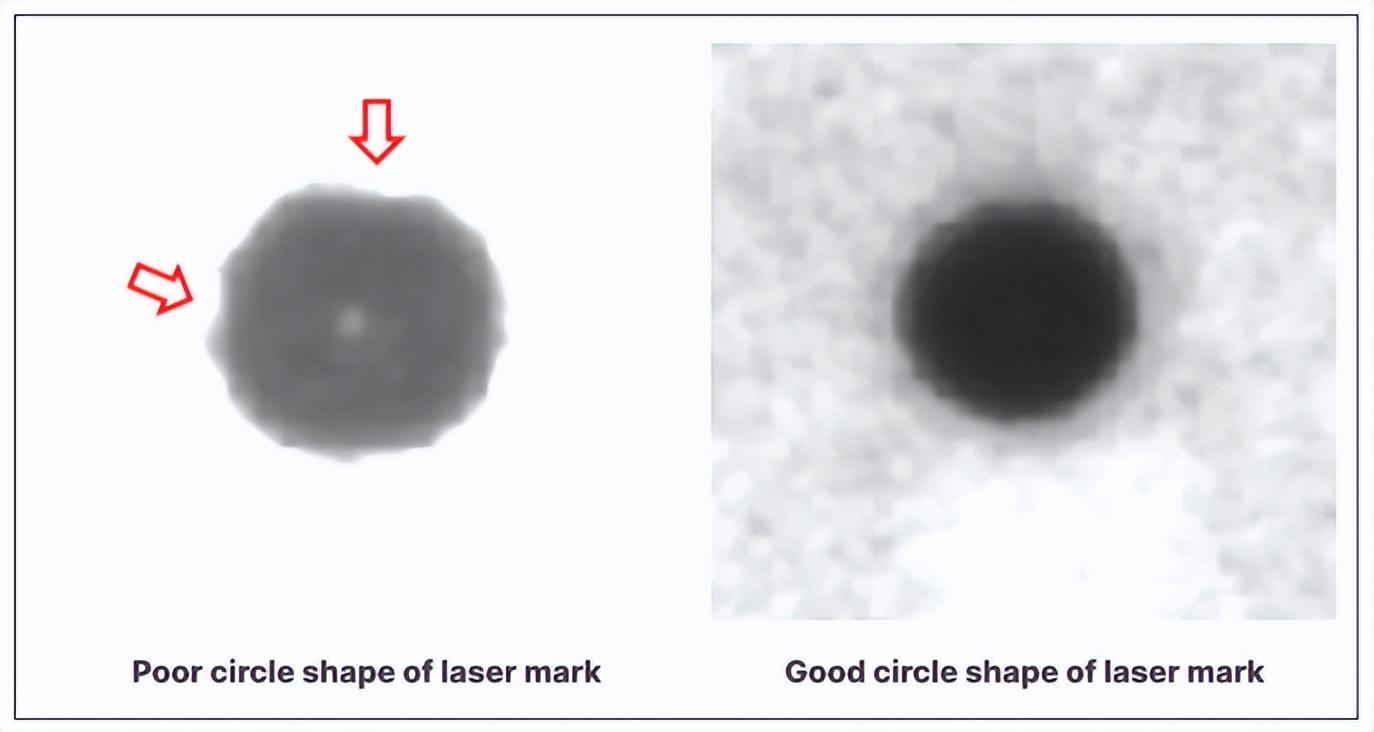

此研究中的测试载具是使用先进基板封装的(AICS)制程所制作出来的,测试载具上的对准图形(Alignment Mark)是经由激光钻孔工艺所制造出来的。由于激光钻孔系统的性能限制,我们可以预期并且也实际观察到由激光钻孔所制作的对位图形有位置精准度较低(Low Accuracy)的问题,且图形形状控制(Shape Control)性能也比较差,而这些问题将会导致最终对位结果的误差。(图10)

△图10:由激光钻孔系统(Laser Drill System)所制造出的对位图形(Alignment Mark)。光刻工艺中的对位图形可能包含一个或多个以上的图形。相较于右边的图形,左边的图形的外观明显有缺角,这将会影响光刻系统中的对位系统的判读并且生成不正确的对位结果(Improper Alignment Solution),进而导致影响到最终的套刻结果与良率。

对位结果的误差会进一步影响到套刻误差的结果。即使光刻系统中的对位系统非常精准的认知出对位图形,根据我们的研究,仍然会有一定的对位误差存在,为了更进一步地达到更好的套刻结果,这个问题必须被克服。

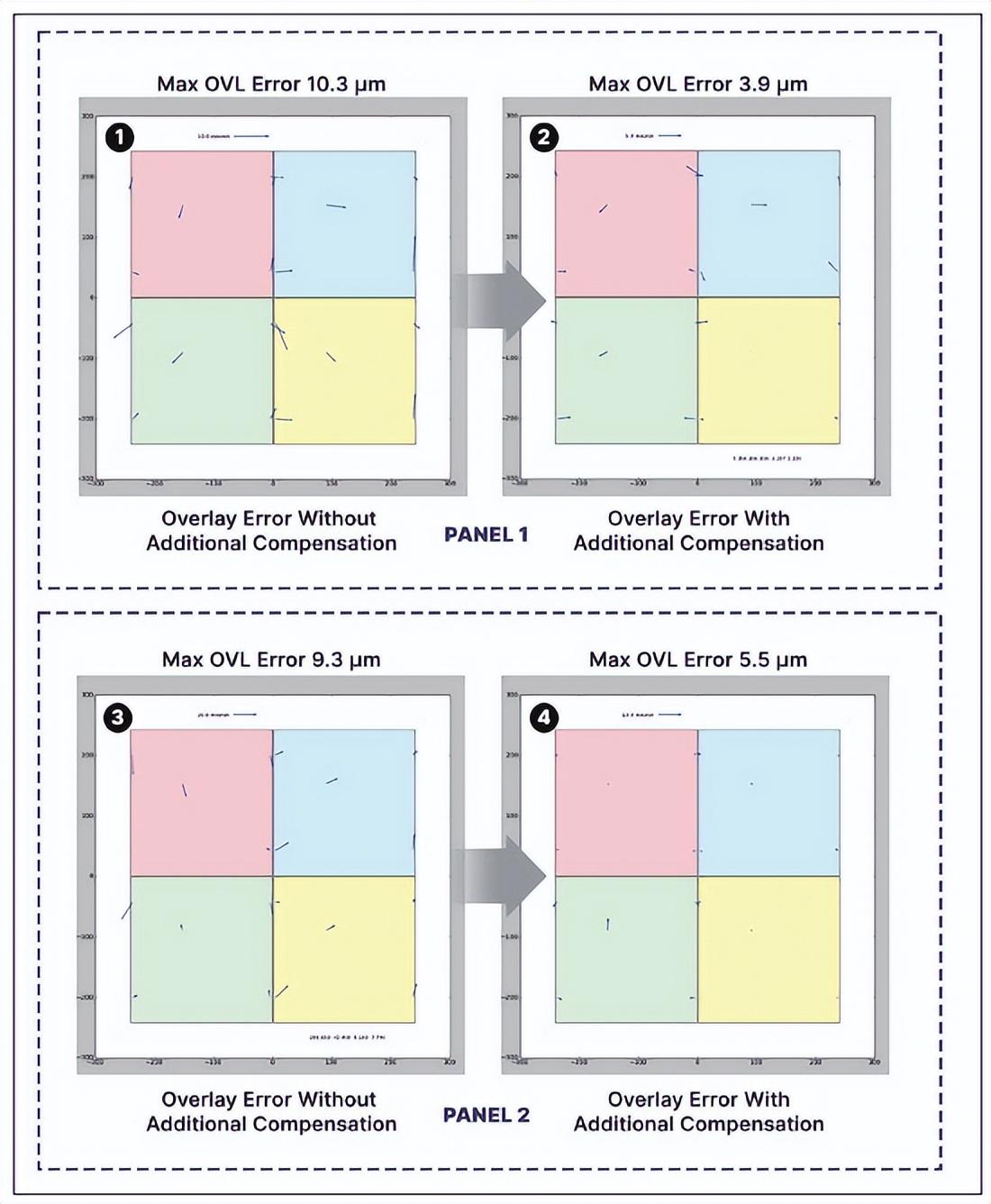

针对上述的对位结果误差,我们发现额外的象限区域补偿(Additional Zone Compensation)可以有效的解决这个情形。为了更好的了解这个情形,我们使用了昂图科技所开发出的套刻图形分析算法来分析并预测当我们使用了额外的象限区域补偿后的套刻结果。此算法是专用来分析套刻误差中可被补偿的误差项(Correctable Term),并且预测矫正后的结果。

在将可补偿的误差项移除后,该算法将可以精准的预测最终的套刻结果。图11的左图是未被补偿前的套刻结果,而右图是补偿后的最终套刻结果,根据该算法的预测,经过额外的区域补偿后,测试载具1和测试载具2上最大的套刻误差将会降低3.9µm和5.5µm,如同图11所示。

△图11:使用额外的区域域补偿与不使用额外的曲域补偿的套刻误差比较。根据算法的预测,使用额外的单区域补偿可以有效地降低最终套刻的误差。

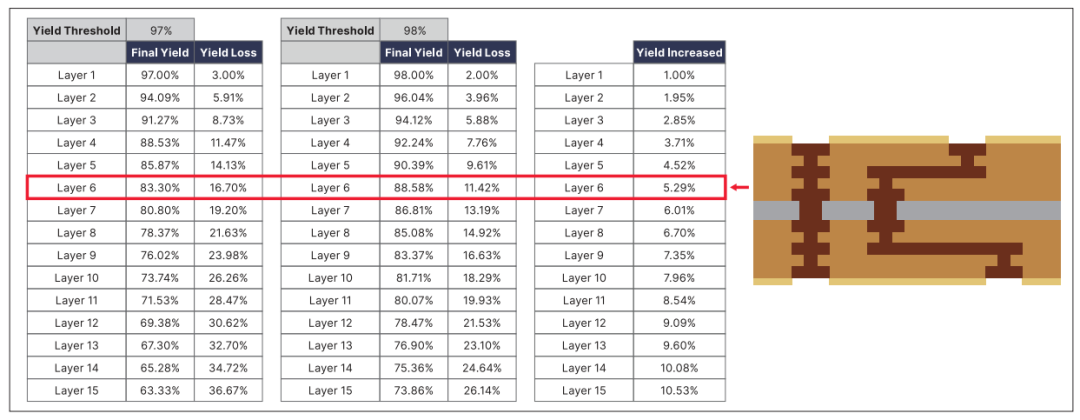

根据异构集成与高效能的需求,在不久的将来,先进基板(Advanced IC Substrate)封装将需要3µm的先进制程来迎合需求。而因应这些先进的制程,也将会需要更严格的套刻规格。在先进基板封装的光刻制程中,传统的每个重布线层的套刻良率为95%到97%(或者以上)。表1中,左边的表格是原始套刻良率的累积良率损失,中间的表格为改善后的套刻良率与累积良率损失,右边的表格则是累积良率的改善。以表1中红框中为例子,我们将97%设为原始套刻良率,改善后的套刻良率为98%,在一个六层结构的封装中,仅仅1%的套刻良率改善便可以达到5.29%累积良率的改善。当然这只是一个大概的估算,但是从此估算便可以得知改善套刻良率是整体封装良率来说是多么的重要。

△表1.光刻制成的套刻良率估算表。在此表格中,原始的套刻良率被设定为97%,在一个六层结构的封装中,光刻制程最大将会造成16.7%的良率损失。而改善后的套刻良率我们将其设定在98%,光刻制程最大将会造成11.42%的良率损失。而从表格得知,在一个六层结构的封装中,1%的光刻制程的套刻良率改善便可以达到5.29%最终良率的改善。

结论

基于此篇研究中的资料我们可以得知,一个极大照射场,高分辨率的光刻系统是可以实现3µm的分辨率并且其标准套刻性能可以达到1µm(平均值+3倍标准差)的。研究中也验证了极大照射场,高分辨率的光刻系统是有性能可以矫正一个510mm×515mm的ABF+CCL基板上的图形偏移与误差进而达到良好的套刻结果。根据此篇研究的分析与讨论中得知,正确认知并矫正基板中误差项与图形形变,使用区域对准校正方法并且加上额外的区域补偿将是在扇出型面板级封装中得到最佳的套刻结果的重要关键。

在不久的将来,随着光刻工艺越来越小的分辨率需求,套刻的规格也会变的越来越严格,在异构集成的封装工艺中,套刻的控制将会变得越来越重要,期许此篇研究可以给用户们提供一个方向,让他们可以克服越来越加严格的套刻需求。

鸣谢

作者特别要感谢David Giroux,John Kennedy和Karie Li在软件与算法上的帮助,Casey Donaher和Perry Banks在光刻系统的技术支持,Paul Sun和Jeremy Zhang在光刻制程中的帮助。同时感谢JetStep®X500项目的所有成员们。

审核编辑:汤梓红

-

芯片

+关注

关注

447文章

47788浏览量

409117 -

封装

+关注

关注

123文章

7278浏览量

141096 -

分辨率

+关注

关注

2文章

989浏览量

41564 -

光刻

+关注

关注

7文章

291浏览量

29888

发布评论请先 登录

相关推荐

昂图科技的极大尺寸照射场高分辨率光刻系统克服了FOPLP图形形变挑战

昂图科技的极大尺寸照射场高分辨率光刻系统克服了FOPLP图形形变挑战

评论