您曾设计过具有分数频率合成器的锁相环(PLL)吗?这种合成器在整数通道上看起来很棒,但在只稍微偏离这些整数通道的频率点上杂散就会变得高很多,是吧?如果是这样的话,您就已经遇到过整数边界杂散现象了 —— 该现象发生在载波的偏移距离等于到最近整数通道的距离时。

例如,若是鉴相器频率为100MHz,输出频率为2001MHz,那么整数边界杂散将为1MHz的偏移量。在这种情况下,1MHz还是可以容忍的。但当偏移量变得过小,却仍为非零值时,分数杂散情况会更加严重。

采用可编程输入倍频法来减少整数边界杂散

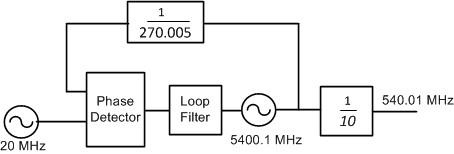

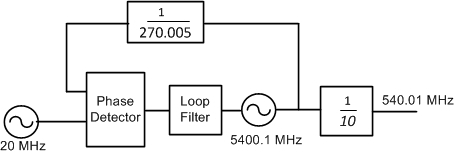

可编程倍频器的理念是让鉴相器频率发生位移,这样压控振荡器(VCO)频率就能远离整数边界。考虑一下用20MHz的输入频率生成540.01MHz的输出频率,如图1所示。该器件具有一个输出分频器(在VCO之后),但输出频率和VCO频率都接近20MHz的整数倍。这种设置将迫使任何PLL产生分数杂散。

图1:整数边界杂散示例

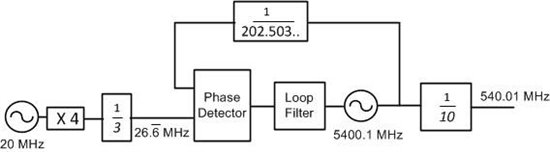

如果该器件具有一个可编程输入倍频器,那么图2中所示的配置就是可行的。

图2:用可编程倍频器来避开整数边界

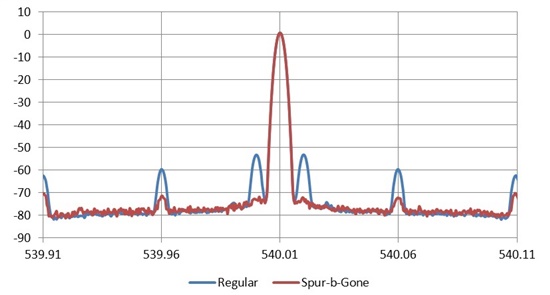

图3展示了内部倍频器的神奇效果。当然,整数边界杂散有多种发生机制,很难完全消除它们。但这种方法可减少整数边界杂散及其产生的其它杂散。

图3中的“杂散消失”路径展示了使用该可编程倍频器的效果。100kHz频率下的整数边界杂散大约减少了9dB,同时还大大减少了50kHz和10kHz频率下的其它杂散。

图3:使用和不用可编程倍频器时的杂散比较

本文中列举的示例都采用了TI的LMX2571合成器 —— 该器件包含一个无需外部组件的可编程倍频器。此外,这款合成器还具有39mA的电流消耗、-231dBc/Hz的PLL相位噪声优值以及10-1344MHz的连续输出频率范围。它能支持陆地移动无线电、软件定义无线电和无线麦克风等应用。

审核编辑:郭婷

-

振荡器

+关注

关注

28文章

4195浏览量

143198 -

频率合成器

+关注

关注

5文章

368浏览量

33900 -

pll

+关注

关注

6文章

991浏览量

138410

发布评论请先 登录

杂散相关问题解答

详解频率合成器高性能架构的实现

改善分数分频锁相环合成器中的整数边界杂散状况

分数频率合成器的锁相环(PLL)偏离整数通道的频率点杂散问题

改善分数分频锁相环合成器中的整数边界杂散状况

改善分数分频锁相环合成器中的整数边界杂散状况

评论