现代接收器系统对更高容量和更多数据吞吐量的需求不断增加。我们必须拥有高采样率数据转换器和高动态范围系统。一些模数转换器(ADC)架构确实实现了非常高的采样率,但没有最佳的信噪比(SNR)。其他器件可实现非常好的SNR,但其采样率有限。没有一个内核ADC器件同时满足高采样速率和动态范围的要求。

交错解决了这个问题。交错将多个低采样速率转换器组合在一起,以创建一个采样速率较高的转换器。每个转换器的时钟源都有延迟,因此信号采样时间略有不同。样本在输出端组合成一个数据流。

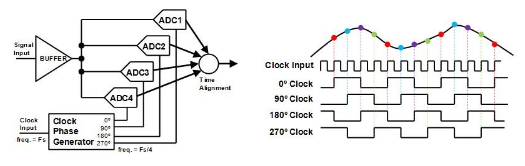

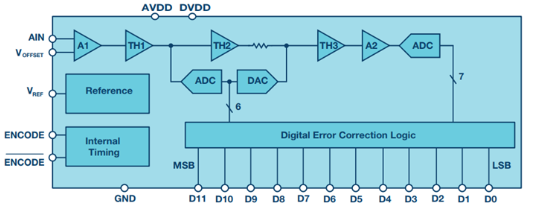

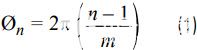

图1:四路交错框图和时序图

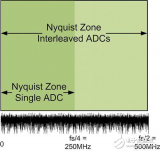

图1所示为四路交错式ADC示例。四个转换器中的每一个都以相同的速率计时。时钟的相位相对于每个转换器偏移90度。时序图说明了时钟边沿的延迟如何在不同时间对模拟信号进行采样。一旦数据在输出端合并,数据流的样本数是一个转换器的四倍。这看起来像一个采样速度是四倍的转换器。复合SNR性能大致相当于单个内核的性能。

有一个问题:使用多个转换器会增加功耗。此外,由于模拟电路的缺陷,小误差会导致交错杂散。这些交错杂散会影响整体无杂散动态范围(SFDR)。

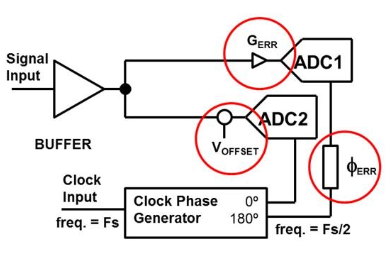

模拟误差主要表现在三个方面,如图2所示。直流失调失配会改变转换器之间的相对共模,而增益和时钟相位对齐误差会导致信号采样位置不精确。

图 2:交错式 ADC 中的误差源

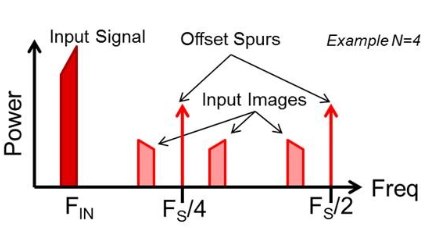

这些误差转化为捕获频谱中的杂散产物。失调误差会引入离散杂散音。杂散的数量取决于交错内核的数量 (N)。离散交错杂散(ILS)频率位置相对于采样速率(Fs)求出,公式1表示:

他们n= Fs*n/N 其中 n = 1, 2, ...N-1 (1)

对于四路交错式ADC,交错杂散位于Fs/4和Fs/2。增益和时钟相位的信号相关误差产生以上述离散频率位置为中心的图像。图3显示了四路交错器件的交错杂散频谱性能。

图 3:四核器件的交错杂散

当然,这些虚假产品是不可取的。在同一芯片上制造的ADC内核本质上会很好地匹配,但它们不会是完美的。需要校准才能获得良好的SFDR性能,通过模拟调整或在前景或背景中进行数字调整来实现。前台校准要求器件停止处理数据,同时校准例程优化性能。后台校准在ADC运行时不断更新调整,使其永远不会离线。

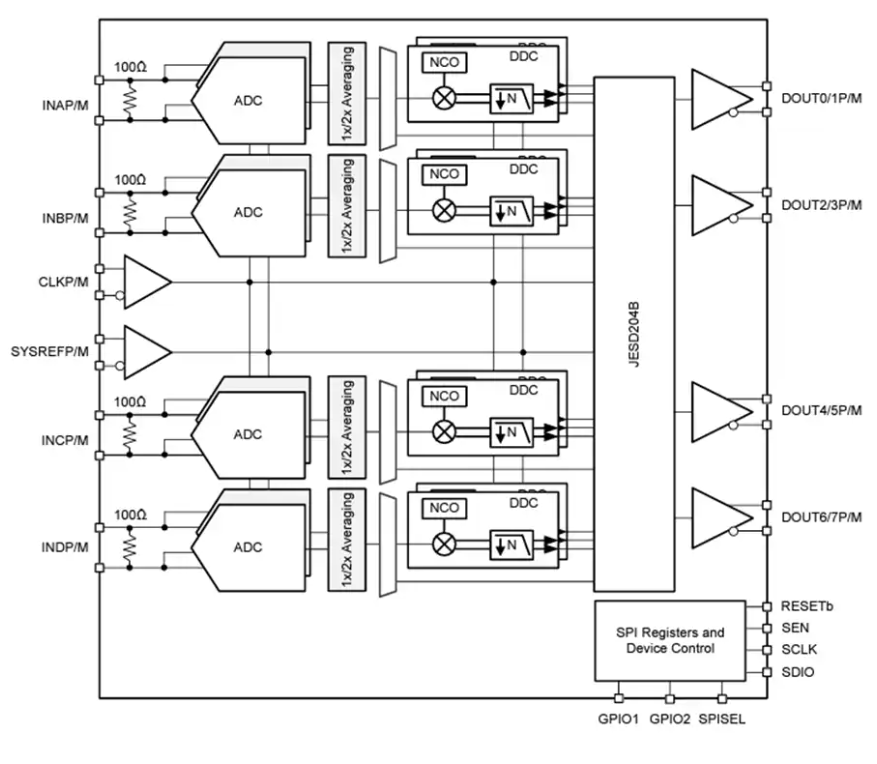

ADC12J4000 ADC使用四个交错内核来实现4GSPS输出采样速率。该器件提供两种交错校正选项。前台校准使采样脱离,并在内核修整时保持输出数据静态。根据校准模式和采样率,此过程可能需要数十毫秒才能完成。如果无法接受离线,则器件具有背景校准模式,其中第五个内核插入混音中。当一个内核脱机校准时,其他四个内核正在正常进行。然后,新校准的内核无缝联机,而另一个内核关闭以进行校准。此过程重复,而不会中断输出。

在室温下,前景校正通常可以使交错杂散保持在-70 dBc以上。ADS54J60 是一款双通道 ADC,每通道使用四个交错内核来实现 1GSPS 输出采样速率。该转换器采用专有的数字交错校正模块来调整内核不平衡。此校正方案始终在后台工作,因此输出数据流永远不会中断。该方案可实现优于-80 dBc的校正。

审核编辑:郭婷

-

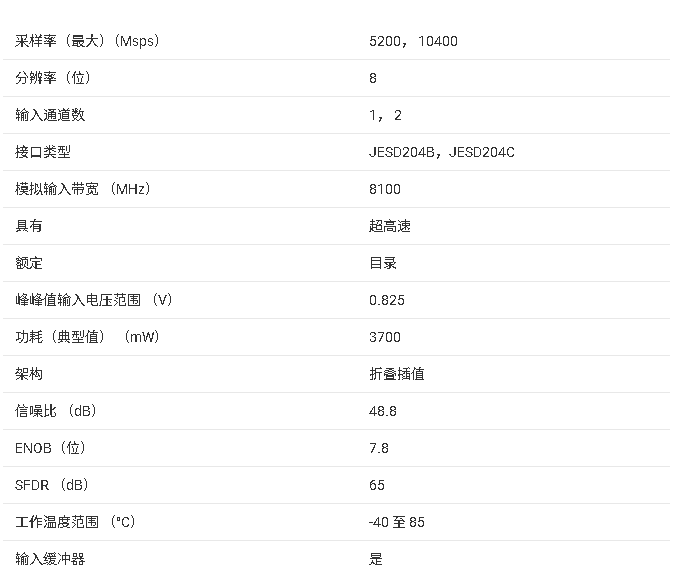

接收器

+关注

关注

15文章

2637浏览量

76307 -

adc

+关注

关注

100文章

7380浏览量

553741 -

RF

+关注

关注

66文章

3196浏览量

171055

发布评论请先 登录

拓展一些关于交错ADC的观点

RF采样ADC的优势

RF采样ADC在系统设计中具有优势

ADC12D1800RF一款RF采样GSPS ADC数据表

ADC12D500RF, ADC12D800RF 12位1.6/1.0 GSPS RF采样ADC数据表

德州仪器ADC34RF55:14位3GSPS RF采样ADC技术解析

ADC12D1000RF 12 位高采样率 RF 采样 ADC 技术文档总结

ADC12D500RF 12 位中高速 RF 采样 ADC 技术文档总结

RF采样:交错构建更快的ADC

RF采样:交错构建更快的ADC

评论