本文以AWR1642为例,介绍了在AWR1642 ES2.0 EVM上基于mmWave SDK 2.1的mmw demo下如何修改代码来改变L3 RAM分布的具体流程和步骤。

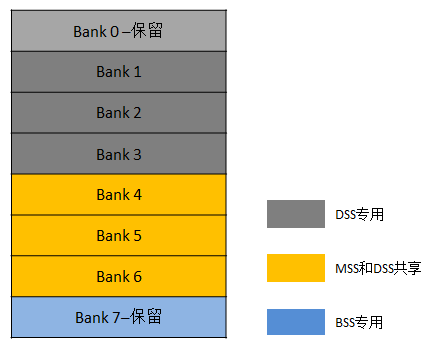

IWR1642/AWR1642上总共有768KB L3 RAM。这768KB L3内存按照128KB一个bank,分成了6个bank(bank6~bank1),其中bank1到bank3是专门给DSS使用的。剩下的3个bank可以配置为DSS,R4F TCMA,R4F TCMB,或者为BSS使用。用户可以根据自己软件的需要,修改各个模块使用L3 RAM的大小。默认代码下所有共享的3个L3 bank都是给DSS使用的。本次测试示例修改了其中一个共享的L3 RAM bank(128KB)给MSS的TCMA使用。

图1 IWR1642/AWR1642 L3 RAM

在mmWave SDK 2.1里面提供了一个方便更改L3 RAM map的接口,环境变量MMWAVE_SDK_SHMEM_ALLOC。但是在某些情况可能仅仅修改这个环境变量还不充足。下面步骤里有具体说明。

| MMWAVE_SDK_SHMEM_ALLOC | ||||

| Bit | 31~24 | 23~16 | 15~8 | 7~0 |

| 含义 | 分配给BSS使用的L3 RAM bank数量 | 分配给MSS TCMB使用的L3 RAM bank数量 | 分配给MSS TCMA使用的L3 RAM bank数量 | 分配给DSS使用的L3 RAM bank数量(包含DSS专用的bank数) |

表1环境变量MMWAVE_SDK_SHMEM_ALLOC的定义

步骤一:以本次测试示例为例,需要修改C:timmwave_sdk_02_01_00_04packagesticommonmmwave_sdk_xwr16xx.mak里环境变量MMWAVE_SDK_SHMEM_ALLOC的定义。但是里面并没有本次测试需要的增加一个bank给MSS TCMA的代码,所以需要添加相关代码。因为一个bank给MSS TCMA,所以MMWAVE_SDK_SHMEM_ALLOC 的bit[15:8]=1,bit[15:8]=5。例如下面黄底加粗部分代码。

MMWAVE_SDK_SHMEM_ALLOC=0x00000105

ifeq ("$(MMWAVE_SDK_SHMEM_ALLOC)", "")

SHMEM_ALLOC = 0x00000006 # default case

MMWAVE_L3RAM_NUM_BANK = 6

MMWAVE_SHMEM_TCMA_NUM_BANK = 0

MMWAVE_SHMEM_TCMB_NUM_BANK = 0

else ifeq ($(MMWAVE_SDK_SHMEM_ALLOC), 0x00000006) # default case

SHMEM_ALLOC = $(MMWAVE_SDK_SHMEM_ALLOC)

MMWAVE_L3RAM_NUM_BANK = 6

MMWAVE_SHMEM_TCMA_NUM_BANK = 0

MMWAVE_SHMEM_TCMB_NUM_BANK = 0

else ifeq ($(MMWAVE_SDK_SHMEM_ALLOC), 0x00000105) # more MSS TCMA

SHMEM_ALLOC = $(MMWAVE_SDK_SHMEM_ALLOC)

MMWAVE_L3RAM_NUM_BANK = 5

MMWAVE_SHMEM_TCMA_NUM_BANK = 1

MMWAVE_SHMEM_TCMB_NUM_BANK = 0

else ifeq ($(MMWAVE_SDK_SHMEM_ALLOC), 0x00000204) # scenario where more MSS code space is needed

SHMEM_ALLOC = $(MMWAVE_SDK_SHMEM_ALLOC)

MMWAVE_L3RAM_NUM_BANK = 4

MMWAVE_SHMEM_TCMA_NUM_BANK = 2

MMWAVE_SHMEM_TCMB_NUM_BANK = 0

else ifeq ($(MMWAVE_SDK_SHMEM_ALLOC), 0x00010005) # scenario where more MSS .bss space is needed

SHMEM_ALLOC = $(MMWAVE_SDK_SHMEM_ALLOC)

MMWAVE_L3RAM_NUM_BANK = 5

MMWAVE_SHMEM_TCMA_NUM_BANK = 0

MMWAVE_SHMEM_TCMB_NUM_BANK = 1

else ifeq ($(MMWAVE_SDK_SHMEM_ALLOC), 0x00010104) # scenario where more MSS code and MSS .bss space is needed

SHMEM_ALLOC = $(MMWAVE_SDK_SHMEM_ALLOC)

MMWAVE_L3RAM_NUM_BANK = 4

MMWAVE_SHMEM_TCMA_NUM_BANK = 1

MMWAVE_SHMEM_TCMB_NUM_BANK = 1

else

$(error Invalid SHMEM_ALLOC setting! Please check the environment variable MMWAVE_SDK_SHMEM_ALLOC.)

endif

修改了MMWAVE_SDK_SHMEM_ALLOC的定义,在代码里面有三处相关代码会连动修改。

1. 一个是link文件里对L3段大小的定义,以本例子为例,是C:timmwave_sdk_02_01_00_04packagestiplatformxwr16xx目录下的cmd文件。

r4f_linker.cmd

PROG_RAM (RX) : origin=0x00000100 length=0x0003FF00+(MMWAVE_SHMEM_TCMA_NUM_BANK*MMWAVE_SHMEM_BANK_SIZE) –》本例为例修改后length=0x0005FF00

DATA_RAM (RW) : origin=0x08000000 length=0x00030000+(MMWAVE_SHMEM_TCMB_NUM_BANK*MMWAVE_SHMEM_BANK_SIZE) –》本例为例修改后length=0x00030000

L3_RAM (RW) : origin=0x51000000 length=MMWAVE_L3RAM_NUM_BANK*MMWAVE_SHMEM_BANK_SIZE) –》本例为例修改后length=0xA0000

注意:为了验证测试,在测试代码中单独把扩展出来的一块分出来,便于测试代码加入。在实际应用的代码里面不需要对r4f_linker.cmd文件做修改。

r4f_linker.cmd修改为:

MEMORY{

…

PROG_RAM (RX) : origin=0x00000100 length=0x0003FF00

PROG_RAM2 (RX): origin=0x00040000 length=0x0001FFFF

…

}

SECTIONS{

…

my_section : {} > PROG_RAM2

}

c674x_linker.cmd

#define MMWAVE_L3RAM_SIZE (MMWAVE_L3RAM_NUM_BANK*MMWAVE_SHMEM_BANK_SIZE) –》本例为例MMWAVE_L3RAM_SIZE 值为0xA0000

…

MEMORY

{

PAGE 0:

…

L3SRAM: o = 0x20000000, l = MMWAVE_L3RAM_SIZE

…

PAGE 1:

L3SRAM: o = 0x20000000, l = MMWAVE_L3RAM_SIZE

}

…

2. 一个是sys_common头文件里和L3, TCMA and TCMB 大小的相关定义。以本文为例是C:timmwave_sdk_02_01_00_04packagesticommonsys_common_xwr16xx_mss.h文件。相关内如如下。

#define SOC_XWR16XX_MSS_SHMEM_TCMA_NUM_BANK MMWAVE_SHMEM_TCMA_NUM_BANK

#define SOC_XWR16XX_MSS_SHMEM_TCMA_SIZE MMWAVE_SHMEM_TCMA_NUM_BANK*MMWAVE_SHMEM_BANK_SIZE /* Extended on Share Memory */

#define SOC_XWR16XX_MSS_TCMA_SIZE MMWAVE_SHMEM_TCMA_NUM_BANK*MMWAVE_SHMEM_BANK_SIZE+0x40000U

#define SOC_XWR16XX_MSS_SHMEM_TCMB_NUM_BANK MMWAVE_SHMEM_TCMB_NUM_BANK

#define SOC_XWR16XX_MSS_SHMEM_TCMB_SIZE MMWAVE_SHMEM_TCMB_NUM_BANK*MMWAVE_SHMEM_BANK_SIZE /* Extended on Share Memory */

#define SOC_XWR16XX_MSS_TCMB_SIZE MMWAVE_SHMEM_TCMB_NUM_BANK*MMWAVE_SHMEM_BANK_SIZE+0x30000U /* Extended on Share Memory + Default 192KB */

#define SOC_XWR16XX_MSS_L3RAM_NUM_BANK MMWAVE_L3RAM_NUM_BANK

#define SOC_XWR16XX_MSS_L3RAM_SIZE MMWAVE_L3RAM_NUM_BANK*MMWAVE_SHMEM_BANK_SIZE

3. 第三个是在ccsdebug和mmw demo的makefile文件里的相关定义。

C:timmwave_sdk_02_01_00_04packagestiutilsccsdebugmakefile

all: mssCCSDebug dssCCSDebug

@echo 'Built the CCS Debug MSS & DSS. Preparing the METAIMAGE BIN ...'

@$(GENERATE_METAIMAGE) $(CCS_DEBUG_BIN) $(SHMEM_ALLOC) $(CCS_DEBUG_MSS_OUT) $(XWR16XX_RADARSS_IMAGE_BIN) $(CCS_DEBUG_DSS_OUT)

@$(GENERATE_HS_METAIMAGE) $(CCS_DEBUG_SECURE_BIN) $(SHMEM_ALLOC) $(CCS_DEBUG_MSS_OUT) $(XWR16XX_RADARSS_IMAGE_BIN) $(CCS_DEBUG_DSS_OUT) $(MMWAVE_SECDEV_HSIMAGE_CFG)

C:timmwave_sdk_02_01_00_04packagestidemoxwr16xxmmwmakefile mmwDemo: mssDemo dssDemo

@$(GENERATE_METAIMAGE) $(MMW_DEMO_BIN) $(SHMEM_ALLOC) $(MSS_MMW_DEMO_OUT) $(XWR16XX_RADARSS_IMAGE_BIN) $(DSS_MMW_DEMO_OUT)

@$(GENERATE_HS_METAIMAGE) $(MMW_DEMO_SECURE_BIN) $(SHMEM_ALLOC) $(MSS_MMW_DEMO_OUT) $(XWR16XX_RADARSS_IMAGE_BIN) $(DSS_MMW_DEMO_OUT) $(MMWAVE_SECDEV_HSIMAGE_CFG)

步骤二:特别需要注意的是,SOC驱动里的SOC_deviceInit代码使用了sys_common_xwr16xx_mss.h里和L3 RAM大小相关的定义。因为这些定义的值改变了,所以这个SOC驱动要重新编译。驱动路径是C:timmwave_sdk_02_01_00_04packagestidriverssoc。编译驱动的流程,请参考mmwave_sdk_user_guide.pdfd 4. 5. 4. 1. Building drivers/control/alg components章节。SOC驱动的重新编译必须在mmw demo和ccs debug工程编译之前。

步骤三:在mmw demo里面添加测试代码并测试运行。

测试代码添加在mss_main.c里。

#pragma CODE_SECTION (my_delay , "my_section")

void my_delay()

{

int i;

for (i=0;i<0x100;)

{

i++;

}

System_printf ("Debug: delay done! Increase MSS TCMAn");

}

int main (void)

{

…

Task_create(MmwDemo_mssInitTask, &taskParams, NULL);

//add for test

my_delay();

/* Start BIOS */

BIOS_start();

return 0;

}

在soc驱动重新编译后,重新编译mmw demo(make clean;make all)。在map文件里面可以看到已经有代码分配到了扩展出来的TCMA区域了。

MEMORY CONFIGURATION

name origin length used unused attr fill

---------------------- -------- --------- -------- -------- ---- --------

VECTORS 00000000 00000100 0000003c 000000c4 X

PROG_RAM 00000100 0003ff00 00016128 00029dd8 R X

PROG_RAM2 00040000 0001ffff 0000004a 0001ffb5 R X

将生成的bin文件烧录到flash上运行,mmw demo可正常运行。

步骤四:在CCS下查看在扩展的TCMA中添加的代码输出的打印信息。

在SOC驱动重新编译后,重新编译ccs debug代码(make clean;make all)。

将重新编译生成的ccsdebug.bin烧写到AWR1642BOOST的QSPI flash上。

然后断电,修改SOP设置,连上仿真器。分别在MSS/DSS下载之前编译好的mmw demo的可执行文件。分别运行MMS/DSS。在CCS的输出串口可以看到下面的打印信息。标黄部分说明在扩展的TCMA上的代码正确运行了,也就是一个L3 RAM bank已经成功的分配给了MSS TCMA。

[Cortex_R4_0] **********************************************

Debug: Launching the Millimeter Wave Demo

**********************************************

Debug: delay done! Increase MSS TCMA

Debug: MMWDemoMSS Launched the Initialization Task

Debug: MMWDemoMSS mmWave Control Initialization was successful

[C674X_0] Debug: MMWDemoDSS mmWave Control Initialization succeeded

[Cortex_R4_0] Debug: CLI is operational

[C674X_0] Debug: MMWDemoDSS Data Path init succeeded

Debug: MMWDemoDSS initTask exit

之后连上mmwave visualizer,下载chirp配置命令,demo正常运行。

[Cortex_R4_0] Sensor has been stopped

Debug: MMWDemoMSS Received CLI sensorStart Event

[C674X_0] Heap L2_Heap : size 49152 (0xc000), free 47104 (0xb800)

Heap L1 : size 16384 (0x4000), free 4096 (0x1000)

Heap L2 : size 49152 (0xc000), free 35592 (0x8b08)

Heap L3 : size 655360 (0xa0000), free 507904 (0x7c000)

综合上面步骤三和步骤四的信息,可以证明修改L3 RAM的分布成功!如果用户还有不同的L3 RAM的分配,参考上的流程修改即可。

后话

实际修改L3 RAM的分布是需要修改SHMEMBANKSEL7TO4寄存器的。该寄存器每8个bit控制一个bank,0x1 : DSS 0x2 : MSS TCMA 0x4 : MSS TCMB 0x10: BSS TCMA。每个bank能够配置的使用者略有不同,具体信息请参考xWR1642 TRM里该寄存器的解释。但在上面测试的步骤里面并没有添加修改SHMEMBANKSEL7TO4

的代码。原因是在生成xWR1642的image的时候,会有相应L3 RAM分布信息输入,在image里面就包含了L3 RAM的配置信息。这样ROM code在启动时候就会根据image里L3 RAM的配置信息设置好相关的寄存器,用户不需要在添加代码来修改SHMEMBANKSEL7TO4寄存器了。

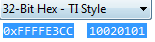

下面是运行修改后代码在CCS下读取到的SHMEMBANKSEL7TO4寄存器的值。可以看到bank 7为BSS所使用。Bank 6为MSS TCMA使用。Bank 5/4为DSS所使用,和测试预想的一致。

图2 运行测试代码后SHMEMBANKSEL7TO4寄存器值

补充:

对于修改r4f的memory,还有一点需要考虑的是r4f的mpu配置。SDK代码里面mpu的配置在C:timmwave_sdk_02_01_00_04packagestidriverssocplatformsoc_xwr16xx_mss.c文件的SOC_mpu_config()函数里。默认定义DOWNLOAD_FROM_CCS变量时,TCMA配置为可读写,可执行,不缓存,配置大小为512KB。所以在上面的例子里,TCMA的大小从256KB,加大到256KB+128KB,大小仍然小于512KB。所以mpu的配置不需要做修改。但是如果用户是增加了TCMB的大小,默认TCMB配置为256KB(实际192KB),但增加128KB后,TCMB的大小就变成了320KB,就大于256KB了,这时候就需要修改相关的mpu配置。另外,TCMB默认的mpu配置为不可执行,是不可以放代码,只能放数据。如果用户需要在TCMB上既放代码又放数据,要修改mpu为可执行即可。下面是加大TCMB大小并修改为可执行的一个例子。

#if ((SOC_XWR16XX_MSS_TCMB_BASE_ADDRESS & (256U * ONE_KB - 1)) != 0)

#error SOC_XWR16XX_MSS_TCMB_BASE_ADDRESS not aligned to 256 KB

#endif

_mpuSetRegion_(mpuREGION3);

_mpuSetRegionBaseAddress_(SOC_XWR16XX_MSS_TCMB_BASE_ADDRESS);

_mpuSetRegionTypeAndPermission_(MPU_NORMAL_OINC_NONSHARED, MPU_PRIV_RW_USER_RW_EXEC);

_mpuSetRegionSizeRegister_(mpuREGION_ENABLE | MPU_512_KB);

审核编辑:郭婷

-

代码

+关注

关注

30文章

4941浏览量

73150 -

DSS

+关注

关注

0文章

26浏览量

13531 -

SDK

+关注

关注

3文章

1093浏览量

51199

发布评论请先 登录

在IWR1642/AWR1642上修改L3 RAM的分布

在IWR1642/AWR1642上修改L3 RAM的分布

评论