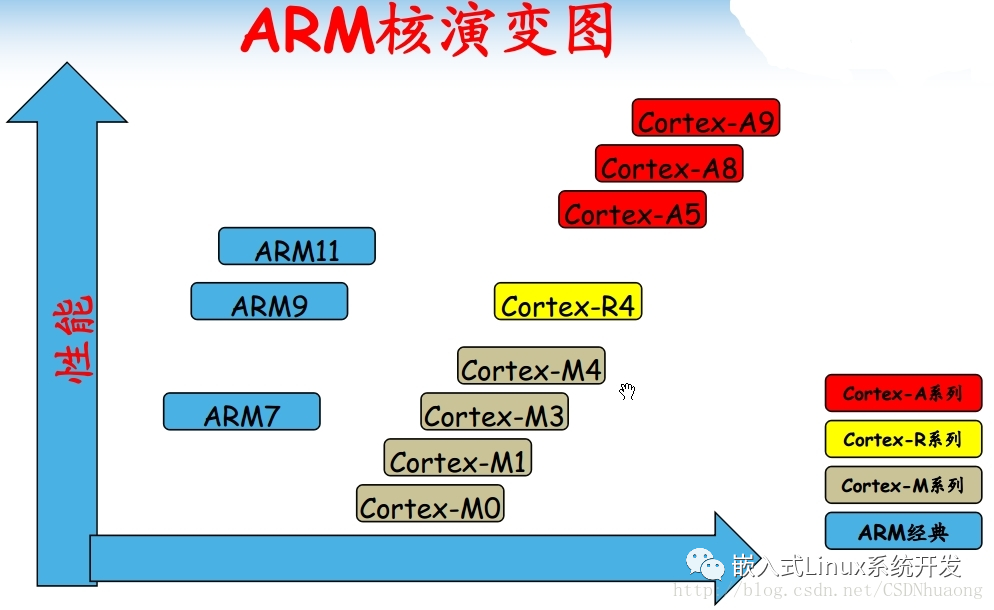

Cortex M架构,典型就是STM32系列,比如STM32F103(Cortex M3)。

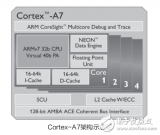

Cortex A架构,可以细分为Cortex A7,Cortex A8,Cortex A9,Cortex A15等,比如NXP的IMX6系列,TI的AM335X系列等。

Cortex M主要用在微控制器领域,Cortex R主要用在对实时性要求比较高的领域,Cortex A主要用在高端应用领域。

Cortex M架构

在Cortex M架构中,比如STM32F103,中断向量表是写在启动文件当中,一般为startup_stm32f10x_hd.s或者startup_stm32f10x_md.s中,.s结尾为汇编文件,这个汇编语言写的启动文件的作用,是在板子上电后为C语言代码的运行做好初始化工作,比如设置堆栈大小,设置中断向量表等,然后再跳转到main函数去执行你的C代码。文件内容如下(部分省略):

设置栈大小

Stack_SizeEQU0x00000400

设置堆大小

Heap_SizeEQU0x00000200

; Vector Table Mapped to Address 0 at Reset后面很多 DCD 的就是STM32的中断向量表,系统所有可用的中断都写在这里,包括外部中断、定时器中断、DMA中断、IIC中断、串口中断等。

Stack_SizeEQU0x00000400 AREASTACK,NOINIT,READWRITE,ALIGN=3 Stack_MemSPACEStack_Size __initial_sp ;HeapConfiguration ;HeapSize(inBytes)<0x0-0xFFFFFFFF:8> ; Heap_SizeEQU0x00000200 AREAHEAP,NOINIT,READWRITE,ALIGN=3 __heap_base Heap_MemSPACEHeap_Size __heap_limit PRESERVE8 THUMB ;VectorTableMappedtoAddress0atReset AREARESET,DATA,READONLY EXPORT__Vectors EXPORT__Vectors_End EXPORT__Vectors_Size __VectorsDCD__initial_sp;TopofStack DCDReset_Handler;ResetHandler DCDNMI_Handler;NMIHandler DCDHardFault_Handler;HardFaultHandler DCDMemManage_Handler;MPUFaultHandler DCDBusFault_Handler;BusFaultHandler DCDUsageFault_Handler;UsageFaultHandler DCD0;Reserved DCD0;Reserved DCD0;Reserved DCD0;Reserved DCDSVC_Handler;SVCallHandler DCDDebugMon_Handler;DebugMonitorHandler DCD0;Reserved DCDPendSV_Handler;PendSVHandler DCDSysTick_Handler;SysTickHandler ;ExternalInterrupts DCDWWDG_IRQHandler;WindowWatchdog DCDPVD_IRQHandler;PVDthroughEXTILinedetect DCDTAMPER_IRQHandler;Tamper DCDRTC_IRQHandler;RTC DCDFLASH_IRQHandler;Flash DCDRCC_IRQHandler;RCC DCDEXTI0_IRQHandler;EXTILine0 DCDEXTI1_IRQHandler;EXTILine1 DCDEXTI2_IRQHandler;EXTILine2 DCDEXTI3_IRQHandler;EXTILine3 DCDEXTI4_IRQHandler;EXTILine4 DCDDMA1_Channel1_IRQHandler;DMA1Channel1 DCDDMA1_Channel2_IRQHandler;DMA1Channel2 DCDDMA1_Channel3_IRQHandler;DMA1Channel3 DCDDMA1_Channel4_IRQHandler;DMA1Channel4 DCDDMA1_Channel5_IRQHandler;DMA1Channel5 DCDDMA1_Channel6_IRQHandler;DMA1Channel6 DCDDMA1_Channel7_IRQHandler;DMA1Channel7 DCDADC1_2_IRQHandler;ADC1&ADC2 DCDUSB_HP_CAN1_TX_IRQHandler;USBHighPriorityorCAN1TX DCDUSB_LP_CAN1_RX0_IRQHandler;USBLowPriorityorCAN1RX0 DCDCAN1_RX1_IRQHandler;CAN1RX1 DCDCAN1_SCE_IRQHandler;CAN1SCE DCDEXTI9_5_IRQHandler;EXTILine9..5 DCDTIM1_BRK_IRQHandler;TIM1Break DCDTIM1_UP_IRQHandler;TIM1Update DCDTIM1_TRG_COM_IRQHandler;TIM1TriggerandCommutation DCDTIM1_CC_IRQHandler;TIM1CaptureCompare DCDTIM2_IRQHandler;TIM2 DCDTIM3_IRQHandler;TIM3 DCDTIM4_IRQHandler;TIM4 DCDI2C1_EV_IRQHandler;I2C1Event DCDI2C1_ER_IRQHandler;I2C1Error DCDI2C2_EV_IRQHandler;I2C2Event DCDI2C2_ER_IRQHandler;I2C2Error DCDSPI1_IRQHandler;SPI1 DCDSPI2_IRQHandler;SPI2 DCDUSART1_IRQHandler;USART1 DCDUSART2_IRQHandler;USART2 DCDUSART3_IRQHandler;USART3 DCDEXTI15_10_IRQHandler;EXTILine15..10 DCDRTCAlarm_IRQHandler;RTCAlarmthroughEXTILine DCDUSBWakeUp_IRQHandler;USBWakeupfromsuspend DCDTIM8_BRK_IRQHandler;TIM8Break DCDTIM8_UP_IRQHandler;TIM8Update DCDTIM8_TRG_COM_IRQHandler;TIM8TriggerandCommutation DCDTIM8_CC_IRQHandler;TIM8CaptureCompare DCDADC3_IRQHandler;ADC3 DCDFSMC_IRQHandler;FSMC DCDSDIO_IRQHandler;SDIO DCDTIM5_IRQHandler;TIM5 DCDSPI3_IRQHandler;SPI3 DCDUART4_IRQHandler;UART4 DCDUART5_IRQHandler;UART5 DCDTIM6_IRQHandler;TIM6 DCDTIM7_IRQHandler;TIM7 DCDDMA2_Channel1_IRQHandler;DMA2Channel1 DCDDMA2_Channel2_IRQHandler;DMA2Channel2 DCDDMA2_Channel3_IRQHandler;DMA2Channel3 DCDDMA2_Channel4_5_IRQHandler;DMA2Channel4&Channel5 __Vectors_End __Vectors_SizeEQU__Vectors_End-__Vectors AREA|.text|,CODE,READONLY

其中“__initial_sp”就是第一条中断向量,存放的是栈顶指针,接下来是第 2 行复位中断复位函数Reset_Handler 的入口地址,依次类推,直到最后一个中断服务函数DMA2_Channel4_5_IRQHandler 的入口地址,这样 STM32F103 的中断向量表就建好了。

中断使用方法:

1、配置中断向量表(ST提供)。 2、配置NVIC(内嵌向量中断控制器)。 3、中断使能。 4、中断服务函数。

先配置好中断向量表(自动),然后配置一下IO口,配置NVIC来管理中断,使能中断,最后编写中断服务函数,中断服务函数里是我们真正想做的事情。

这个思路也适合于Cortex A架构,只是中断系统不同,中断管理器也不同,STM32中的中断管理器是NVIC,Cortex A架构的中断管理器是GIC控制器。GIC 是 ARM 公司给 Cortex-A/R 内核提供的一个中断控制器。

Cortex A架构

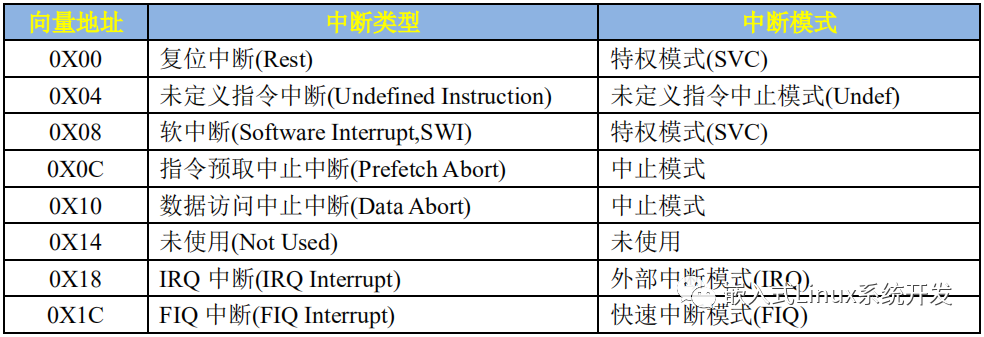

下表为Cortex A架构中断向量表,这个表也是写在.s结尾的启动文件当中,为C语言代码的运行提供前期的初始化工作,只有做好了初始化,你的C语言代码才会运行,启动文件中做好初始化以后,会跳转到你的main函数。

可以发现比STM32的中断少了很多,只有八个中断,还有一个未使用。其中我们最常用的中断是复位中断和 IRQ 中断。

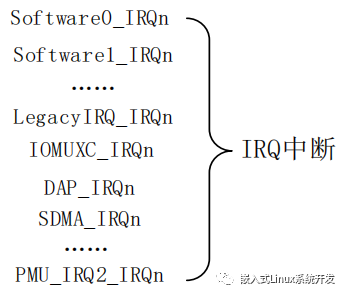

实际上Cortex A架构是不可能只有这么少的中断,Cortex-A 内核 CPU 的所有外部中断都属于IQR 中断,当任意一个外部中断发生的时候都会触发 IRQ 中断。

在 IRQ 中断服务函数里面就可以读取指定的寄存器来判断发生的具体是什么中断,进而根据具体的中断做出相应的处理,如下图:

中断解释:

1、复位中断(Rest),CPU 复位以后就会进入复位中断,我们可以在复位中断服务函数里面做一些初始化工作,比如初始化 SP 指针、DDR 等等。

2、未定义指令中断(Undefined Instruction),如果指令不能识别的话就会产生此中断。

3、软中断(Software Interrupt,SWI),由 SWI 指令引起的中断,Linux 的系统调用会用 SWI指令来引起软中断,通过软中断来陷入到内核空间。

4、指令预取中止中断(Prefetch Abort),预取指令的出错的时候会产生此中断。

5、数据访问中止中断(Data Abort),访问数据出错的时候会产生此中断。

6、IRQ 中断(IRQ Interrupt),外部中断,芯片内部的外设中断都会引起此中断的发生。

7、FIQ 中断(FIQ Interrupt),快速中断,如果需要快速处理中断的话就可以使用此中。

存放地址

中断向量表都是链接到代码的最前面,比如一般 ARM 处理器都是从地址 0X0000 0000 开始执行指令的,那么中断向量表就是从0X0000 0000 开始存放的。

在STM32中,一般代码是下载到 0X0800 0000开始的存储区域中。因此中断向量表是存放到 0X0800 0000 地址处的,而不是 0X00000000。这种是通过中断向量表偏移实现的。

审核编辑:刘清

-

微控制器

+关注

关注

49文章

8872浏览量

165720 -

ARM

+关注

关注

135文章

9588浏览量

393668 -

STM32

+关注

关注

2313文章

11195浏览量

374656 -

中断系统

+关注

关注

1文章

96浏览量

61774 -

STM32F103

+关注

关注

34文章

497浏览量

68199

原文标题:Cortex M架构与Cortex A架构中断系统的区别

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Cortex-M产品的特色

Cortex-M0和Cortex-M0+的区别

【图书分享】《ARM Cortex-M3应用开发实例详解》

arm架构和cortex架构

Cortex-M处理器采用的架构是什么

cortex-m下各种微架构的区别是什么?

Cortex-A8与STM32有哪些区别呢

介绍Cortex-A和Cortex-M的TrustZone之间的差异

Cortex-A8与STM32的区别

Cortex M架构与Cortex A架构中断系统的区别详解

Cortex M架构与Cortex A架构中断系统的区别详解

评论