这里提到的局部重配置技术(Partial Reconfiguration) 是现场可编程门阵列(呵呵,就是FPGA了) 器件中的一部分。指的是在FPGA其他部分还在正常运行的情况下对其局部进行的重新配置。

众所周知,硬件也可以像软件一样做模块化的设计。比如使用HDL在FPGA器件内部,先创建子模块,再用更高级的模块来封装各种子模块。在某些情况下,如果在FPGA的一部分还在正常工作时,能实时调整其他一个或多个子模块功能,将是一个很有好处的事情。

一般情况下,要重新配置一个FPGA需要使其处于复位状态,并通过外部控制器重新加载一个新设计到器件中。而局部重配置技术允许在FPGA内部或外部的控制器在加载一个局部设计到一个可重配置模块中时,设计中的其他部分仍能继续正常工作。局部重配置还可以用于存储多种设计时的节省空间目的,比如说只存储多种设计之间不同的局部,设计的相同部分仅保存一次,不会重复保存。

举个常见例子,比如在通信产品中,如果一个FPGA器件控制多个连接,一些连接可能要加密,并且要加载不同的加密IP核来处理不同的连接,这时有了局部重配置技术就不用down掉整个控制器来切换了。

目前局部重配置技术还不能支持XILINX旗下全部的FPGA产品系列。当前版本的软件中仅支持Virtex II, Virtex II Pro, and Virtex 4系列,更新的产品系列应该在更新的软件版本中支持。一个特殊的软件流程要在这种模块设计过程中被强调注意。典型情况下,这种设计模块是建立在FPGA内部经过良好定义的边界上的,并且需要通过特别的设计,将其映射到内部硬件上。

从设计的功能性上来分,局部重配置可以分为以下两种:

动态局部重配置(dynamic partial reconfiguration), 显而易见,这是个可以活动的重配置,它允许FPGA的其他部分还在正常运行的情况下改变器件的一部分。

静态局部重配置(static partial reconfiguration),在这种重配置处理期间,器件不是活动的。当局部数据被发送入FPGA时,器件的其余部分是停止的(处于shutdown模式),配置完成后其余部分才又开始运行。

XILINX的FPGA器件的局部重配置还可以分为以下两种类型:

基于模块的局部重配置(Module-based partial reconfiguration)允许重配置设计中特定的模块元件。要确保通过可重配置模块边界的通信,需要事先准备好一种特殊的总线宏单元。该总线宏单元作为一种固定的路由桥工作,连接设计中空余部分的可重配置模块。基于模块的局部重配置在设计规范阶段需要运行一套特定的Guidelines。最终为设计中的每个可重配置模块都创建一个分立的bit流。这样的bit流即可被用来运行局部重配置。

基于区别的局部重配置(Difference-based partial reconfiguration) 可以被用在对设计的一次小修改上。尤其是在改变LUT等式或存储器块内容时尤为有效。这样的局部bit流仅包含现有设计结构和新结构之间的区别信息。基于区别的局部重配置有两种方式:前端和后端。前端方式基于硬件描述语言(HDL)的修改。这种方式对于一个需要完全重复综合和实现过程的解决方案来讲是很清晰的。后端方式允许在原型设计的实现阶段进行修改,因此不需要重新执行综合过程。两种方式的运用都会创建局部bit流,并都能用于FPGA的局部重配置功能。

需要提示注意的是:局部重配置仅能更新FPGA的一部分。更新期间不需要FPGA的任何部分继续运行。

审核编辑 :李倩

-

FPGA

+关注

关注

1655文章

22283浏览量

630236 -

控制器

+关注

关注

114文章

17638浏览量

190246 -

赛灵思

+关注

关注

33文章

1797浏览量

133147

原文标题:谈谈赛灵思的局部重配置技术(Partial Reconfiguration)

文章出处:【微信号:Hack电子,微信公众号:Hack电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

强强联合进军万亿晶振市场,赛思电子与一晶科技成立合资公司

易灵思2025 FPGA技术研讨会成都站圆满收官

易灵思与思特威第二届机器视觉方案大会圆满收官

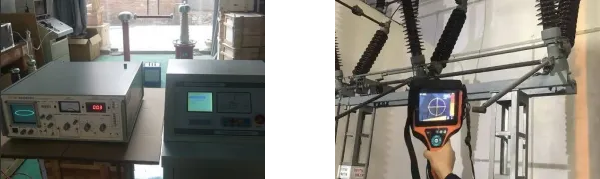

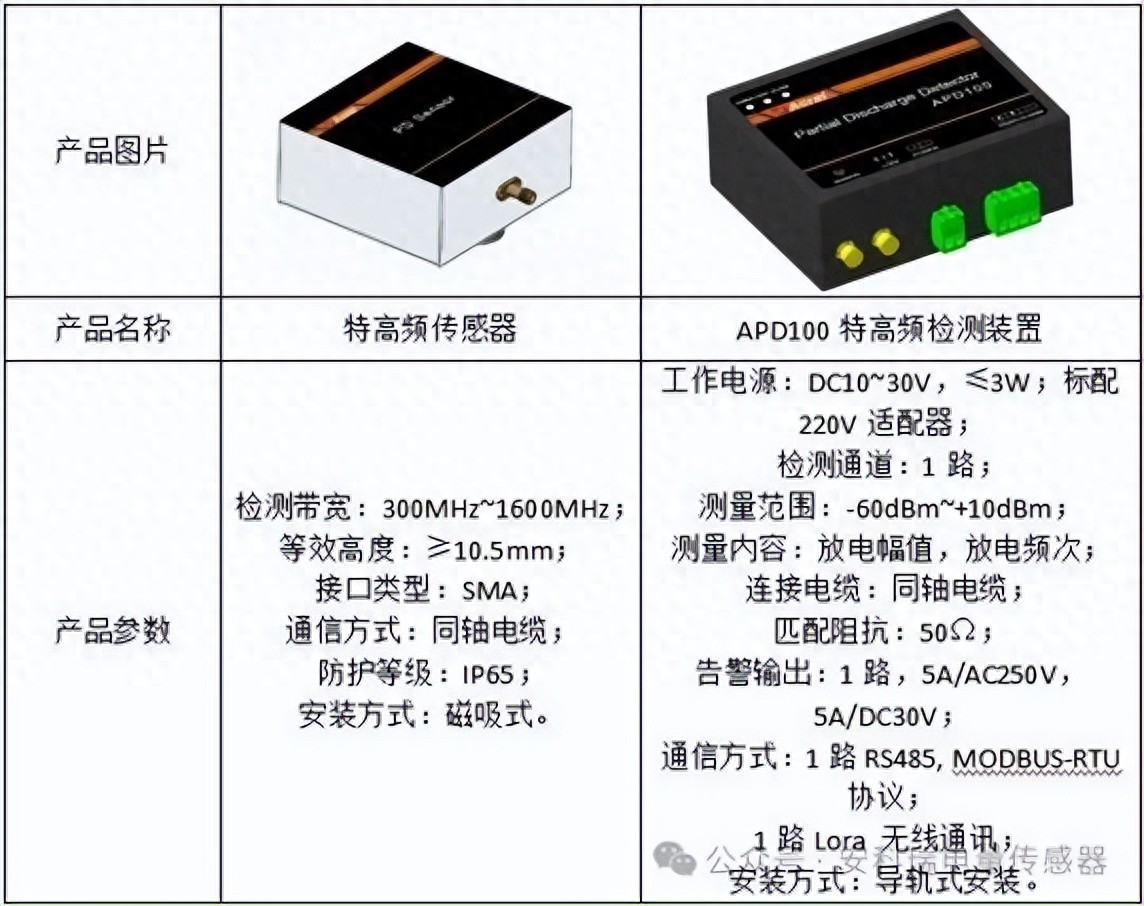

数字化仪在局部放电中的应用

睿思芯科灵羽处理器获得国家级权威认可

创“芯”舞台!思尔芯邀您挑战2025 EDA精英赛

易灵思 FPGA TJ375的PLL的动态配置

安科瑞APD局部放电监测装置解决方案:守护电力设备安全运行

授时系统厂家,授时系统哪家好?赛思高精度授时系统助力华福证券授时服务新升级!

赛思快讯 | 嘉兴市委书记陈伟一行莅临赛思调研

易灵思2025 FPGA技术研讨会北京站圆满结束

国产EDA亿灵思®接入DeepSeek

赛灵思的局部重配置技术(Partial Reconfiguration)

赛灵思的局部重配置技术(Partial Reconfiguration)

评论