在本文中,我想谈谈我们CEVA和Intrinsix如何就OEM和半导体进行协作,以找到进行交钥匙ASIC设计或无线子系统设计的可靠路径。

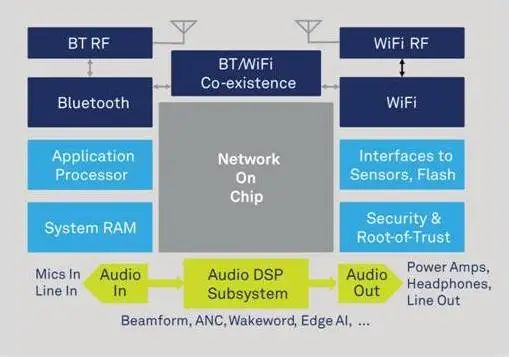

举例来说,想象一下您可能想要为无线智能扬声器或智能家庭娱乐系统构建的SoC类型。该系统的核心是音频管线,支持控制命令语音处理,并可通过Wi-Fi和蓝牙连接技术实现无线连接,其中BT连接可用于远程控制或音频流式传输。我们还提供用于蓝牙和WiFi的片上射频。总体结构图如下所示:

ASIC设计共创阶段I – 规划

规划从详细讨论产品需求开始。智能扬声器通常会配备多个麦克风,支持自动回声消除和音频波束成型,以放大整个房间的语音命令。无线耳塞可能只需一个或两个麦克风,并且依靠骨传导来接收语音命令,而非波束成型。

对于蓝牙,您想仅使用BLE还是想通过双模式来支持较旧的设备或更丰富的音频?对于Wi-Fi,向后兼容性可解决大多数问题,但您可能需要考虑蓝牙和Wi-Fi之间的干扰(2.4GHz)。我们有解决这一问题的共存解决方案。集成射频收发机也需要仔细规划。

对于IP选择,CEVA是无线、音频、人工智能和运动感应嵌入式解决方案的市场领导者,可解决此应用的IP 需求。

对于其他功能和参数目标,我们会讨论设计和IP替代方案以及相关取舍。讨论将涵盖应用控制、外部接口(如果有的话)以及安全启动、配置和无线更新的安全性(CEVA还提供嵌入式安全信任根解决方案)。在此阶段,我们应该设定功率、性能和服务质量(带宽和延迟)目标。如果您有自有IP或计划使用商业IP,则我们需要讨论IP与总体目标的匹配程度。所有重要预期都应在这一阶段敲定。然后,我们将构建、审核并商定最终架构结构图和需求列表。

我们的方法高度重视验证,以确保我们能够准确地按您的预期提供解决方案,并且方案能够在第一批硅片样品上正常运行。因此,我们将与您密切合作,以制定、审核和签署全面的需求规范。其中应包括用例和操作模式,以及驱动这些用例和模式的软件,还有预期的异常行为。需求必须涵盖参数行为和功能。

一旦架构和需求得到充分定义,我们将构建详细的项目时间表和成本分析,并纳入人力、IP、工具和其他因素。我们将通过一系列完整文档向您展示这些内容,从验证计划和设计规范,到DFT以及ASIC设计的实施计划。我们还将讨论软件注意事项。

CEVA为其许多IP提供广泛的软件解决方案,例如无线协议堆栈、音频堆栈和用于AI产品的CNN/DNN堆栈。这些内容将在规划讨论中介绍,并在报告中予以详细说明,以帮助您了解如何将现有软件集成到目标硬件中。

无线子系统的规划过程与SoC计划的规划过程基本相似,除了这里的客户端还必须在子系统上提供SoC约束(例如可用时钟、重置、电源控制平面图约束等)。

共创 – 规划阶段以外

共创项目的其余部分遵循标准ASIC设计或子系统设计流程,装配、验证和实施之间具有显著的并行性。射频和混合信号集成需要专业技能。

在整个过程中,我们会更新进展并邀请您讨论当前设计情况。在RTL开发过程中,客户将为我们提供测试软件,以证明关键用例的需求已得到满足。如果他们运行FPGA仿真以进行自己的软件开发,他们将在仿真就绪的RTL衰减可用时使用这些RTL衰减。对于ASIC设计,我们定期向客户提供最新进展,从物理设计前时序收敛到物理设计后时序收敛及完全签核。

我们过往的表现是我们的品质保证

CEVA和Intrinsix将验证和严密的项目计划放在我们所有工作的第一位,这些构成我们对您的承诺。35年来,我们一直按时、按规格地向领先的系统和半导体公司交付设计和子系统。我们合作的大部分客户来自国防、医疗及其他领域,他们对流程和产品可靠性的要求非常高。我们与这些客户共同开发的流程和专业知识已经融入到我们“第一次就把事情做好”的文化理念中,正如您在我们的验证和项目管理规范中所看到的那样。

我们设计的ASIC范围广泛,从智能扬声器到无线环绕音响,从智能电源工具到智能手术仪器,从医疗植入体到可穿戴和智能健康设备,从物联网微控制器到生物指纹传感器。其中许多应用目前都在批量生产中。

我们基于DSP的IP解决方案包括移动、物联网和基础设施中的5G基带处理平台、任何摄像头设备的高级成像和计算机视觉平台、多个物联网市场的音频/语音/声音和超低功耗始终开启/传感应用平台。

我们提供传感器技术,并为耳穿戴设备、可穿戴设备、AR/VR、PC、机器人、远程控制和物联网等市场提供广泛的传感器融合软件和惯性测量装置(IMU)解决方案。对于无线物联网,我们的蓝牙(低功耗和双模)、Wi-Fi 4/5/6 (802.11n/ac/ax)、超宽带(UWB)、NB-IoT和GNSS平台是业内广泛授权的连接平台。

我们在IP和ASIC设计交付方面的综合专业知识为您保驾护航,CEVA和Intrinsix无疑是您下一款突破性产品的正确选择。

联系CEVA,了解我们如何帮助您进行共创规划。

识别右侧二维码

立即了解

CEVA更多信息

本文作者:Mark Beal, Chief Technical Officer at Intrinsix, subsidiary of CEVA

-

dsp

+关注

关注

559文章

8214浏览量

363935 -

蓝牙

+关注

关注

119文章

6221浏览量

177529 -

CEVA

+关注

关注

1文章

191浏览量

77050

原文标题:共创计划确保可靠ASIC设计

文章出处:【微信号:CEVA-IP,微信公众号:CEVA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

对话K计划系列,第五期主题:《三体》,星辰大海,K计划未来探索(总结:唐石平)

对话K计划系列,第五期主题:《三体》,星辰大海,K计划未来探索(嘉宾:何红星)

对话K计划系列,第五期主题:《三体》,星辰大海,K计划未来探索(嘉宾:李平)

【深度解析】硬件电路设计:如何确保嵌入式数据可靠性?

AI芯片,需要ASIC

实用电子电路设计(全6本)——数字逻辑电路的ASIC设计

NS-JD电缆接地箱——确保电力传输安全的首选解决方案

CPLD 与 ASIC 的比较

ASIC和GPU的原理和优势

共创计划确保可靠ASIC设计

共创计划确保可靠ASIC设计

评论