去耦电容的摆放

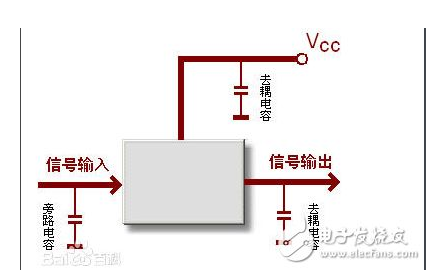

在PCB的设计中,使用去偶电容能够有效滤除电源中包含的噪声,电容的摆放是根据容值大小确定,电容的去耦作用是有一定的距离要求,满足去耦半径问题,若电容距离IC的摆放距离超出电容的去耦半径,则电容将失去去耦作用。

大电容的去耦半径大,小电容的去耦半径小,因此小电容应距离IC的供电引脚尽可能近,大电容可距离IC适当远些,各个规格的去耦电容布局时要均匀布置在IC周围,这样可以使IC所在区域的各电源等级均匀去耦。如下图举例所示:

去耦电容的合理布局

引脚去耦

适用于IC引脚较少,且电源引脚与地引脚之间距离较小的情况,如下图所示:

引脚去耦

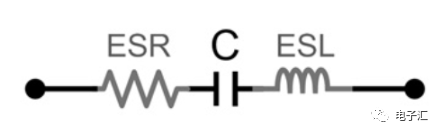

引脚去耦时,要尽可能缩短焊盘和去耦电容之间引线的长度,避免引入额外的寄生电感。

平面去耦

适用于电源引脚与地引脚较多且分布分散的IC去耦,BGA类的IC一般都采用平面去耦方式,如下图所示:

平面去耦

平面去耦中的去耦电容并不和IC的电源和地引脚直接相邻,去耦电容、IC的电源引脚和地引脚都是通过过孔连接到内部的电源平面和地平面。

当电容摆放空间不足,可以2个引脚共用一个去耦电容的电源引脚,引线处理尽可能短,若无法保证电源引线和地引线都最短,优先考虑地引脚引线最短,使回流路径短,如下图所示:

去耦电容平面去耦方式焊盘引线的处理

电容焊盘的扇出

电容的焊盘在做扇出时,有如下几种方式,这里做了方案对比,采用多过孔与电源平面和地平面连接时,并联的过孔可以减小过孔引入的寄生电感,使电容的去耦特性优于其他焊盘扇出或走线的方式。

电容焊盘的扇出

审核编辑:刘清

-

PCB设计

+关注

关注

396文章

4939浏览量

95789 -

BGA

+关注

关注

5文章

586浏览量

51958 -

电源IC

+关注

关注

4文章

472浏览量

48262 -

去耦电容

+关注

关注

0文章

1浏览量

251

发布评论请先 登录

PCB布线技巧:去耦电容的摆放

PCB布板去耦电容为什么一定要就近摆放

PCB布板时去耦电容的就近摆放

PCB布线技巧及去耦电容的摆放问题

PCB布局时去耦电容的摆放

设计技巧#老司机 PCB打样布线去耦电容的摆放技巧

电容在高速PCB设计中该如何摆放呢?

PCB布局时去耦电容摆放经验分享

看看去耦电容的摆放要遵循什么规则

看看去耦电容的摆放要遵循什么规则

评论