-已经请您介绍了FPGA的电源要求,接下来请您介绍一下将该DC/DC转换器系列定义为“FPGA用”的原因。首先,该系列中有些什么样的DC/DC转换器IC呢?

目前有8种机型,是覆盖FPGA电源的电压与电流的产品阵容。单个介绍比较困难,请看产品阵容表。

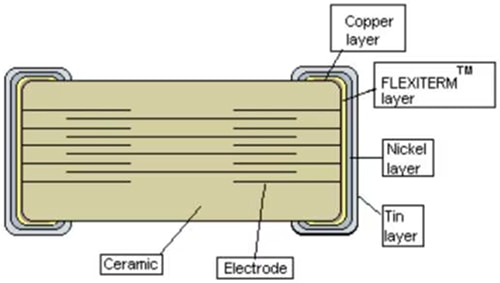

大致分为功率晶体管内置型与外置控制器型,全部为同步整流型单通道DC/DC转换器IC。输入电压考虑到5V系统电压与12V总线输入电压,耐压为7V与15.2V,控制器为28V。功率晶体管内置型的输出电流为1A~6A,控制器的输出电流通过外置MOSFET可设置的范围较广。设想的输出电压为1.8V~1V左右,因此最低输出电压为0.8V,控制器为0.75V。即使作为通用电源使用也搭载了一般的电源良好(Power Good)、软启动及各种保护功能。

-前面请您总结的有关FPGA的电源要求事项是:1) 电源电压为多种;2) 电源时序;3) 低电压大电流;4) 电压精度要求严格(包括纹波、负载瞬态引起的变动,PCB板布线电阻引起的电压降等);5) 低噪声。您提到这些是电源方面的课题,那么该DC/DC转换器系列是怎么处理这些课题的呢?

首先,1)电源电压为多种,使1个DC/DC转换器支持各电源,可进行最适合的条件设置。关于2)电源时序,可通过软启动和外部控制进行处理。最关键的要点在于3)低电压大电流和4)电压精度的处理。5)低噪声也与此相关。

-从您的介绍和表来看,最低电压为0.8V/0.75V,已经很低了,输出电流为1A~6A,控制器可达到更高,但好像近年来通用DC/DC转换器也是相同的规格。

关键是4)电压精度。DC的电压精度由内部的参考电压精度来决定,保证最大值为±1%(控制器为±1.5%),这属于最高精度级别了。也就是说,如果这是输出电压精度的全部的话,前面举例的1V±3%很轻松就可以达到。但是,作为电压精度还要加上括号中(纹波、负载瞬态引起的变动,以及PCB板布线电阻引起的电压降等)的误差。

-那么,针对些误差也有相应的处理吧?

对影响电压精度的要因——纹波和负载瞬态的处理与对电压降的处理是分开的。首先,对纹波与负载瞬态进行说明。纹波,提高对来自输出的反馈电压的响应速度,对参考电压如果将开关尽可能控制在狭小范围内,可减小误差。关于负载瞬态,负载急剧变动时,如果尽可能快速响应并使变动的电压恢复为设置值,则输出变动变小,并可在短时间内恢复。为此,该DC/DC转换器系列采用了电流模式、迟滞模式、H3Reg™模式等高速控制模式。

-电流模式与迟滞模式是众所周知的基本控制方法,H3Reg是什么样的模式呢?

H3Reg是ROHM独有的高速瞬态响应控制。下面的框图表示BD95601MUV-LB的H3Reg控制环路。H3Reg是定位为“固定导通时间控制的改进版”的控制方法,使用电压比较器快速比较基准电压(参考电压)与反馈电压,并快速切换输出开关。这不必依赖开关频率即可实现快速响应。

正常工作时的波形如下。

如果FB反馈电压(为便于比较被分压的输出电压)比REF基准电压(参考)低,则通过比较器立即导通HG(高边输出功率晶体管),在右边公式算出的时间内对输出供应电流,从而使Vout上升并关闭HG。接着LG(低边输出功率晶体管)在FB=REF成立之前导通,Vout下降。

负载电流(Io)瞬态增加时输出电压显著降低,可能会出现即使过了上述公式中的ton时间还未完全上升到设置电压的情况。当检测到这种情况时,像左边的波形那样,H3Reg延长ton时间以促进Vout的恢复,也就是提高瞬态响应速度。之后如果Vout恢复,则恢复正常工作。

其他还有很多更细致的内容,但以该H3Reg为代表的高速瞬态响应控制,是满足FPGA的低电压大电流条件下高输出电压精度等电源要求的关键要点。

-对电压精度的另一个课题–PCB板布线引起的电压降是怎么处理的呢?

有两种方法,一种是反馈FPGA电源引脚电压的远程感测方法,另一种是尽可能地将DC/DC转换器的输出端安装在FPGA的电源引脚端的称为“POL(Point of Load)”的方法。

-明白了,该DC/DC转换器系列的基本性能当然不用说,高速瞬态响应性能非常优异,因此可以满足FPGA的电源要求。但是,在实际的设计过程中,为了充分发挥IC的性能,应该需要元器件选型及PCB板布局等方面的技术诀窍和经验积累。

这是非常重要的一点。这次采访中,我重点讲了IC的功能及性能方面的要点。但实际上是通过电源电路来应对FPGA的要求的,而这涉及到组成元器件的选型及布局等很多必须注意的内容。对此,ROHM在提供使用了该DC/DC转换器系列的参考设计的同时,也提供个別的设计支持。以下是参考设计示例。

-有了这样的参考设计与支持,我想设计师会比较有信心。

如其名称所呈现的,FPGA是可编程器件,构成与工作各不相同,对电源的要求也不同。从这个意义上讲设计支持也是必须的。

-最后还有什么需要补充的吗?

实际上,还没提到电源的固有项目–效率。决不是说FPGA不需要高效率,FPGA是需要较大功率的设备,因此电源的最大效率还是备受期待的。该DC/DC转换器系列,基本上通过同步整流式可实现90%左右的最大效率,轻负载时具有以Deep-SLLM™ (Simple Light Load Mode)为代表的轻负载效率保持模式,在效率方面也可满足FPGA的要求。

审核编辑:汤梓红

-

电源

+关注

关注

185文章

18707浏览量

261325 -

FPGA

+关注

关注

1655文章

22282浏览量

630078 -

转换器

+关注

关注

27文章

9365浏览量

155071

发布评论请先 登录

交流不停电电源ups应满足哪些条件?

通过采用先进组件满足汽车设计不断发展的要求

使用Simcenter STAR-CCM+进行拓扑优化:生成理想的增材制造设计,尽早满足工程要求

医疗设备电源中的铝电解电容:为何对 “低漏电流” 有极致要求?

UPS电源—不同场景UPS电源要求大不同

根据不同的医疗设备要求选择合适的医疗电源滤波器参数

在医疗设备中,电源滤波器的接线方式有哪些严格要求?

ups电源—UPS电源安装,输入电压有什么要求?

ups电源—UPS电源安装环境要求,您知道吗?

AFE5804工作频率为10M或者10M以上时,输出的FCLK满足要求,但LCLK就会变得很小,怎么解决?

用RC低通滤波的话,转折频率是可以满足,但是RC滤波器中,充电时间常数RC能满足△-∑型ADC的采样时间要求吗?

基于Agilex 5 FPGA的模块系统介绍

为了满足FPGA的电源要求

为了满足FPGA的电源要求

评论