芯片贴装工艺是将芯片用有机胶和金属焊料将芯片粘接在基板上,起到热、电和机械连接的作用。那么你知道半导体集成电路芯片贴装的方法有哪些?这四种方式分别有什么区别?今天__【科准测控】__小编就来为大家介绍一下半导体集成电路芯片贴装的四种方法以及区别,一起往下看吧!

芯片贴装也称芯片粘贴,简称装片、黏晶,就是把芯片装配到管壳底座或引线架上去芯片装片如图 2-5 所示。

黏晶的目的是将一颗颗分离的晶粒放置在引线架上并用银胶黏着固定。引线架是提供给晶粒一个黏着的位置 (晶粒座),并预设可延伸集成电路晶粒电路的延伸脚 (分为内引脚及外引脚)。一个引线架上依不同的设计可以有数个晶粒座,这数个晶粒座通常排成一列,也有成矩阵式的多列排法。引线架定位后,首先要在晶粒座预定黏着晶粒的位置点上银胶(此动作称为点胶),然后移至下一位置将晶粒放置其上,而经过切割的晶圆上的晶粒则由取放臂一颗一颗地放置在已点胶的晶粒座上。黏晶完后的引线架则经传输设备送至弹匣内。

切割下来的芯片贴装到引线架的中间焊盘 (Die-padding) 上,焊盘的尺寸要和芯片大小相匹配。若焊盘尺寸太大,则会导致引线跨度太大,在转移成型过程中会由于流动产生的应力而造成引线弯曲及芯片位移等现象。贴装的方式可以用软焊料 (如含 Sn 的合金、Au~Si 低共熔合金等) 焊接到基板上,在塑料封装中最常用的方法是使用聚合物粘结剂 (Polmer Die Adhesive) 粘贴到金属引线架上。常用的聚合物是环氧 (Epoxy) 或聚亚胺(Polyimide,PI),以Ag(颗粒或薄片)或A1,0,作为填充料 (Filer),其目的是改善粘结剂的导热性。工艺过程是一个自动拾片机(机械手) 将芯片精确地放置到芯片焊盘上。

装片要求芯片和引线架小岛的连接机械强度高,导热和导电性能好,装配定位准确,能满足自动键合的需要,能承受键合或封装时可能的高温,保证器件在各种条件下使用时有良好的可靠性。

装片过程如图 2-6 所示,具体如下:

- 银浆分配器在引线架的小岛上点好银浆。

(2) 抓片头将芯片从圆片上抓到校正台上。

(3) 校正台将芯片的角度进行校正。

(4) 装片头将芯片由校正台装到引线架的小岛上,装片过程结束。

陶瓷封装以金-硅共晶粘结法最为常用:塑料封装则以高分子胶粘剂粘结法为主。

1、共晶粘贴法

共晶粘贴法利用金-硅合金在 363C 时产生的共晶反应特性进行集成电路芯片的粘贴在使用金-硅 (一般是 69%Au~31%Si)低共熔合金时,首先将材料切成小块,放到引线架的芯片焊盘上,然后将芯片放在焊料上,加热到熔点以上 (>300C)。但是,由于芯片、引线架之间的热膨胀系数(Coefhcient of Thermal Expansion,CTE)严重失配,合金焊料贴装可能会造成严重的芯片开裂现象。而且,在一些有特殊导电性要求的大功率晶体管中,还有使用合金焊料或焊管连接芯片和芯片焊盘的。

共晶粘贴法通常是将集成电路芯片置于已镀有金膜的基板芯片座上,再加热至约为425C,金-硅交互扩散而形成接合,共晶粘结通常在热氮气保护的环境中进行,以防止硅高温氧化,基板与芯片在反应前需给一相互摩擦的动作,以除去硅氧化表层,增加反应液面的浸润,使接合的热传导性降低,同时也避免因应力分布不均匀而导致集成电路芯片破裂损坏。为了获得最佳的粘结效果,集成电路芯片背面常先镀有一薄层的金,在基板的芯片承载座上植人预成型片(Preform),预成型片一般约为0025mm厚,使用预成型片可以弥补基板孔洞平整度不佳时所造成的接合不完全,因此在大面积集成电路芯片的粘结时常被使用因为预成型片非金-硅成分并没有完全互溶,其中的硅仍然会发生氧化的现象,故粘结过程中仍需进行相互摩擦的动作并以热氮气保护。预成型片也不得过量使用,否则会造成材料溢流,对封装的可靠性有害。预成型片也可使用不易氧化的纯金片,但接合时所需的温度具高的雅顶切越桂较高。

2、导电胶粘贴法

导电胶是大家熟知的填充银的高分子材料聚合物。高分子胶粘贴法也称树脂粘贴法,它采用环氧、聚酰亚胺、酚醛、聚胺树脂及硅树脂作为粘结剂,加入银粉作为导电材料,再加入氧化铝粉填充料作为导热材料。

以下三种导电胶的配方可以提供所需的电互连:

(1)各向同性材料,它能沿各个方向导电,可以代替热敏元件上的焊料,也能用于需要接地的元器件。

(2导电硅橡胶,它能有助于保护元器件免受环境的危害,如水、汽,而且可以屏蔽电磁和射频干扰。

(3)各向异性导电聚合物,它只允许电流沿一个方向流动,提供倒装芯片元器件的电接触和消除应变力。

由于高分子材料与引线架材料的热膨胀系数相近,高分子胶粘结法因此成为塑胶封装常用的芯片粘结法,其是利用戳印、网印或点胶等方法将环氧树脂涂在芯片承载座上,放置集成电路芯片后再加热完成粘结。高分子胶中也可填入银等金属以提高其热传导性。胶材可以制成固体膜状再施以热压接合。低成本且能配合自动化生产是高分子胶粘结法广为采用的原因,但其热稳定性不良,易致成分泄漏而影响封装可靠性。

高分子胶粘结剂的基体材料绝大多数是环氧树脂,填充料一般是银颗粒或者是银薄片,填充量一般在 75%~80%之间,在这样的填充量下,粘结剂都是导电的。但是,作为芯片的粘结剂,添加如此高含量的填充料的目的是改善粘结剂的导热性,即是为了散热因为在塑料封装中,电路运行过程产生的绝大部分热量将通过芯片粘结剂、引线架散发出去。

用芯片粘结剂贴装的工艺过程如下:用针筒或注射器将粘结剂涂布到芯片焊盘上(要有适合的厚度和轮廓,对较小的芯片来讲,内圆角形可提供足够的强度,但不能大靠近芯片表面。否则会引起银迁移现象),然后用自动拾片机 (机械手) 将芯片精确地放置到焊盘的粘结剂上面。对于大芯片,要求误差<25 m,角误差<0.3°。对 15~30 m 厚的粘结剂,压力为5N/cm。若芯片放置不当,会产生一系列的问题,例如:空洞造成高应力:环氧粘结剂在引脚上造成搭桥现象,引起内连接问题:在引线键合时造成引线架翘曲,使得一边引线应力大。一边引线应力小,而且为了找准芯片位置,还会使引线键合的生产效率降低,成品下降。

芯片粘结剂在使用过程中可能产生如下问题:在高温存储时的长期降解,界面处形成空洞会引起芯片的开裂。空洞处的热阳会造成局部温度升高,因而引起电路参数漂移现象:吸潮性造成模块焊接到基板或电路板时产生水平方向的模块开裂问题。

高分子胶粘结剂通常需要进行固化处理,环树脂粘结剂的固化条件一般是 150℃,1h(也可以用186℃,0.5h的固化条件)。聚亚胺的固化温度要更高一些,时间也更长。具体的工艺参数可通过差分量热仪 (Differential Scanning Calorimetry,DSC)实验来确定。

3、玻璃胶粘贴法

玻璃胶粘贴法是一种仅适用于陶瓷封装的低成本芯片粘结技术,是以戳印(Stamping)、网印(Screen Printing)或点胶(Syringe Dispensing)的方法将填有银的玻璃胶涂于基板的芯片座上,放置集成电路芯片后再加热除出胶中的有机成分,可使玻璃熔融接合。玻璃胶粘贴法可以得到无孔洞、热稳定性优良、低残余应力与低湿气含量的接合。但在粘结热处理过程中,冷却温度需谨慎控制以防接合破裂,胶中的有机成分也需完全除去,否则将有损封装的结构稳定与可靠性。

4、焊接粘贴法

焊接粘贴法为另一种利用合金反应进行芯片粘结的方法,其主要的优点是能形成热传导性优良的黏结。焊接粘贴法也必须在热氮气保护的环境中进行,以防止焊锡氧化及孔洞的形成,常见的焊料有金-硅、金-锡、金-锗等硬质合金与铅-锡、铅-银-钢等软质合金,使用硬质焊料可以获得具有良好的抗疲劳 (Fatigue) 与蠕变 (Creep) 特性的粘结,但它有因热膨胀系数差引起的应力破坏问题。使用软质焊料可以改善这一缺点,使用前需在集成电路芯片背面先镀上多层金属薄膜。

芯片在粘贴过程中,由于操作不当或工艺缺陷,往往造成粘贴失败,从而使芯片废弃,常见的芯片废弃情况有如下几种:

- 裂缝划痕(Scratches Die)。

- (2)断裂(Crack Die/Die Retake)。

- 污染(Contaminated Die)。

- 错位(Die Placement)。

- 缺失(Missing Die)。

(6)堆叠 (Stacked Die)。

(7)定位不良(Misorientation Die)。

(8)融合不良(Poor Melting)。

以上就是给大家分享的半导体集成电路芯片贴装的四种方式了,有共晶粘贴法、导电胶粘贴法、玻璃胶粘贴法、焊接粘贴法,内容十分详细,希望能给大家带来帮助!如果您对半导体芯片、集成电路、推拉力测试机有任何不清楚的问题,欢迎给我们私信或留言,科准测控的技术团队都会为大家解答!还想了解更多有关半导体集成电路的知识,敬请关注!

审核编辑:汤梓红

-

芯片

+关注

关注

462文章

53530浏览量

458842 -

集成电路

+关注

关注

5446文章

12464浏览量

372609 -

半导体

+关注

关注

336文章

29978浏览量

257984 -

芯片贴装

+关注

关注

0文章

8浏览量

6246

发布评论请先 登录

42.5亿,重庆半导体大动作,8个集成电路领域头部企业集中签约,包含2个传感器项目

现代集成电路半导体器件

【展会预告】2025 中国西部半导体展重磅来袭,华秋邀您 7 月 25-27 日西安共探集成电路新未来!

全球半导体进出口(1-3月):日本设备出口增长14.1%,韩国集成电路出口增加1.6%

电机控制专用集成电路PDF版

中国集成电路大全 接口集成电路

科研分享|智能芯片与异构集成电路电磁兼容问题

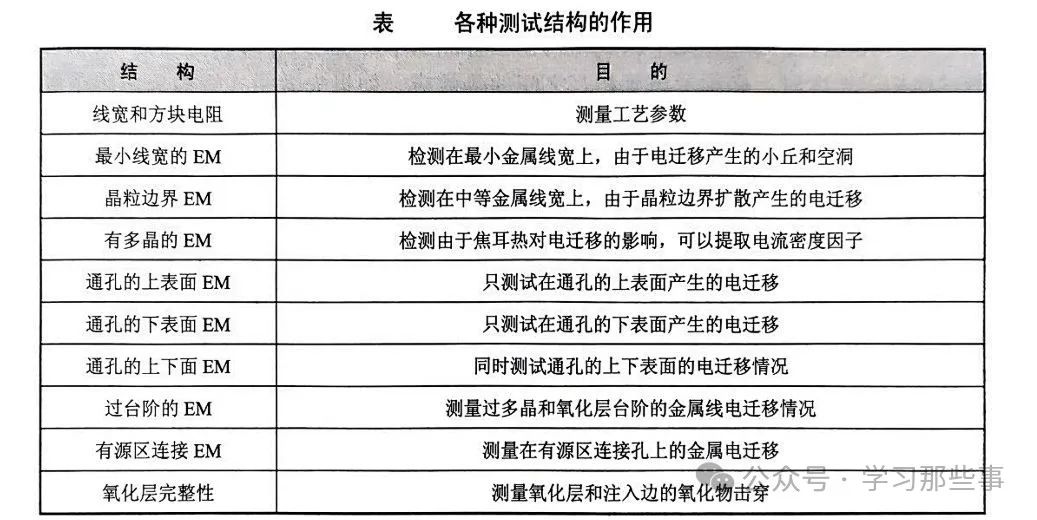

半导体集成电路的可靠性评价

硅集成电路技术的优势与挑战

集成电路的引脚识别及故障检测

【「大话芯片制造」阅读体验】+ 半导体工厂建设要求

未来五年中国集成电路与半导体设备防震基座需求预测

半导体集成电路芯片贴装的方法有哪些?

半导体集成电路芯片贴装的方法有哪些?

评论