手机上LPDDR5怎么看不到绕线等长设计?频率越来越高,为什么DDR绕线等长的要求却越来越低了?其实从LPDDR3开始,手机上很少有见到夸张的绕线了,都是直接芯片公司提供的DOME板来Copy线的。

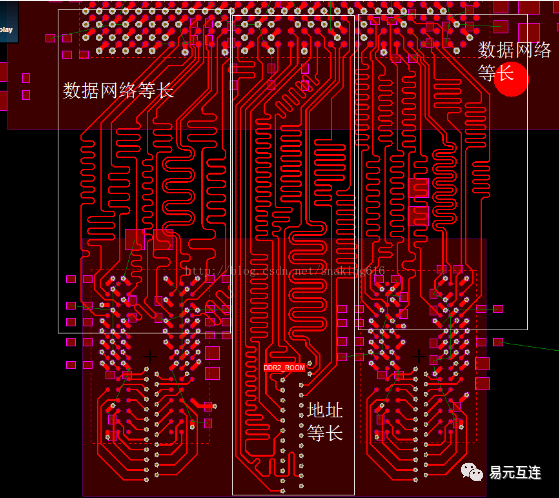

最早是做X86架构的电脑主机板的,DDR部分要单独分出一个人力来绕线的。首先,DDR绕线等长要考虑芯片内部长度(Pin Delay),也就是仅仅保证CPU到DDR的Pin to Pin的长度相等是不行的,要考虑CPU和DDR内部的芯片内部焊接长度Pin Delay,而且CLK线的长度要比Data线长出200mil左右。

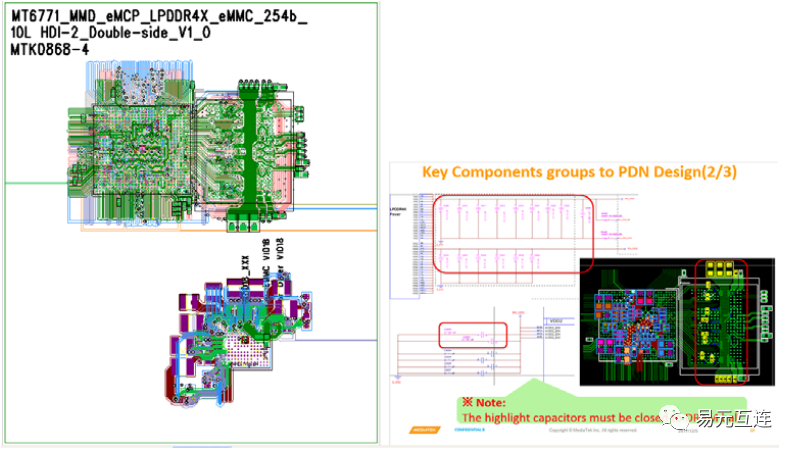

图 1 DDR绕线的PCB图

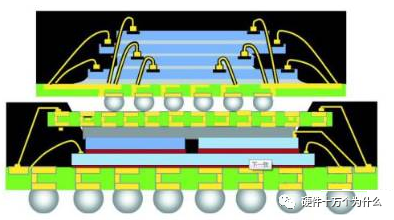

元件堆叠装配(PoP, Package on Package), 在底部元器件上面再放置元器件,逻辑+存储通常为2到4层,存储型PoP可达8层。外形高度会稍微高些,但是装配前各个器件可以单独测试,保障了更高的良品率,总的堆叠装配成本可降至最低。器件的组合可以由终端使用者自由选择, 对于3G移动电话,数码像机等这是优选装配方案。

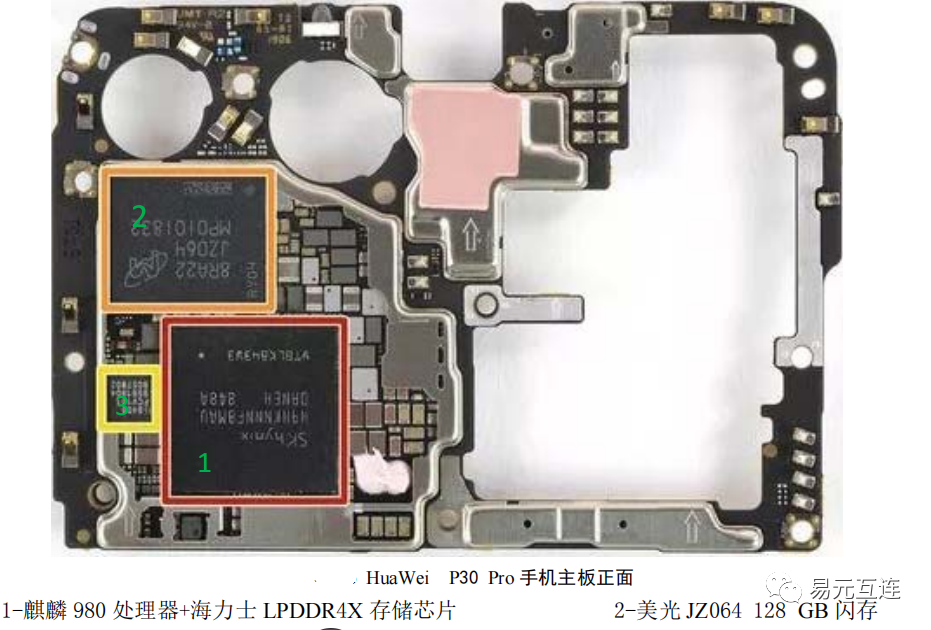

从 LPDDR4开始,手机线路板上大多使用POP焊接工艺,直接焊接在CPU的背部焊盘上,很少有见到在PCB板子上的,比如华为的P30,可以看到DDR的空间被一颗EMMC替代,DDR4和CPU已经使用POP工艺立体叠装在同一个地方了。

图 2 CPU与DDR的POP立体贴装工艺 那究竟为什么到DDR5,频率提高了,反而很少绕线了呢?答案是:不是不绕,而是绕了等长也没用。为了解答这个问题,不妨先一起来做一个仿真的习题。

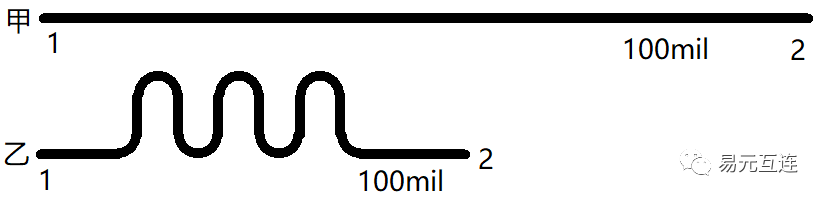

【题目】下图有甲乙两根都是100mil的信号线,如果各有一个高电位信号开始从1传输到2,哪根线的2端先收到信号?

图 3 【A】甲2先收到 【B】乙2先收到 【C】同时收到

如果把信号线当作一个高速公路,电荷是一辆车(当然电荷移动速度是很慢的),那肯定是直线路况最好,车速最快,应该选A;如果考虑到电流的速度都是按照6mil/ps,那就是虽然有拐弯,但整体路线长度是一样的,到达时间应该也是一样的,应该选C。

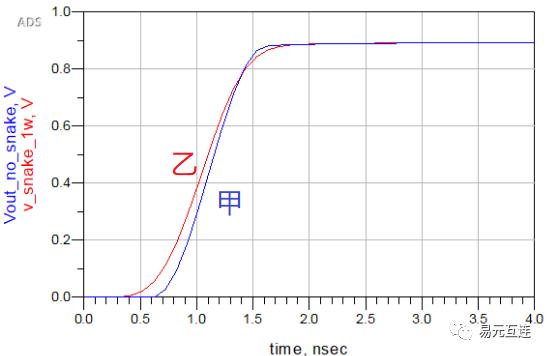

那到底是A还是C呢?使用ADS来对这两根信号线进行仿真,下图为仿真结果,蓝色和红色分别是甲和乙的时域波形图,可以看到乙刚开始一直领先的,在上升到0.8的时候,甲开始追上乙,然后提前到达0.9的高度上。至于为什么没有达到1那是另外一个问题,咱们不做考虑,那结果就是甲先到达了吗?当然不是这么简单的,衡量一个信号至高电平,一般下限为70%,也就是高电平是1V,到达0.7V就可以达到置1的效果,就像咱们考试,达到60分就及格了,不一定非要人人100分,信号也是如此的。

那接下来就要看甲和乙谁先到达0.7V的位置了,从上图很明显可以看到红色线首先到达0.7V的位置, 那就说明是乙先到的,所以答案不是A,也不是C,而是B,意不意外?

那接下来咱们就分析下为什么答案选B,首先在PCB上的铜箔走线是有宽度的,我们知道信号有个特性,就是会自动寻找最近的路径,比如两点信号总会寻找到最近的回流路径。可以把甲乙两根线看成一个跑道,而电子就是一个个的运动员,如果信号的频率很低,这些电子就可以迈着整齐的步伐跑步了,就像咱们上学时候的早上出操,可以保持队形。

但进入高频以后就不一样了,就像咱们1000米跑步,大家都知道内侧的距离最短,都会争抢着去跑道的内侧,这个时候就无法保持原来整齐的队形了。

电子也是一样的,它就像赛车手一样,很聪明的自动寻找内侧的最短路径,如下图中绿色的路径,这样就造成了实际的路径长度要远远小于100mil, 弯曲的部分越多,实际的路径就越短。

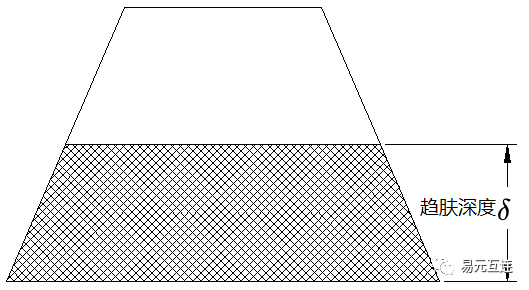

但这个问题还没有结束,我们知道PCB上铜箔不仅有宽度,还有厚度,由于蚀刻的原因,铜箔的横截面形成上窄下宽的梯形结构。由于高频中存在趋肤效应,所有的电子都是走在趋肤深度范围内的,如下图所示。阴影部分是电子通过的空间,上部白色部分,实际上是没有作用的,这也就是高频板的铜箔为什么都是很薄的,因为厚了也没什么效果,反而会浪费钱,就像路修的再宽,也没有车子通过一样的道理。

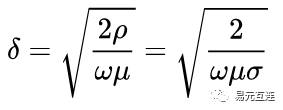

这是趋肤深度的计算公式,可以看到趋肤深度和频率是反比关系。

频率越高,趋肤深度就越小,电子回流路径就越贴近PCB板。了解了趋肤深度和频率的关系,我们再回头看图6,趋肤深度越小,就意味着铜箔的宽度越宽,因为梯形结构,越往下宽度越大。线路越宽,也就代表着走内侧的路径就会更短,这个应该可以想象出来的,如果乙的线宽0.1mm,走内的距离是98mil,那如果线宽是0.12mm,那走内侧的距离可能就是96mil。

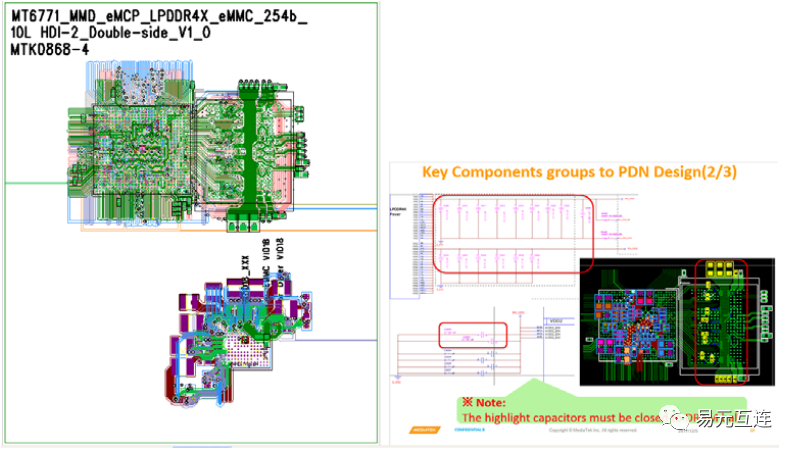

所以,最终得出的结论是:频率越高,线路弯曲造成的实际传输距离差异就越大。绕线做等长,反而没有好处,既然绕线等长没有效果,那如何保证信号同步呢?那这个答案是只有通过仿真。 但很多公司都没有仿真工程师的职位,而且仿真要占据很多的时间。这个时候芯片厂家的 Turn key 服务就很到位,会提供仿真好的CPU和DDR的线路给ODM和品牌商,如下图是MTK公司提供的MT6771的PCB图,而且不同的层数和阶数也会有不同的PCB图提供。

MT6771的DDR和CPU走线 有了厂家提供的走线,设计公司只要直接copy过来使用就可以了,包括CPU和DDR的相对位置都要一模一样,所有的DDR线不能做任何更改,包括删掉一个GND孔。这也就是手机设计中EDA工程师不需要自己走DDR线的原因,当然厂家提供的DDR走线肯定也没有做等长绕线的。

审核编辑 :李倩

-

元器件

+关注

关注

113文章

4946浏览量

98187 -

cpu

+关注

关注

68文章

11217浏览量

222952 -

DDR

+关注

关注

11文章

747浏览量

68531

发布评论请先 登录

趋肤效应对DDR走线绕等长的影响

趋肤效应对DDR走线绕等长的影响

评论