我们不断向先进的CMOS的微缩和新存储技术的转型,导致半导体器件结构的日益复杂化。例如,在3D NAND内存中,容量的扩展通过垂直堆栈层数的增加来实现,在保持平面缩放比例恒定的情况下,这带来了更高深宽比图形刻蚀工艺上的挑战,同时将更多的阶梯连接出来也更加困难。人们通过独特的整合和图案设计方案来解决工艺微缩带来的挑战,但又引入了设计规则方面的难题。

二维 (2D) 设计规则检查 (DRC) 已不足以用来规范设计以达成特定性能和良率目标的要求。同时完全依赖实验设计 (DOE) 来进行工艺表征和优化也变得难以操作。以往工程师通过运用DOE实验来节省工艺研发的成本和时间,而现在他们需要进行数以百计的DOE才能达到目的,这反而需要大量的时间和物料,包括晶圆。

此外,工艺步骤之间非直观的交互作用,以及狭窄的工艺窗口,使得使用第一性原理建模来同时进行性能提升和良率优化变得尤为困难。因此需要对复杂工艺流程进行三维建模理解,而虚拟制造建模平台Coventor SEMulator3D为此而生。

SEMulator3D能提供哪些功能?

该软件可从一系列标准单元工艺步骤中创建3D虚拟工艺整合模型,以模拟工艺流程。SEMulator3D使用完全整合的工艺流程模型,可以预测工艺更改对下游工艺步骤的影响,这在过去则需要在晶圆厂中依靠“先制造和后测试”的循环来实现。

例如,工程师可以使用该软件对替换金属栅极 (RMG) FinFET进行快速建模,该元件使用先沟槽金属硬掩模 (TFMHM) 后段制程 (BEOL) 与自对准通孔工艺 (SAV)。工程师在完成虚拟加工的3D模型之后,就可以进行2D和3D的虚拟测量和电学性能参数提取。

该软件的电学分析组件增加了电阻和电容提取功能,有助于理解工艺和设计灵敏度。该软件提供了3D建模和验证电学性能的快捷平台。SEMulator3D中使用了有预测性的工艺模型和能精确匹配实际晶圆的3D结构,比其它孤立解决方案中使用的理想化几何结构,更能精确地反映所制造的器件,从而具有更高的精度。

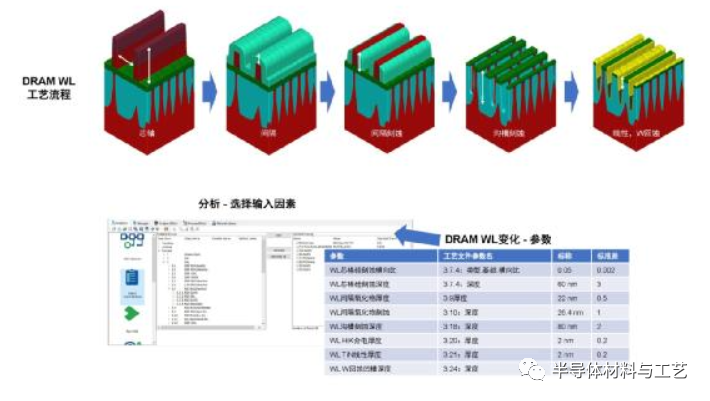

DRAM演示

该演示展现了该平台如何根据刻蚀设备的性能参数(如材料的刻蚀选择比和气流流向通量分布)的变化对器件电学性能进行建模,形象地说明了虚拟制造的案例。简单的DRAM器件案例研究侧重于对栅极刻蚀行为和刻蚀特征的研究,通过对其做合理设定来满足预先设定的电学性能和良率目标。

该演示在虚拟制造中使用了典型的工作流程,包括四个步骤:

1一个标准工艺流程的建立,此艺流程支持工艺校准,然后生成具有预测性的3D结构模型。

2添加量测参数,以评价器件结构或电学行为。量测可能包括几何尺寸测量、3D DRC(设计规则检查)和电学参数测量。

3使用DOE(实验设计)和校准。

4数据分析,包括对工艺实现和/或设计变更的敏感性分析。

标准工艺流程的建立

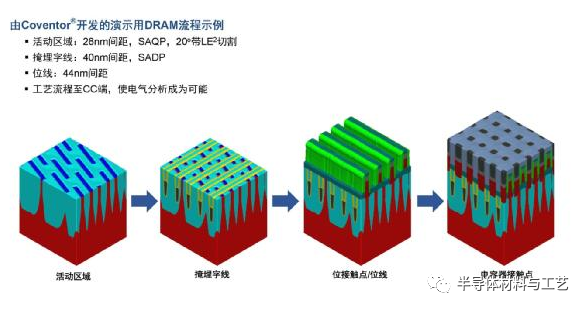

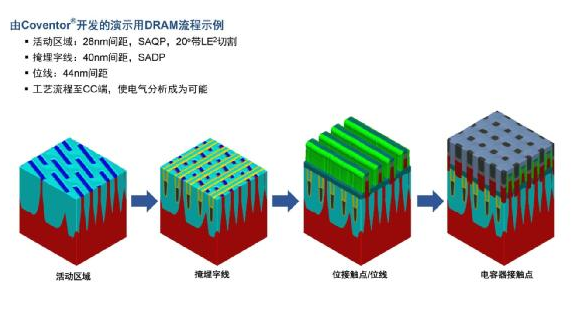

该演示的标准工艺流程面向2X DRAM。该工艺由Coventor根据公开数据开发,未使用客户机密信息

图1:建立模型之后,电容器接触点结果如图所示。此时可以进行电学分析,研究电容器的边缘效应。

在本演示中,DRAM的有源区 (AA) 使用自对准四重图形技术 (SAQP) 和倾角20°的光刻-刻蚀-光刻-刻蚀 (LELE或LE2) 对多余的图形进行去除,其间距为28 nm。掩埋字线使用自对准双重图形化技术 (SADP),间距为40 nm,位线使用SADP,间距为44 nm。工艺流程在电容器接触点 (CC) 处结束,这使得软件可以进行电学分析,并能够分析电容器中的边缘效应。

添加重要度量

每个工艺步骤只需要几个易于理解和校准的几何和物理输入参数。工作流程的下一步是确定重要量工艺参数。就像在实际的晶圆厂一样,单元工艺参数,如沉积一致性、刻蚀的各向异性和选择比,他们之间相互影响并与其它设计参数交互作用,最终以复杂的方式影响最终器件的结构。

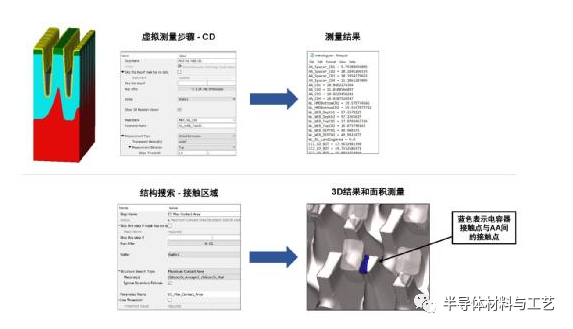

SEMulator3D支持添加两种几何测量。第一种是虚拟测量,支持测量模型结构并验证结构是否符合预期尺寸。第二种是结构搜索,相关步骤可以检查整个3D模型或某些部分,以确定测量极值,如膜厚度、线宽和接触面积的数值和位置。它还可以计算电网组件的数量,这有助于识别电网短路或开路(图2)。

图2:虚拟测量步骤(顶部)可帮助测量结构,包括CD、刻蚀深度和薄膜厚度。结构搜索步骤(底部)可确定测量极值,并计算电网组件的数量,如识别网络短路或开路。

当几何偏差的位置随工艺的变化而变化时,结构搜索特别有用。例如,图2显示了CC和AA之间的接口最小面积。软件将高亮显示该位置,而该位置容易成为器件失效的故障点。

器件电学性能模拟

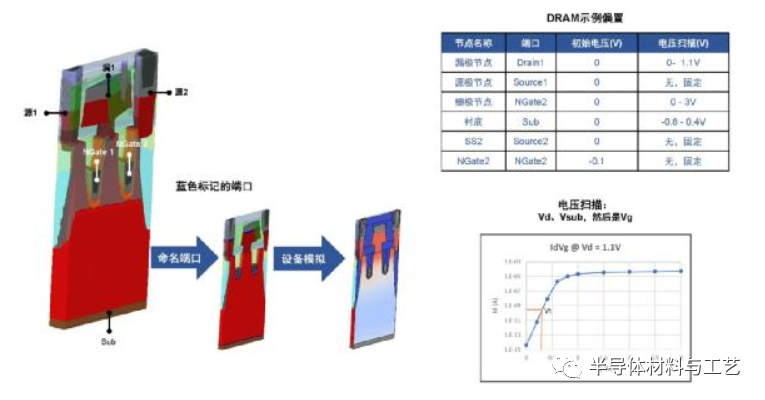

器件的电学性能参数可以通过器件电学性能模拟来提取。通过使用与图2相同的模型,该演示可以在SEMulator3D中进行器件电学仿真。

图3:SEMulator3D可识别3D结构中的器件端口,并像TCAD中那样仿真电学性能,但不需要进行耗时的TCAD建模。

该软件有助于识别3D结构中的器件的端口和电极,并模拟器件的特性,如温度、带隙和电子/孔迁移率。该软件允许手动和自动识别节点(一个或多个连接在一起的引脚),初始电压或电流可以与选定节点的电压扫描一起设置。

图3中的电学仿真示例显示了两个栅极、两个源、一个漏和一个衬底。工程师可以自由设置偏置电压或初始电压以及电压扫描,如DRAM示例偏置电压表所示。

然后,工程师可以使用该软件自动提取重要电学性能指标,如一个电压点上的阈值电压 (Vth)、亚阈值摆幅 (SS)、漏致势垒下降 (DIBL) 和开启电流 (ION)。这些功能无需耗时和严格的TCAD建模即可实现,同时可以体现3D工艺变化对电学性能的影响。

物理结构变化的影响

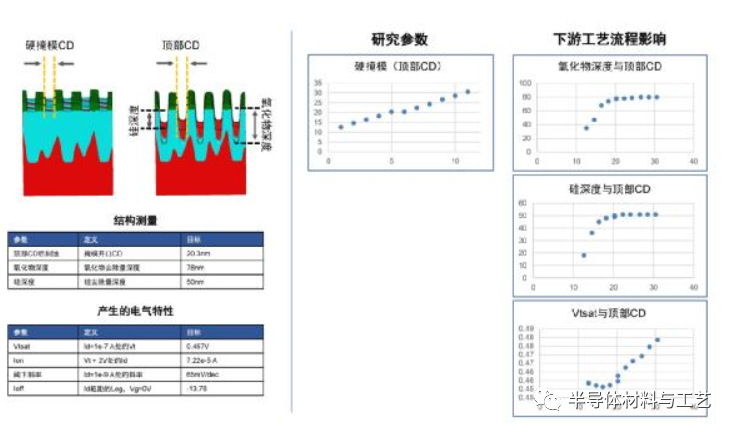

对由物理结构改变造成的影响的研究,首先需要检查标准模型中的参数的设定,包括硬掩模CD/顶部CD、硅深度和氧化物深度。SEMulator3D使用以上参数构建模型然后提取对应的器件电学参数(包括Vt、ION、IOFF和亚阈值摆幅)(图4,左侧)。

图4:研究标准模型(左侧)的物理结构变化的影响。使用SEMulator3D(右侧)进行的实验表明,氧化物深度和硅深度对CD变化的敏感性在20nm以上降低,而Vtsat敏感性在相同范围内增加。

本研究的目的是将图4中的硬掩模CD以2 nm的增量从12 nm变化至30 nm,同时监测其他结构参数,包括硅深度和氧化物刻蚀。此变化是通过更改流程早期工艺步骤来实现的,并且下游工艺步骤对模型更改的响应符合预测。

图4(右侧)显示,硬掩模CD变化对栅极刻蚀具有非线性响应。氧化物深度和顶部硅深度对较小CD的顶部CD很敏感,但在较大CD上趋于饱和。另一方面,当CD高于20 nm标准值时,Vtsat值显著增加。因此,SEMulator3D的指标揭示了对单个物理结构变化的各种响应,有利于工程师研究物理结构变化对所选参数造成的影响。

识别重要的工艺步骤

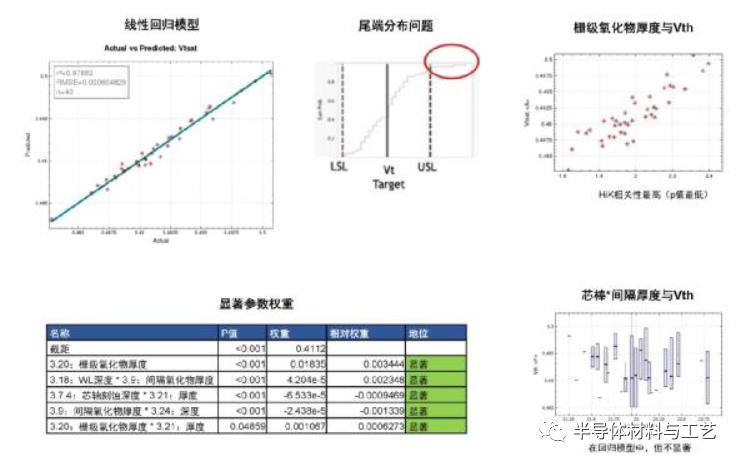

下一步DOE,包括蒙特卡罗变异性研究,以确定重要的工艺步骤(图5)。在参数变化研究中,采用了蒙特卡罗方法对DRAM字线 (WL) 深度进行变化。

图5:SEMulator3D利用数百甚至数千次DOE试验,使用回归分析来识别对特定指标有显著影响的关键工艺参数。

WL工艺参数值是通过基于平均值或标准值和标准差的高斯分布随机设置的。演示中选择了50个实验。然而,通常至少需要100个实验才能获得有意义的研究。

DOE的结果如图6所示。DOE运行时,阈值电压Vt在0.4837 V和0.5031 V之间变化。SEMulator3D的回归分析有助于识别对阈值电压影响显著的5个参数,这些参数的p值小于0.5,不支持原假设。注意,第一个参数(截距)被排除在本讨论之外,因为它始终是列表的一部分。

图6:工程师可以在SEMulator3D中分析任何量测结果,以识别重要参数,极端情况如上图所示(红色圈出)。

有待进一步研究的五个最重要的因素是:

1栅极介电层厚度(最重要的参数)

2字线刻蚀深度和侧墙厚度的交叉项

3芯轴刻蚀深度和栅极厚度的交叉项

4间隔氧化物厚度和抛光深度的交叉项,以及

5栅极介电厚度和侧墙厚度的交叉项。

线性回归曲线的R方值 (r2) 为0.97882,说明模型与数据吻合较好。栅极氧化层厚度与Vth图显示出很强的相关性,而芯棒间隔厚度与Vth图则没有相关性,因此可以认为它不是一个重要参数。

DOE的结果还可以帮助识别一些特殊情况,例如规格下限 (LSL) 到规格上限 (USL) 范围之外的Vth,使工程师可以仔细检查况并找到造成这种结果的工艺条件。

工艺优化

为了从不同的角度进行优化,我们可以将电学性能作为研究的目标。可以使用电学性能参数目标值作为工艺步骤优化的目标。每个工艺步骤参数都可以改变,以寻找满足电气性能的条件。

根据所使用的制造设备,在软件中定义了每个刻蚀行为的允许范围。因此,可以根据材料的刻蚀选择比、横向比、聚合/锥度、溅射和离子通量分布等参数来定义刻蚀行为。利用DOE确定的重要输入参数,输入电学性能指标。

SEMulator3D采用直接优化的方法,以确定WL刻蚀工艺中最佳刻蚀步骤行为的工艺参数,以满足电学性能目标。校准工艺建议包括氧化层,硅和氮化层的刻蚀选择比、氧化层和硅的刻蚀角度和选择比等参数。

根据这些结果,可以通过工艺研究验证是否存在满足条件的电学性能,或者在此范围内是否无法实现特定的电学性能。

虚拟工艺节省了成本和时间

由于工艺假设是在开发早期甚至在硬件实现之前完成的,因此虚拟工艺无需制造真正的晶圆,即可验证这些假设,节省了时间和费用。

该DRAM案例研究表明,通过在虚拟环境中执行大量的DOE和工艺变化研究,可以消除不相关DOE路径的时间和成本,并快速实现性能和良率目标,从而加快产品上市时间。

审核编辑:汤梓红

-

CMOS

+关注

关注

58文章

6189浏览量

241582 -

DRAM

+关注

关注

40文章

2373浏览量

188173 -

虚拟工艺

+关注

关注

0文章

5浏览量

6429

原文标题:借助虚拟工艺加速CMOS工艺优化

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

借助虚拟工艺加速工艺优化

请问DAC7731的数字部分是bipolar工艺还是cmos工艺?

CMOS,Bipolar,FET这三种工艺的优缺点是什么?

怎么采用标准CMOS工艺设计RF集成电路?

《炬丰科技-半导体工艺》CMOS 单元工艺

IC工艺,CMOS工艺,MEMS工艺有什么关系和区别?

如何使用虚拟工艺加速工艺优化

通过虚拟工艺加速工艺优化

什么是BCD工艺?BCD工艺与CMOS工艺对比

HV-CMOS工艺制程技术简介

借助虚拟工艺加速CMOS工艺优化

借助虚拟工艺加速CMOS工艺优化

评论