几乎每个射频和微波系统都需要频率合成器。频率合成器产生本地振荡器信号,驱动混频器、调制器、解调器以及许多其他射频和微波组件。创建频率合成器(通常被认为是系统的心跳)的一种方法是使用锁相环(PLL)频率合成器。

传统上,一个简单的PLL对压控振荡器(VCO)输出频率进行划分,将其与参考信号进行比较,然后调整VCO控制电压以调整其输出频率。多年来,PLL和VCO一直是两个独立的芯片 - 分立解决方案。VCO 创建实际输出信号;PLL监视输出信号并调谐VCO以将其锁定相对于已知参考信号。

分立式解决方案有许多优点:

每个分立芯片都可以设计为提供其最佳性能。

PLL和VCO之间的物理距离降低了交叉耦合效应,并最大限度地减少了输出上不需要的杂散信号。

如果环路中的一个芯片损坏,则需要更换的组件更少。

分立式解决方案在合成器行业长期占据主导地位,但也有缺点。一个主要问题是分立解决方案需要大量的电路板空间来容纳两个芯片及其所有支持元件。这导致更大的最终产品和更高的成本。

分立式解决方案的另一个主要问题是传统VCO的输出频率范围很窄。典型VCO带宽为50 MHz至500 MHz;可以上升到2 GHz左右,但这需要一个基于运算放大器的有源滤波器。对于任何想要实现频率范围更宽的系统的人来说,这都是一个重大挑战。为了创建更宽的频率范围频率合成器,需要多个PLL、VCO、支持组件、滤波、开关和电源!这成倍增加电路板空间和设计成本。分立式解决方案不仅会影响电路板设计,而且在确定、创建软件和控制每个器件的库存方面还有大量的开销工作。

大约 10 年前,基于 PLL 的合成器行业取得了突破。第一个集成的PLL和VCO(PLL/VCO)开始出现在市场上。这一重大发展意味着电路板可以更小,成本可以更低,开销可以大大减少。集成解决方案还意味着VCO架构可以改变,从一个组件创建宽带频率合成器。让我们探讨一下VCO架构,以及向集成VCO的转变如何打开了频率合成器性能的大门。

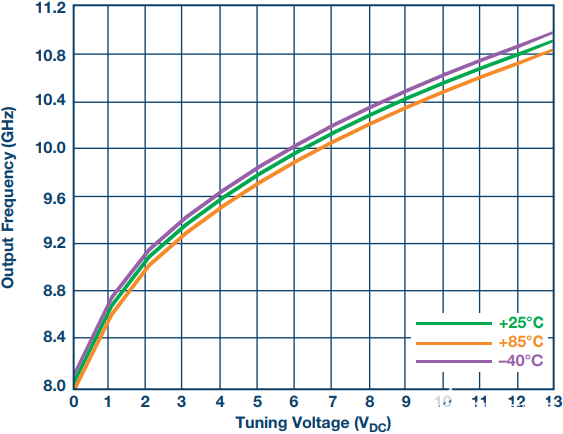

传统的VCO是简单的器件——电压施加到VCO上的调谐引脚,并输出一定的频率;电压增加,输出频率增加;电压降低,输出频率降低。图1显示了GaAs MMIC VCO的调谐电压与输出频率的示例——13 V调谐范围需要有源滤波器或带高压电荷泵的PLL。

图1.传统VCO——调谐电压与输出频率的关系。

集成的 PLL/VCO 解决方案使用基于传统架构的不同类型的 VCO 架构。集成的PLL/VCO有效地并排结合了多个传统VCO,以创建具有极宽带宽的VCO。每个单独的VCO(通过切换电容器输入和输出)称为频段。PLL和VCO集成在一个芯片上,这使得多频段架构成为可能。每当用户想要锁定到新频率时,器件都会启动VCO校准过程,芯片快速对VCO频段进行分类,并为所需的输出频率选择最佳频段。一旦选择了VCO频段,PLL就会锁定环路,并将输出保持在所需的频率。

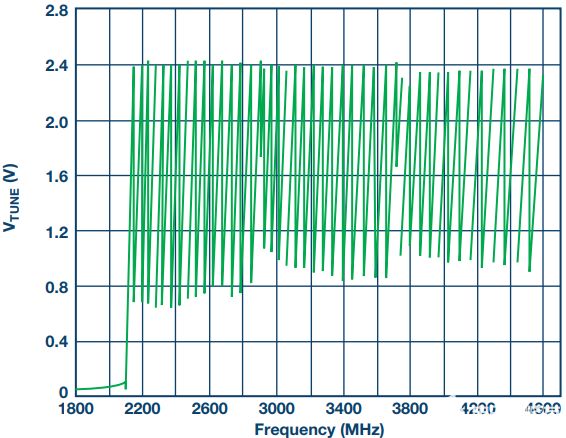

第一代PLL/VCO芯片的带宽超过4 GHz!将其与分立的100 MHz至300 MHz带宽进行比较,相对于以前所需的PLL、VCO、滤波器和开关组,该频率范围可以从微小的芯片实现。图2显示了多频段PLL/VCO的调谐电压与输出频率的关系。在本例中,基波VCO输出范围指定为2200 MHz至4400 MHz。在VCO输出之后,在芯片内部有一组分频器,可以将信号分频至低至35 MHz;因此,>4 GHz 带宽全部来自一个 5 mm × 5 mm 封装。

图2.多频段VCO—调谐电压与输出频率的关系。

虽然这项突破性技术在频率范围、电路板空间、成本和开销方面向前迈出了一大步,但仍存在一些缺点,使集成解决方案无法完全取代分立式解决方案。在许多应用中,最重要的性能规格(频率范围之后)是相位噪声。

为什么相位噪声如此重要?想象一个通过晴朗空气传输信号的系统。假设发射天线处传输信号的信噪比为 50 dB。这意味着,接收器应该接收的信号比传输信号两侧的噪声强 50 dB;也就是说,在附近的较高和较低频率下。假设该信号可以在信号功率衰减为噪声并且传输丢失之前传播 10 英里。现在,假设频率合成器的相位噪声提高了3 dB。这意味着传输信号的信噪比为53 dB。因此,传输的信号功率是之前的10英里范围信号的两倍,因此可以在衰减成噪声之前传播得更远。更远的距离意味着需要更少的中继器/发射器,并且可以降低成本。

除了这个通信示例之外,电子测试和测量界还推动了相位噪声性能。无论通信行业使用何种相位噪声性能,电子测试和测量仪器都需要更好的相位噪声性能,以便能够测量通信协议。

虽然许多解决方案能够从分立式转向集成式,从而节省数百万美元,但第一代PLL/VCO的相位噪声性能根本不足以取代许多低相位噪声要求的应用。除了相位噪声性能外,与许多需要分立PLL和VCO的应用相比,频率范围仍然相当低。

频率范围问题可以通过倍频器和其他乘法器来缓解,但这些倍频器耗电,会增加解决方案的成本和电路板空间。

幸运的是,在推出这些集成解决方案的同时,已经开始开发新的IC工艺,以实现备受追捧的相位噪声和频率范围改进。

因此,在这一点上,第二代集成PLL/VCO已经准备就绪。要求是:

输出频率大于 4.4 GHz。

相位噪声性能可与分立解决方案相媲美。

集成在单个小型封装中的PLL和VCO。

成本低于分立式解决方案。

2014年底,第二代集成PLL/VCO问世。产品开始出现在市场上,其输出频率范围大于10 GHz,相位噪声可与分立VCO相媲美,5 mm×5 mm封装,价格低于类似的分立PLL和VCO解决方案(频率范围要窄得多)。

例如,ADI公司的ADF4355系列满足了第二代产品的所有要求:

输出频率为 50 MHz 至 13.6 GHz(一个端口为 ≤6.8 GHz,≥另一个端口为 6.8 GHz)。

相位噪声:

10 GHz 时的传统分立式 VCO:100 kHz 偏移时为 –110 dBc/Hz,1 MHz 偏移时为 –135 dBc/Hz。分立VCO在频率范围和相位噪声性能之间进行权衡。

ADF4355系列在10 GHz时:100 kHz失调时为–106.5 dBc/Hz,在1 MHz偏移时为–130 dBc/Hz。

5 mm × 5 mm LFCSP 封装。

各个系列的价格各不相同,但成本低于分立式解决方案。

现在,用户可以享受分立解决方案的所有相位噪声性能优势,以及集成解决方案的所有其他优势。作为额外的好处,PLL技术也经过多年的发展,因此第二代PLL/VCO器件也具有各种PLL性能增强功能。

对于第一代PLL/VCO,PLL模块的最大鉴频检测器(PFD)频率约为32 MHz,小数N分频器分辨率约为12位。这种组合意味着典型的通道分辨率在几十千赫兹。第二代PLL/VCO的最大PFD频率大于100 MHz,小数N分频器分辨率为25位甚至高达49位。这有两个主要好处——更高的PFD频率允许更低的PLL相位噪声(PFD频率每增加一倍意味着N分压器可以减半,因此N分压器噪声贡献下降3 dB);25 位甚至更高的分辨率可实现精确的频率生成和亚 Hz 通道间隔。

杂散性能

集成PLL/VCO的一个重要方面需要讨论。上面列出的分立解决方案的优点之一是,两个芯片之间的物理隔离减少了PLL和VCO之间的交叉耦合,从而降低了不需要的杂散信号的功率。当PLL和VCO集成时,杂散性能不可避免地会下降。市场上的一些器件设法将这种衰减保持在非常低的水平,并且对于PLL/VCO而言具有令人惊讶的良好杂散性能,例如HMC830。其他PLL/VCO器件需要额外的应用工作,以改善某些高性能产品的杂散水平。

改变PFD频率以消除整数边界杂散

一种技术是使用频率规划算法改变PLL的PFD频率。这可以将由PFD块引起的杂散信号移动到它们没有强烈影响并且几乎被消除的区域。本文“分析、优化和消除具有高达 13.6 GHz VCO 的锁相环中的整数边界杂散”中对此进行了详细介绍。

隔离锁相环和虚拟通道

如上所述,PLL和VCO电路的紧密接近会导致不必要的耦合。为了缓解这种情况,可以使用两种芯片解决方案来物理分离PLL和VCO电路。这提供了低杂散信号的分立优势和宽输出频率范围的集成优势。

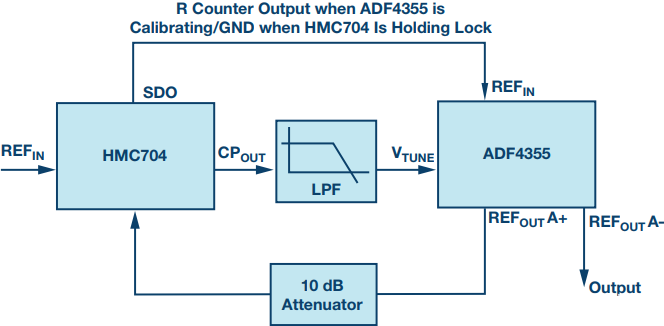

ADI公司的分立式小数N分频PLL产品组合的HMC704非常适合此任务。在该解决方案中,其中一个VCO输出信号(所有ADF4355系列都有两个输出)馈送到HMC704(该信号上的可选10 dB衰减器有助于进一步降低杂散电平)。ADF4355 PLL最初用于完成VCO校准并锁定至所需频率。然后,ADF4355 PLL部分可以关闭,方法是对电荷泵进行三重处理并保持计数器复位,从而消除PLL中的任何杂散,HMC704将保持环路锁定。这样做有几个好处:

在与VCO不同的芯片中使用PLL可降低杂散功率。

HMC704固有的杂散性能优于ADF4355 PLL,因此杂散性能进一步降低。

HMC704的归一化相位本底噪声低于ADF4355 PLL,因此频率合成器输出端的噪声更低。

为了完成环路,HMC704电荷泵输出连接到环路滤波器。环路滤波器输出必须连接到ADF4355 VTUNE引脚。当环路锁定时,HMC704仅在PLL上工作,ADF5355仅作为VCO工作。为了完全消除ADF4355 PLL中的杂散,必须在不使用ADF4355 PLL时将ADF4355基准输入引脚接地。幸运的是,HMC704提供了一种简单的方法。HMC704具有通用输出(GPO)引脚——该引脚可直接连接到ADF4355基准输入引脚。当ADF4355需要基准信号(用于VCO校准)时,HMC704可以将其参考信号路由到GPO引脚;当需要将ADF4355基准输入引脚接地时,可以将HMC704编程为在GPO引脚上输出GND。图3显示了该电路。

图3.使用外部HMC704 PLL锁定ADF4355,以改善杂散性能。

ADI公司发布了具有第二代PLL/VCO性能的四款关键器件ADF4355系列。该系列中有四种设备;除了频率范围外,三个非常相似,一个是低功耗变体。

ADF4355-2:集成PLL/VCO,输出频率为53 MHz至4400 MHz。

ADF4355:集成PLL/VCO,输出频率为53 MHz至6800 MHz。

ADF5355:集成PLL/VCO,输出频率为53 MHz至13,600 MHz。

ADF4355-3:低功耗集成PLL/VCO,输出频率为51 MHz至6600 MHz。

审核编辑:郭婷

-

射频

+关注

关注

106文章

6121浏览量

173855 -

振荡器

+关注

关注

28文章

4192浏览量

143170 -

调制器

+关注

关注

3文章

978浏览量

48742

发布评论请先 登录

集成压控振荡器的宽带锁相环能够取代分立式解决方案吗?

集成压控振荡器的宽带锁相环真的能取代分立式解决方案吗?

TI推出业内最高性能宽频带RF锁相环并集成了压控振荡器

UG-1404:评估集成小数N锁相环和压控振荡器的ADMV4420,K波段下变频器

UG-742:评估集成小数N锁相环和压控振荡器的ADRF6720-27宽带正交调制器

集成压控振荡器的宽带锁相环能否取代分立式解决方案

集成压控振荡器的宽带锁相环能否取代分立式解决方案

评论