摘要

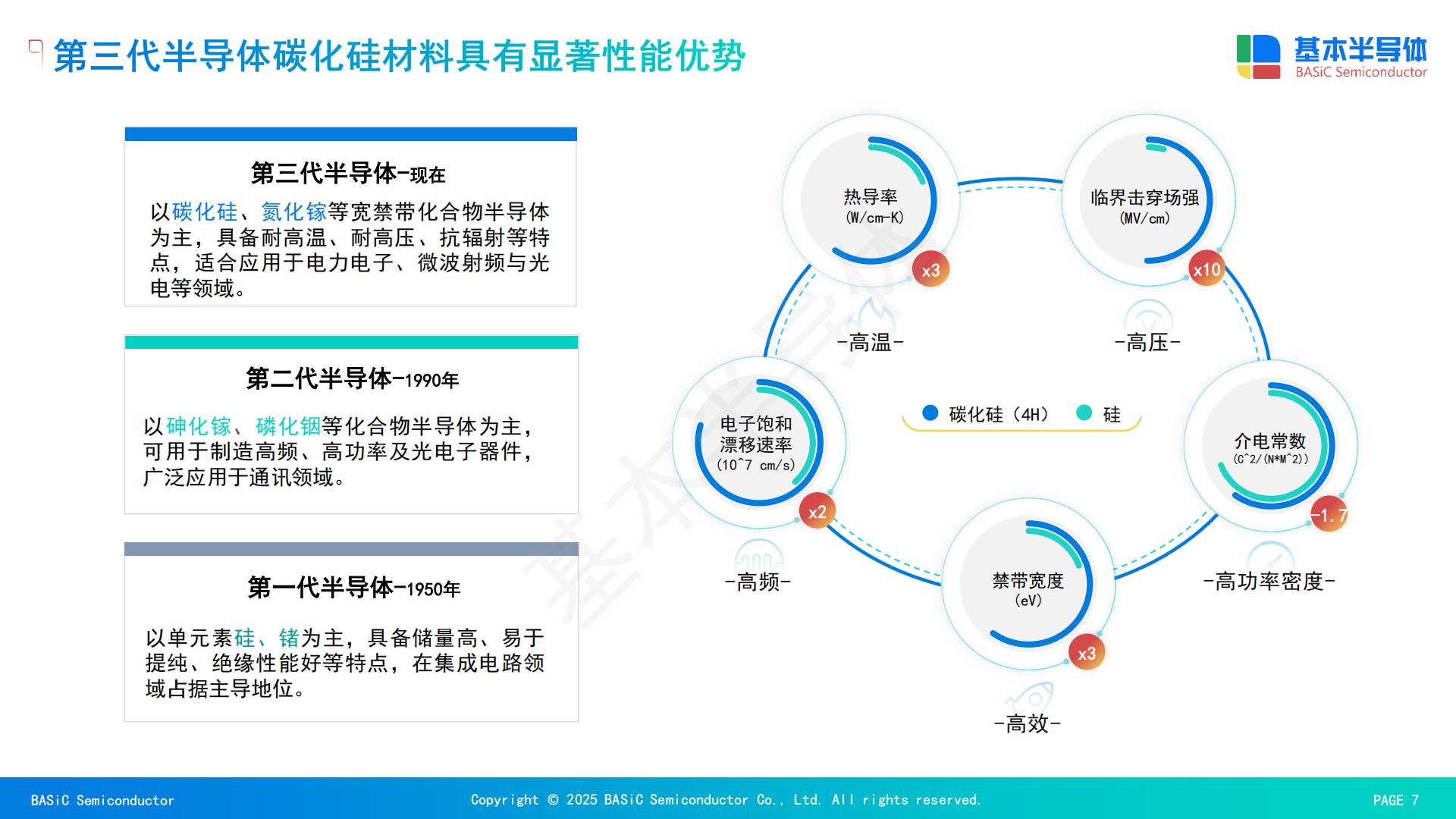

碳化硅(以下简称“SiC”)是制造高功率器件最有前景的半导体材料之一。借助其出色的物理特性(高饱和电子漂移速度、高热导率和高击穿电场), SiC MOSFET器件可以实现更低的损耗和更快的开关速度,并且其几何尺寸比硅 (Si) MOSFET更小。安森美(onsemi)充分利用多年来积累的Si 技术,针对 SiC 材料因尚未得到广泛评估所带来特殊挑战,我们为其量身定制了一套适用的评估方案,以证明其强固可靠性。

本白皮书将向读者介绍安森美从最初设计到批量生产过程中所采用的质量和可靠性方法,它们建立在不同领域之间的相互作用基础上,包括缜密的设计方法、严格的生产监控、制造控制、充分的筛选和稳健的认证计划。

这些方法在汽车市场应用了数十年,对于硅产品行之有效,现针对碳化硅产品的特殊需求重新进行定制。我们将带您了解 SiC 的演进,特别是其成功实现了 SiC MOSFET 晶体管的栅氧层的完备性。

最后,本文将简要介绍近期发表的有关低温偏置温度不稳定性、体二极管退化和动态应力要求等文章。

简介

单一产品的质量和可靠性,取决于从构思、交付到最终用户产品线的所有过程。安森美品质声明/政策充分体现了这种方法(图1)。

图1 安森美品质声明/政策

即使产品设计在高可靠性范围内,仍然可能会存在一些与制程相关的可靠性问题。

为了消除这些风险,我们必须了解限制性故障模式和机制,即通过故障的分析和反馈追溯至工艺薄弱点,并采取永久性的纠正措施。这是通过精心规划的晶圆及产品认证、缜密的设计方法、生产监控、制造控制和充分筛选来实现的。安森美在一般可靠性规范中简述了这些程序的使用方法,如以下海报“安森美的质量——零缺陷之路”所示(图2)。

图2 安森美质量——零缺陷之路

因此,安森美实施了三种不同的认证计划:晶圆制造认证、产品认证和封装路线认证。每个认证项目都明确关注了产品制造周期的其他领域,旨在确保目标领域的充分可靠性。

晶圆制造认证(也称为本征认证)主要关注晶圆制造的工艺制程——旨在确保按照合格流程处理的所有晶圆具有恒定的本征高可靠性水平。在这一阶段,将提取基于物理性质的退化模型。

产品和封装认证(也称为非本征认证)根据最终产品的任务剖面验证封装芯片的可靠性,最终目标是确保最终产品的高可靠性。

碳化硅挑战

碳化硅 (SiC) 材料兼具出色的物理属性和极具吸引力的设计特性,为研制高功率器件提供了卓越的解决方案。

在将产品投放市场时,必须兼具多个关键要素,如图3所示。

图3 强固的本征和非本征可靠性的定义

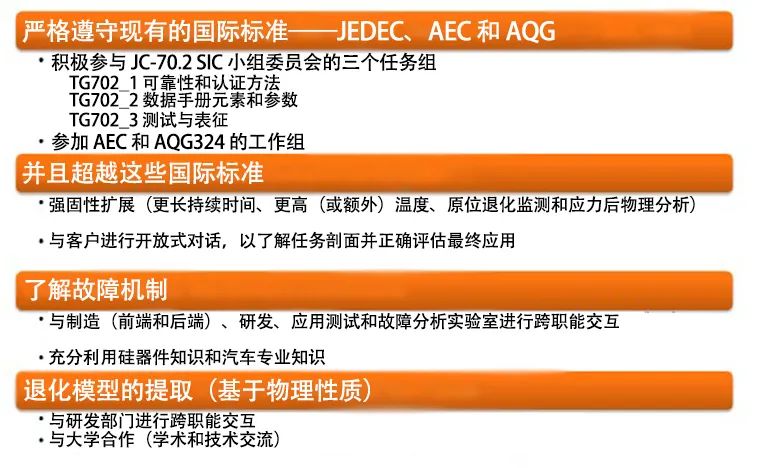

第一个挑战与国际标准的完备程度有关。虽然这些指南针对硅基技术已经做出明确的规定,但 JEDEC、AEC 和 AQG 委员会内的多个小组正在积极努力地为未来的 SiC 标准奠定良好的基础。这将确保让供应商通过统一的国际标准来获得指导,并避免对所收集数据的有效性进行冗长的论证。

第二个挑战是基于物理性质实现对故障机制的理解,以正确量化产品的强固性与客户所需的任务剖面。

与内燃机汽车相比,电动汽车通常具有扩展性任务剖面。此外,SiC 技术与传统Si技术或 IGBT 相比,性能得到了增强,这就要求在器件可靠性等方面更紧密地匹配最终客户的应用。

在此阶段,让跨职能团队(制造前端、研发、制造后端、应用测试和故障分析工程)参与进来是成功的关键,有助于在本征可靠性(寿命模型)和应用之间建立明确的联系。

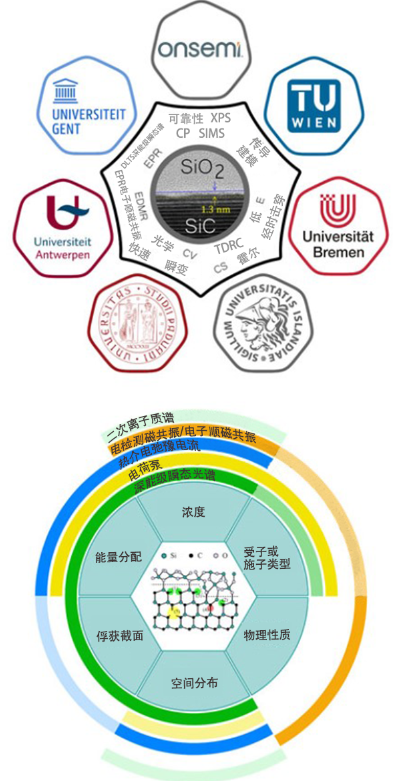

与大学和研究中心的密切合作至关重要,有助于安森美进行更深入的理论研究或获取一些半导体行业所不具备的专用技术和补充技能。图4说明了 SiC/SiO2 界面的表征和可靠性评估。

图4 与大学和研究中心合作——SiC/SiO2 界面

SiC通常需要解决以下难题:

◆衬底和外延的缺陷水平

◆栅极氧化物:本征寿命建模(SiC/SiO2界面表征)和非本征粒子数(筛选)

◆体二极管退化

◆高压阻断 (HTRB) 期间的可靠性

◆与应用相关的性能(雪崩强固性、边缘端接、短路、宇宙射线耐受性、高 dv/dt 耐受性设计、浪涌电流)

安森美方案

对于每种退化机制,安森美所采取的解决方案都是严格且跨职能的,主要步骤为控制 - 改进 - 测试和筛选 - 表征 - 验证和提取模型。

当应用于栅极氧化物完备性 (GOI) 时,这些步骤如下所述:

控制

制造 SiC (控制计划、统计过程控制和工艺 FMEA)的方法和工具准备就绪。收集数据,并将其用作潜在工艺改进的基础。

改进

由于衬底或外延的缺陷、金属污染物和颗粒会严重影响栅极氧化物的品质,因此持续改进并在控制下将其引入生产,对于进一步减少缺陷的发生至关重要。

测试和筛选

安森美开发了一整套用于视觉和电气性能的筛选工具,以剔除有缺陷的芯片。

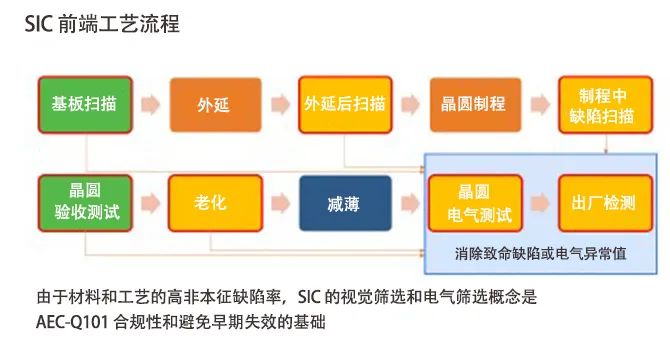

晶圆制造工艺流程从衬底扫描开始,通过坐标跟踪和自动分类识别所有缺陷。通过多重检测可识别关键工艺步骤中更多的潜在工艺缺陷。在上述检测中发现的所有标记缺陷均会被剔除(图5)。

图5 前端工艺中的扫描和检查

在多个层面实施电气筛选:

◆晶圆级性能和验收(参数测试和栅极氧化物完备性验收标准)

◆晶圆级老化

◆晶圆级芯片分选

◆使用动态器件均匀度测试,以消除电气异常值

最后,所有晶圆都经过 100% 自动出厂检测,包括外观缺陷检测。

表征

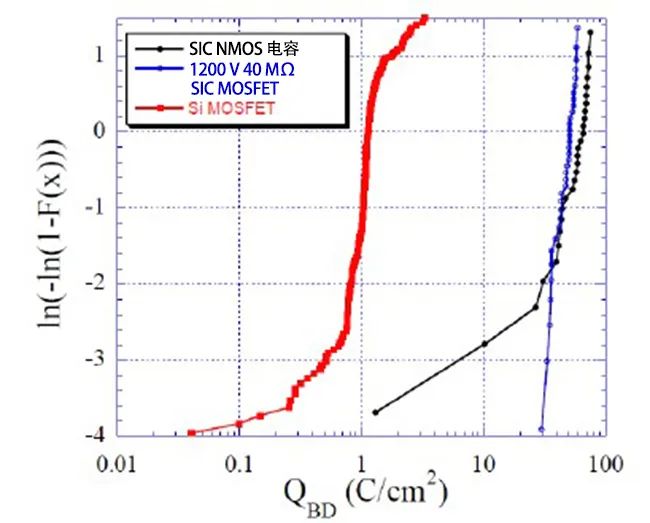

安森美使用失效电荷 (QBD) 作为一种简单的指标来比较与栅极氧化层厚度无关的栅极氧化层质量。这种技术比 GOI/Vramp 更精细,可以检测到本征分布中更精细的缺陷。

如图6所示,平面型 SiC 和 Si 栅极氧化物在击穿和寿命方面的本征性能相当。本征 QBD 性能(与栅极氧化物厚度无关)的对照比较表明,对于相同的标称厚度,安森美平面型 SiC 的本征性能比 Si 高 50 倍。

图6 在室温下使用正向偏置栅极施加 5 mA/cm2 时,SiC NMOS 电容、1200 V 40 mΩ SiC MOSFET 和 Si MOSFET 产品的 QBD 测量值

在生产过程中,通过对 SiC MOSFET 产品芯片的失效电荷(QBD)采样以及与大尺寸(2.7 mm x 2.7 mm)NMOS 电容进行比较,来评估每批产品的栅极氧化物质量。

验收标准就绪后,可在晶圆级选择接受或拒绝。

验证和提取模型

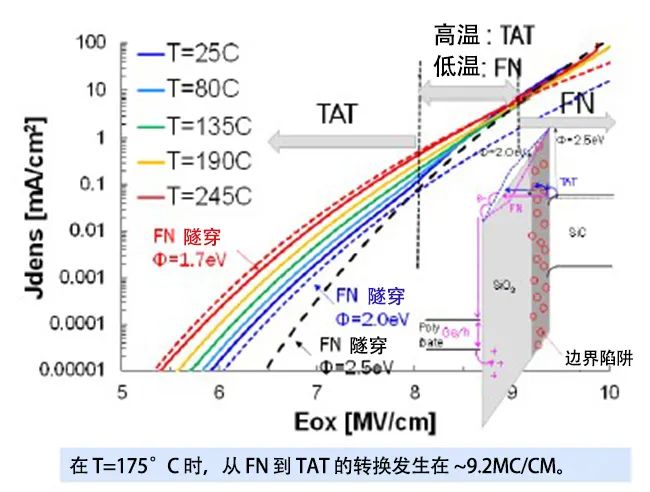

在定义应力条件时,确定栅极氧化物的真实电流传导机制至关重要[1]。热辅助隧穿与 Fowler Nordheim 隧穿竞争,与应力电场和应力温度成函数关系(图7)。

因此,了解传导机制可以防止在另一种传导模式下出现应力,以免无法代表实际使用条件。

图7 与温度和电场成函数关系的竞争性电流传导机制

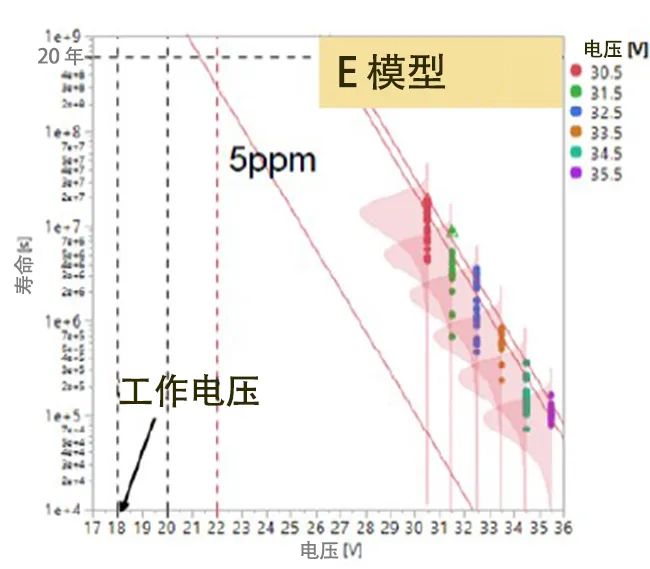

栅极氧化物的本征性能通过介质层时变击穿 (TDDB) 应力进行评估。在不同的栅极偏置和温度条件下对 SiC MOSFET 施加应力,并记录故障时间。然后使用 Weibull 统计分布来获取寿命结果。

到目前为止,我们已经使用了一种非常传统的方法:栅极电压 Arrhenius 温度加速和 E 模型。正在进行更为深入的研究以完善该模型;E 模型被认为过于保守。我们建立了长时间(t63% 为几个月到一年以上)、低电场强度的老化模型进行应力测试,通过实验来精确预测门极的可靠性。

图 8 显示了 SiC MOSFET 在 175℃ 的温度和发生电子俘获的氧化场(因此低于 9 MV/cm,另见图 7)下的 TDDB 数据,其故障模式与在实际情况下的预期相同。对于最低应力电压,记录了半年以上的故障时间。一个大学合作伙伴正在进行更低场条件下的实验,估计 t63% 为1到2年。使用保守的E模型,在5ppm 时,VGS=21V(远高于规定的工作电压),寿命可达 20 年。

图8 SiC MOSFET 的 TDDB 数据(应力条件为 175°C 且低于 9 MV/cm,即在电子俘获条件下,另见图7)

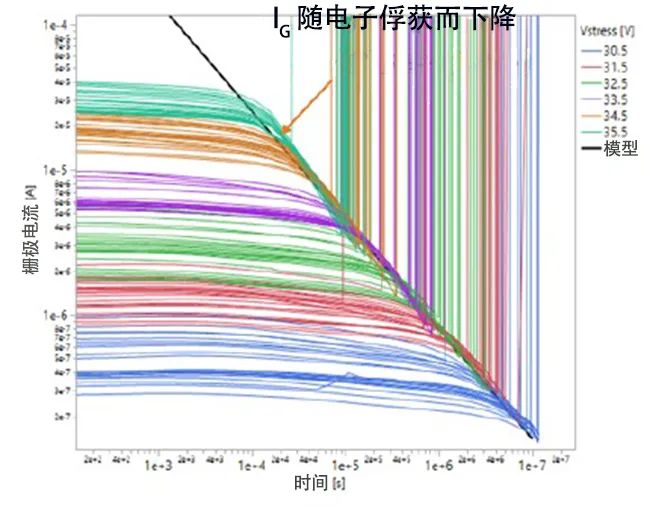

图 9 显示了 TDDB 应力期间各个 MOSFET 晶体管的 IG(t) 曲线(栅极电流与应力时间的函数关系)。栅极电流IG 保持恒定,直到达到特定的包络曲线,之后 IG 因俘获的电子而下降。该包络曲线反映了在晶体管参数受到影响之前,电介质可以承受的俘获电荷。该电荷比电介质的击穿电荷 (QBD)(即电介质击穿电荷)低约十倍,与 Si/SiO2 晶体管上获得的 QBD 相当。

图9 图8中所绘制的 TDDB 数据的 IG(t) 曲线(SiC MOSFET 应力条件为 T=175°C)

以上为本白皮书的第一部分,第二部分将于下周发布,敬请期待!

原文标题:碳化硅(SiC)——宽禁带半导体材料的征服之旅(第一部分)

文章出处:【微信公众号:安森美】欢迎添加关注!文章转载请注明出处。

-

安森美

+关注

关注

33文章

2153浏览量

95829

原文标题:碳化硅(SiC)——宽禁带半导体材料的征服之旅(第一部分)

文章出处:【微信号:onsemi-china,微信公众号:安森美】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

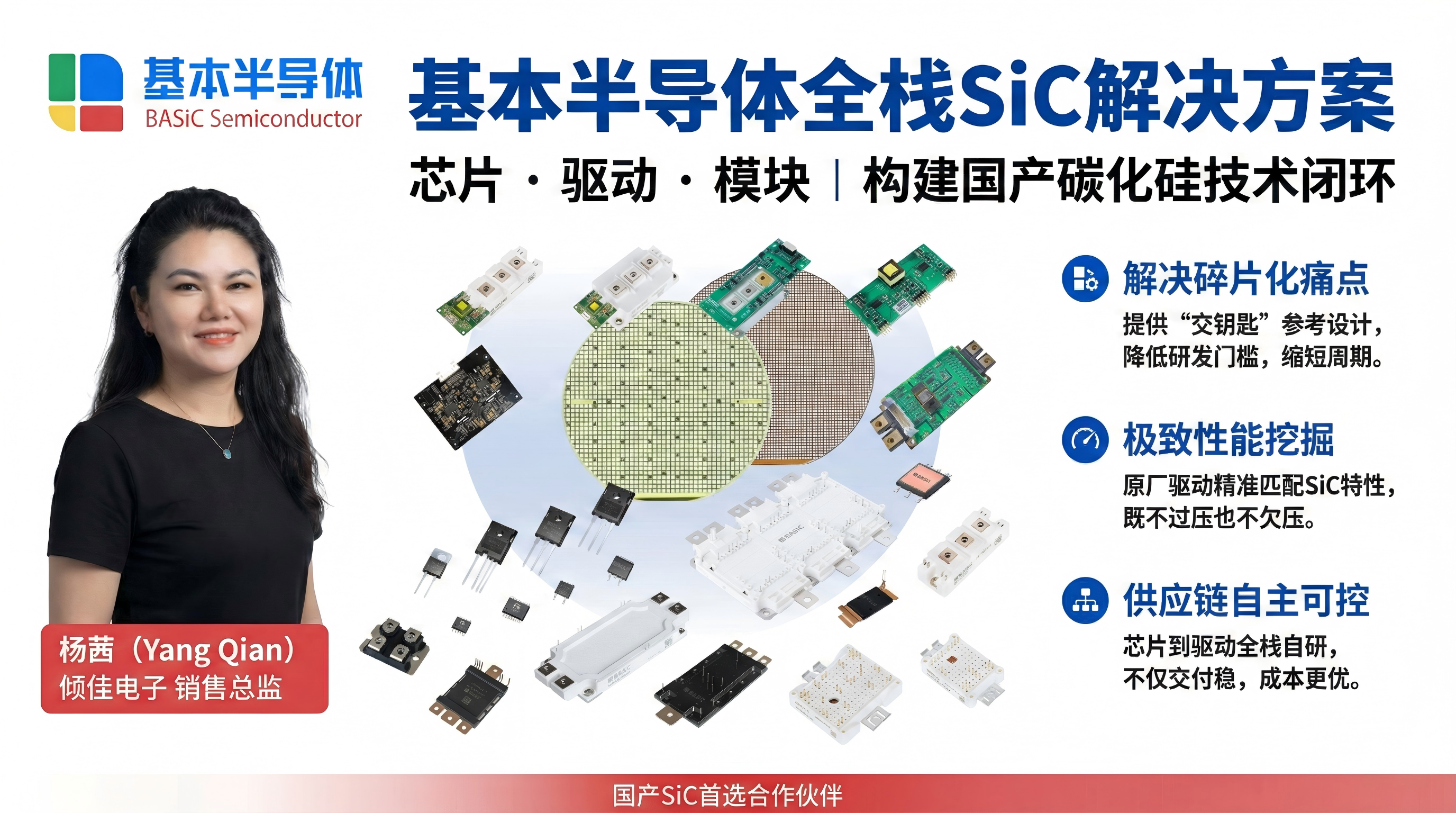

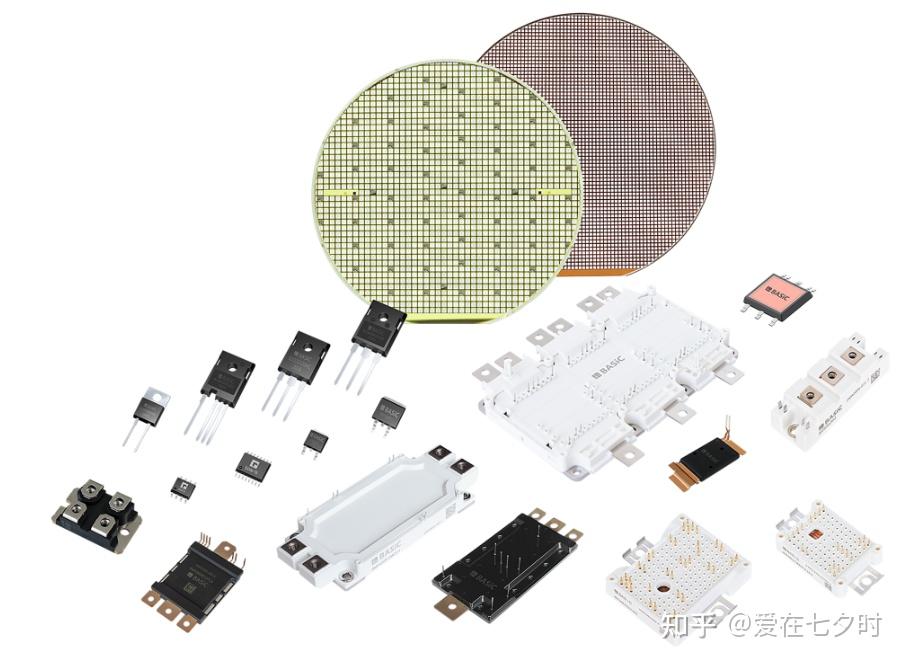

碳化硅MOSFET器件国产化替代深度分析:基于英飞凌与基本半导体产品的栅极驱动负压阈值与开关速度校准

宽禁带半导体软开关损耗分析及死区时间自优化算法:针对SiC的极致效率设计

宽禁带电力电子转换半导体工业标准深度分析:JEDEC JC-70 委员会规程对SiC碳化硅器件寿命评估框架

“三个必然”战略论断下的SiC碳化硅功率半导体产业演进与自主可控之路

基本半导体650V碳化硅MOSFET产品线深度研究报告

碳化硅(SiC)——宽禁带半导体材料的征服之旅(第一部分)

碳化硅(SiC)——宽禁带半导体材料的征服之旅(第一部分)

评论