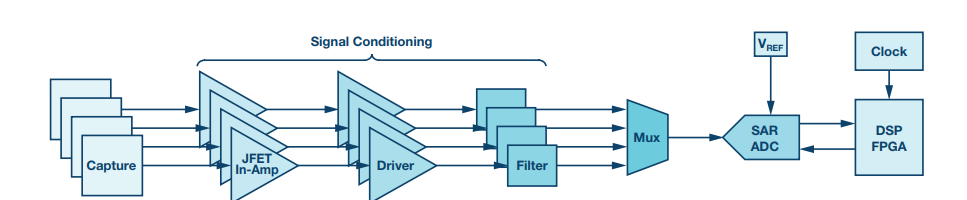

图1. 典型测量信号链

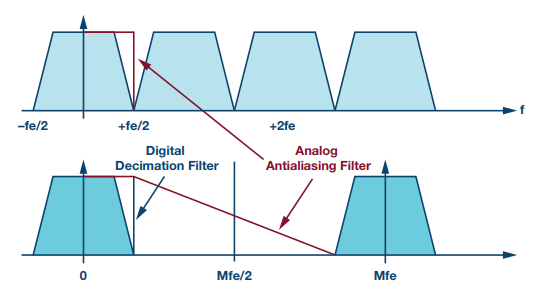

图2.通过添加数字抽取滤波器比较频谱噪声密度

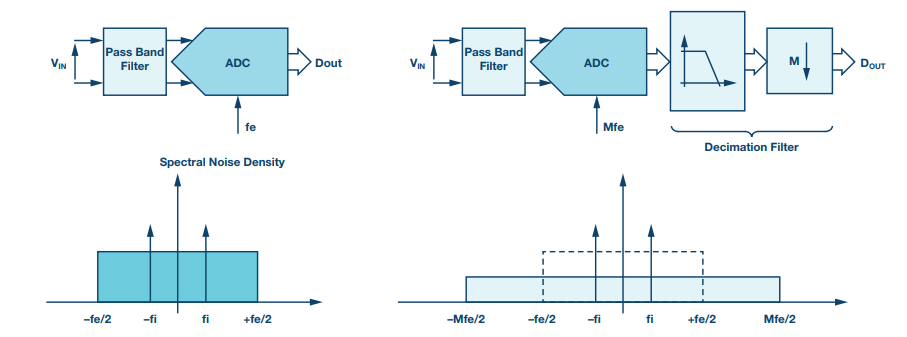

以高于奈奎斯特定理要求的最小值的FSE速率对信号进行采样,可以通过处理和增加编码器的信噪比来执行增益运算,并因此增加有效位的数量。实际上,量化噪声和热噪声被同化为白噪声,该噪声在整个奈奎斯特频带及以外均匀分布。过采样之后,通过滤波和严格以最小所需采样速率(或2×BW)限制有用频带,频带每降低一个倍频程,噪声能量将降低3dB,如图2所示。换句话说,过采样因子为4时最为理想,在理论上使信噪比增加了6dB;即是说,增加了一位,如等式1所示:

图3.过采样分布在-3dB条件下截止频率与阻带起点之间的过渡带

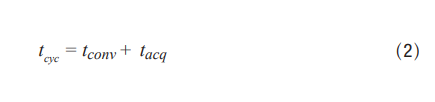

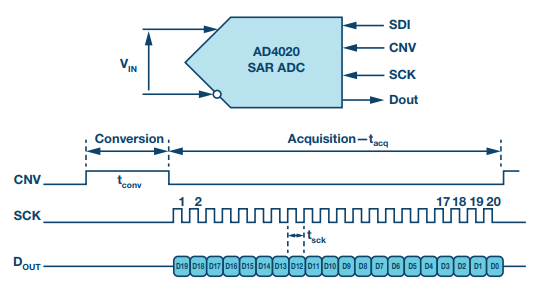

故定义最大采样频率,其构成为:

其本身由输出数据的读取速率调理,其中,

图4.AD4020的时序图

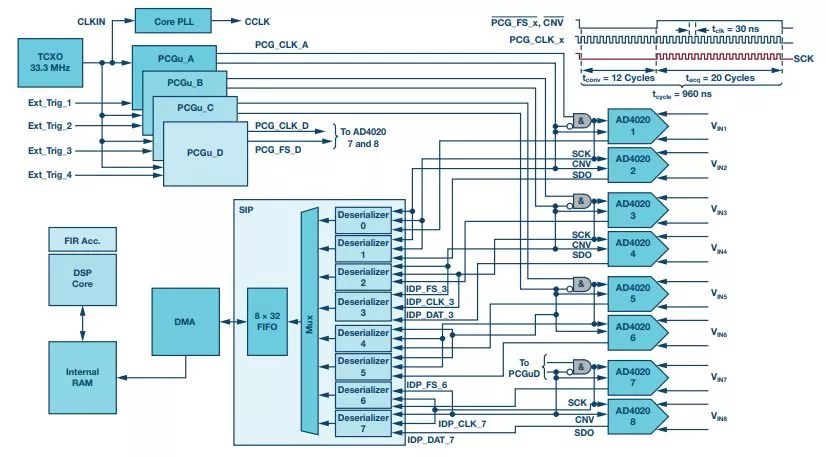

图5.通过解串行将8个20位1MSPSSAR ADC接入SHARC DSP;DMA数据传输进DSP内部RAM

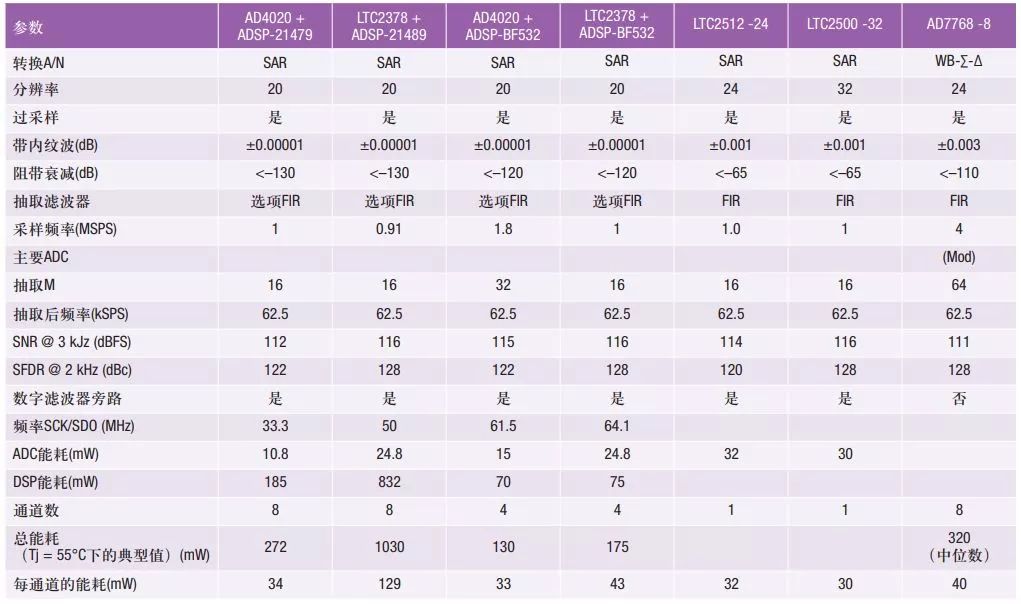

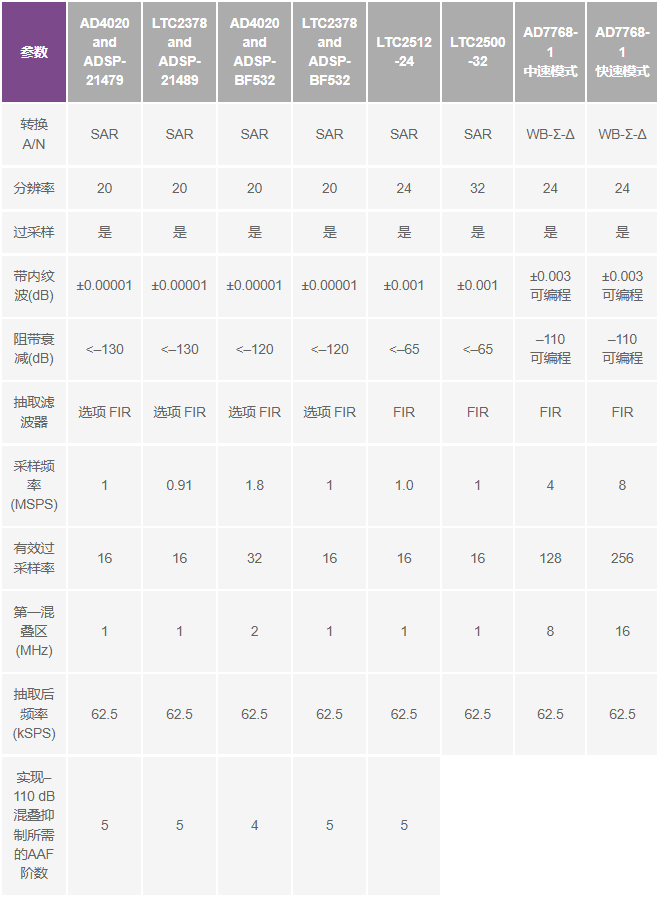

表1.不同SAR ADC与DSP相比的情况对比

抽取专用直接或优化FIR滤波器

级联多速率FIR滤波器(1/2频段)

多相FIR滤波器

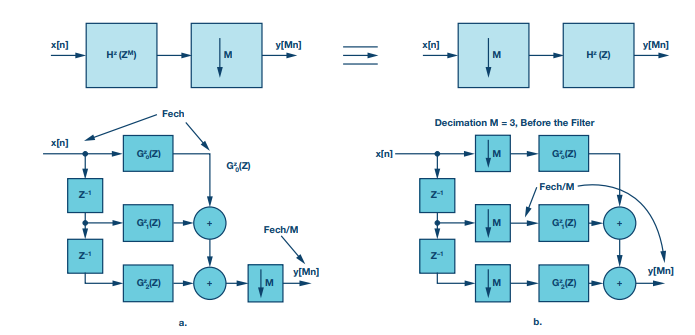

无论是FIR还是IIR类型的多相滤波器都是抽取或插值滤波器最有效的实现方案之一。然而,传统数字处理方案要求在抽取之前进行滤波。在此假设下,1/M抽取滤波器由低通滤波器和紧随其后的采样频率降级组成(图6a)。预先对信号滤波,避免频谱混叠,然后以M-1的速率定期消除样本。然而,常规FIR或其他结构针对这些抽取滤波器的直接实现方案存在资源浪费问题,因为被拒样本是几十甚至几百次累乘(MAC)的结果。使用分解成若干滤波器组的多相滤波器或是针对抽取进行优化的滤波器,可以基于某些特点(如图6b所示)形成高效的滤波器。

图6a和6b.常规抽取滤波器和采用多相方案的抽取滤波器

支持IEEE-754定点或浮点32位算术格式„

有四个并行运行的累乘单元„

支持单速率和多速率处理模式(抽取或插值)„

一次简单迭代可以处理最多32个FIR滤波器,总共多达1024个系数

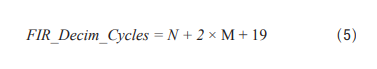

N为滤波器的系数的个数,M为抽取速率。

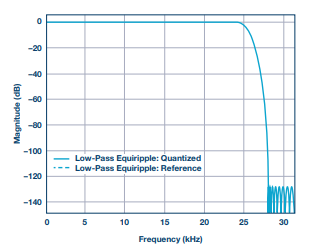

图7.抽取滤波器的滤波器响应

表1. 不同SAR ADC与DSP相比的情况对比

原文标题:高精度 SAR ADC的抗混叠滤波考虑因素

文章出处:【微信公众号:亚德诺半导体】欢迎添加关注!文章转载请注明出处。

-

亚德诺

+关注

关注

6文章

4681浏览量

16734

原文标题:高精度 SAR ADC的抗混叠滤波考虑因素

文章出处:【微信号:analog_devices,微信公众号:analog_devices】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

AD7678:18位高速高精度SAR ADC的卓越之选

高精度高速ADC:AD7665的技术剖析与应用指南

SAR ADC采样外围滤波电路配置电路计算原理

16位15Msps SAR ADC LTC2387-16:高速高精度的理想选择

高精度、低功耗20位差分SAR ADC——AD4020/AD4021/AD4022深度解析

AD4002/AD4006/AD4010:高精度SAR ADC的卓越之选

SGM51652H4/SGM51652H8 SAR ADC:高精度与灵活性兼备的模拟数字转换方案

SGM51613D/SGM51652D/SGM5162D:16位高精度SAR ADC的设计之道

泡沫起升仪模拟前端设计:微弱信号放大与抗混叠滤波电路

模数转换器(ADC)的最高使用频段取决于哪些因素

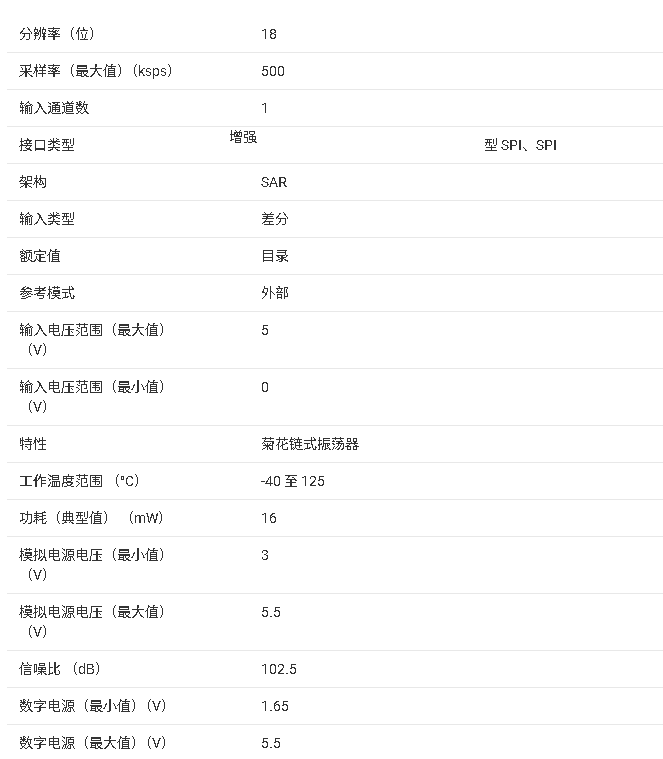

ADS891xB 系列 18 位高精度 SAR ADC 核心信息总结

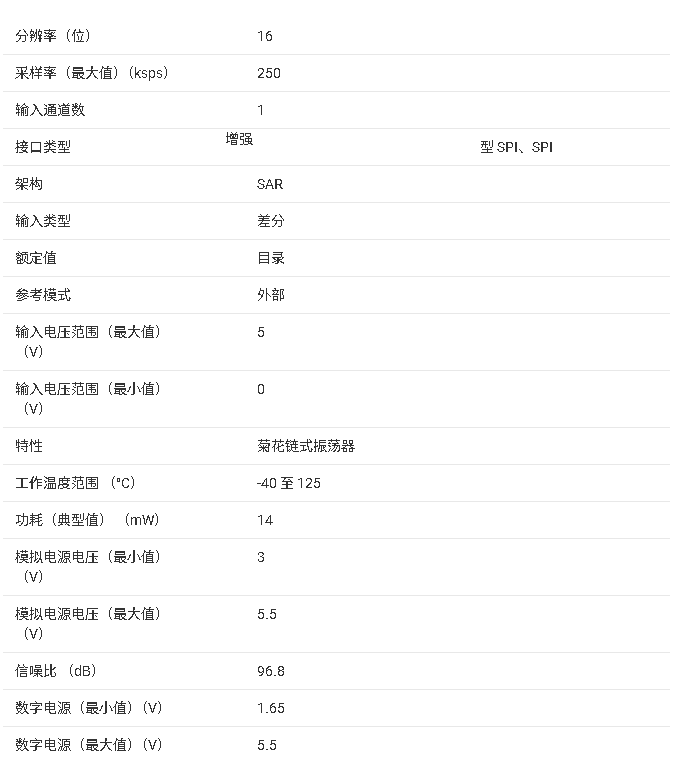

ADS892xB 系列 16 位高精度 SAR ADC 核心信息总结

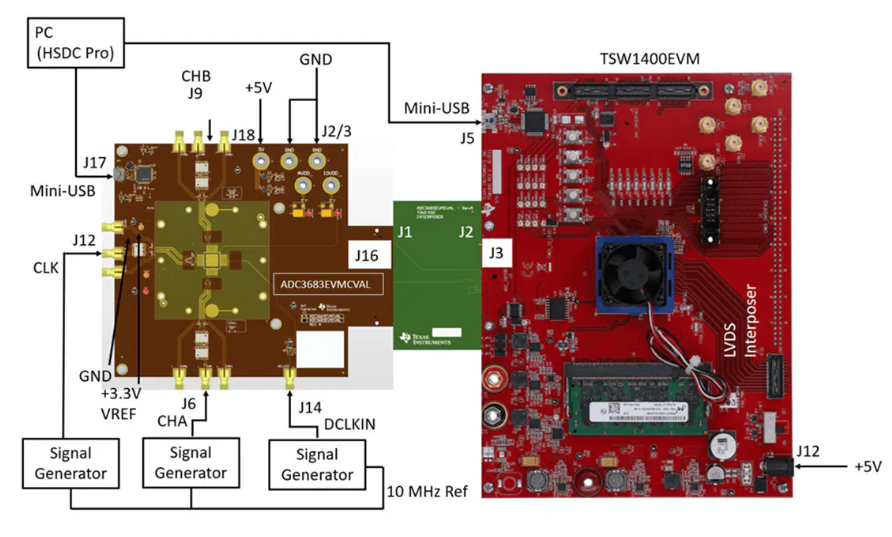

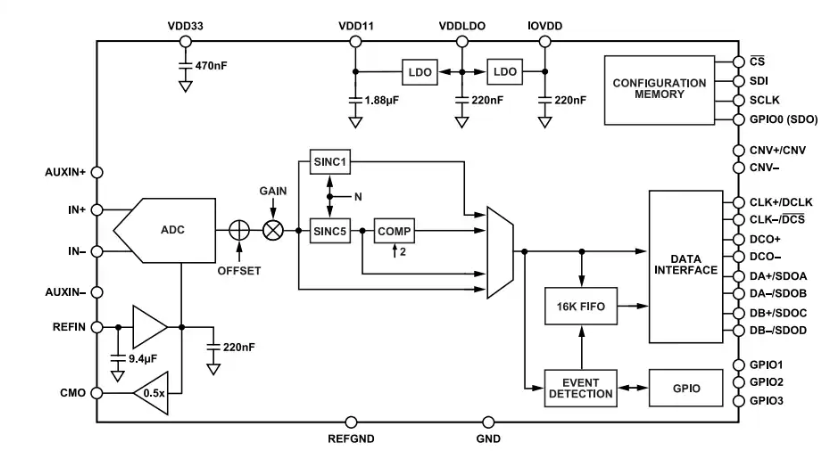

ADC3683EVMCVAL评估模块技术解析与应用指南

笙泉高精度24位ADC (MAD2402)新上市,赋能精准量测

Analog Devices Inc. AD4080差分SAR ADC数据手册

高精度 SAR ADC的抗混叠滤波考虑因素

高精度 SAR ADC的抗混叠滤波考虑因素

评论