FPGA中有专门的ROM IP Core,如果按照规范用Verilog编写的ROM文件可以被工具综合成RAM资源,而ASIC在需要后端去做专门Memory,前端仿真可以自己编写RAM/ROM/FIFO/RegFile IP。为了方便仿真这样写个ROM,方便初始化。

将设计电路参数化可重复使用,构建自己的代码库,搭建起你的数字积木。

将设计电路参数化可重复使用,构建自己的代码库,搭建起你的数字积木。

module single_port_rom(/*autoarg*/

Outputs

q,

Inputs

clk

);

parameter DATA_WIDTH = 8;

parameter ADDR_WIDTH = 8;

input [ADDR_WIDTH-1:0] addr;

input clk;

output reg [DATA_WIDTH-1:0] q;

reg [DATA_WIDTH-1:0] rom[2**ADDR_WIDTH-1:0];

initial begins

rom);

rom);

end

always @ (posedge clk)begin

q <= rom[addr];

end

endmodule

系统函数$readmemh和$readmemb分别用来读取十六进制文件和二进制文件。貌似没有读十进制的。txt中的数据每行一个不需要逗号和最后一个数据后面的分号,数据格式对应。更多使用可以查询IEEE的Verilog语法手册。例化方式和rom IP一样可参数化配置任意大小

single_port_rom

#(

.DATA_WIDTH(DATA_WIDTH),

.ADDR_WIDTH(ADDR_WIDTH)

)

u_sin(/*autoinst*/

// Outputs

.q (dout[DATA_WIDTH-1:0]),

// Inputs

.addr (addra[ADDR_WIDTH-1:0]),

.clk (clk));

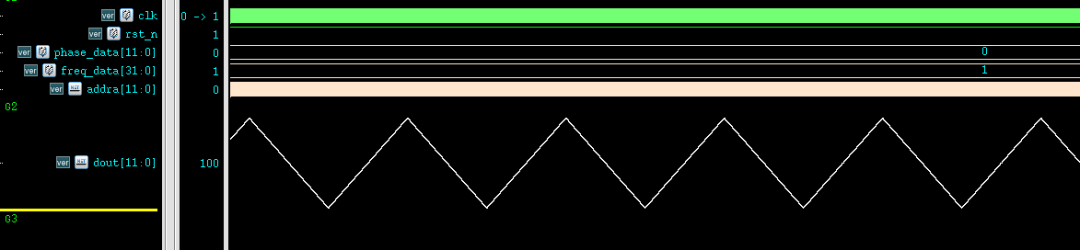

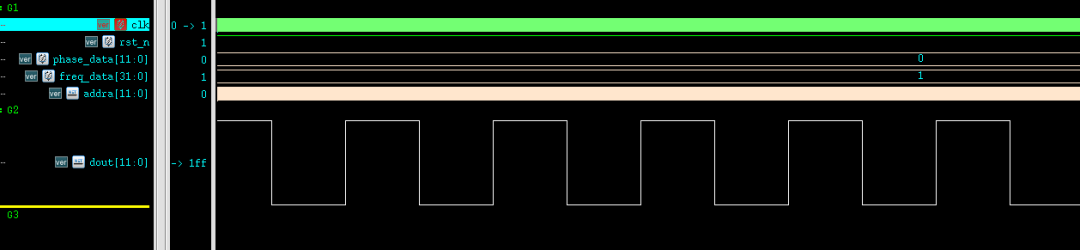

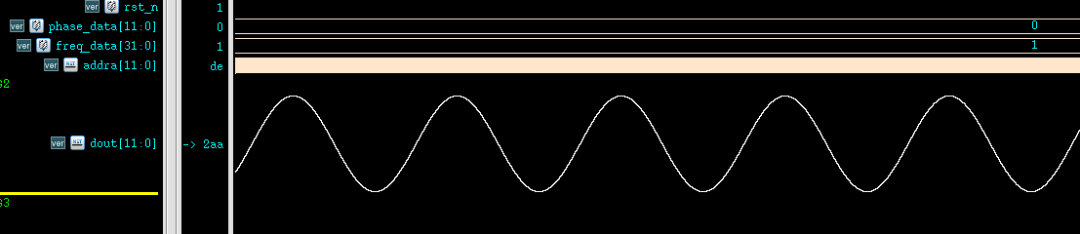

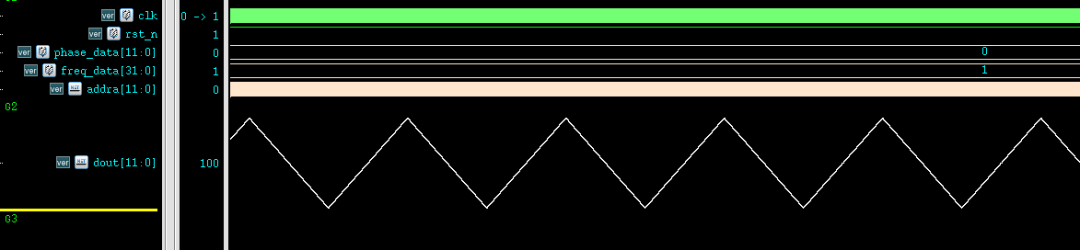

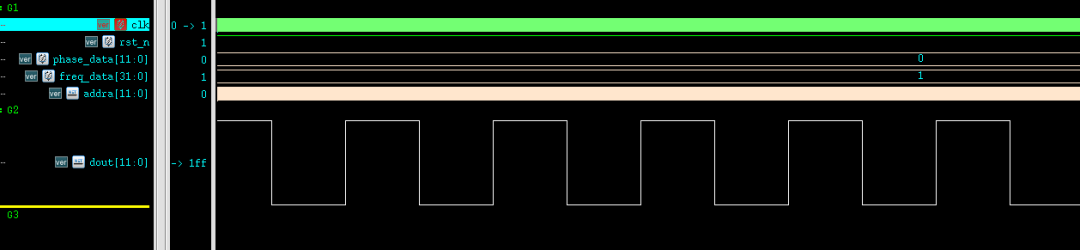

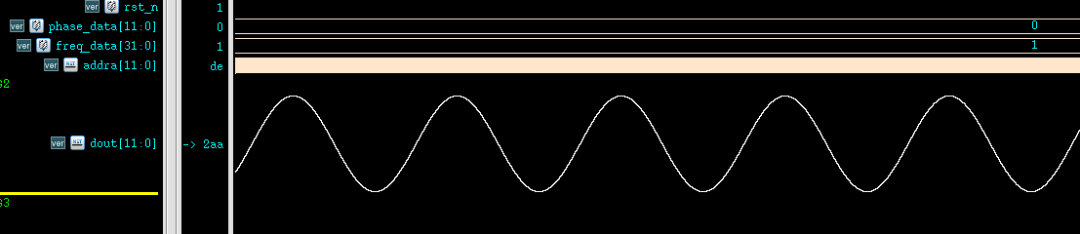

整了三个波形,仿真能跑起来。

将设计电路参数化可重复使用,构建自己的代码库,搭建起你的数字积木。

将设计电路参数化可重复使用,构建自己的代码库,搭建起你的数字积木。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

asic

+关注

关注

34文章

1277浏览量

124929 -

ROM

+关注

关注

4文章

579浏览量

89364 -

Verilog

+关注

关注

30文章

1374浏览量

114709

原文标题:为了方便仿真这样写个ROM

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

RW612 ROM 引导加载程序卡在 ISP 模式测试

Issue Description

I\'m experiencing a consistent issue with the NXP RW612 where the ROM bootloader

发表于 04-15 10:13

深度解析Z90255 ROM与Z90251 OTP电视控制器:功能、特性与应用

深度解析Z90255 ROM与Z90251 OTP电视控制器:功能、特性与应用 在电视控制领域,Z90255 ROM和Z90251 OTP这两款32 KB电视控制器凭借其丰富的功能和出色的性能,成为

Z86C02/E02/L02微控制器:高性价比的512字节ROM CMOS解决方案

Z86C02/E02/L02微控制器:高性价比的512字节ROM CMOS解决方案 在电子设计领域,寻找一款既经济实惠又功能强大的微控制器是许多工程师的追求。Zilog的Z86C02/E02/L02

Hummingbirdv2 E203 仿真排坑之路

在仿真时读入rom,判断功能是否正确。

3.1编译工具

编译需要用riscv的GNU工具,可以在[官网下载](https://nucleisys.com/download.php

发表于 10-31 09:22

Nucleistudio+Vivado协同仿真教程

内部ROM启动,故需要修改 .cfg 配置文件,位置如下?

双击打开后,将划线的flash启动部分注释掉

然后修改Build选项,使反汇编生成机器指令文件:右键工程,点击properties

在

发表于 10-23 06:22

RISCV指令二进制编码利用matlab生成E203仿真可用文件

鉴于nuclei studio IDE生成的.verilog难懂,为了方便对单条或者几条指令进行测试,我们队伍编写了matlab代码来实现E203仿真可以识别到的文件。

matlab代码如下

发表于 10-22 07:06

请问谁家串口屏屏幕支持在线仿真功能,这样我们做界面更加方便

发表于 10-13 09:06

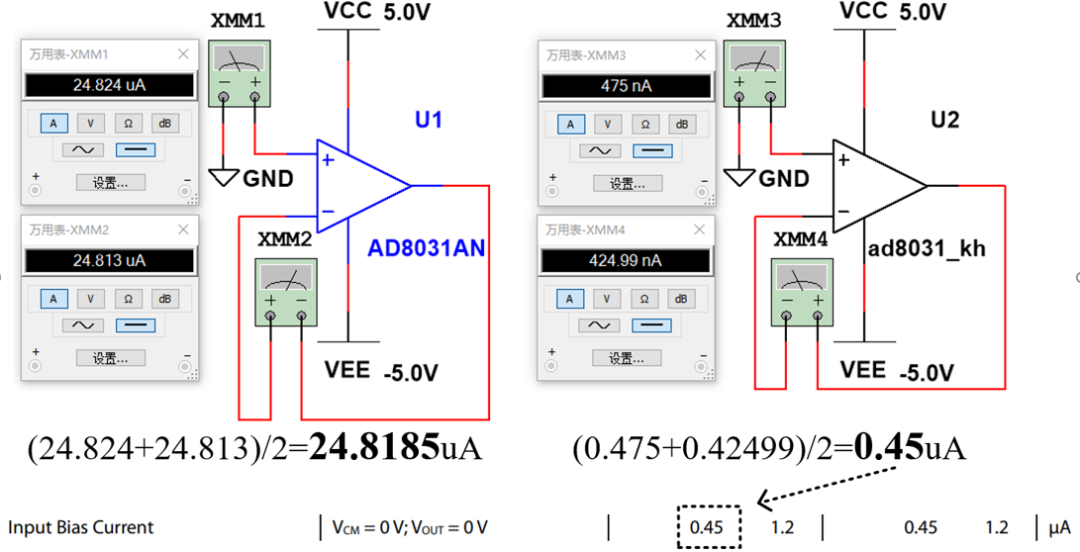

胡言乱语:Multisim仿真准不准?偏置电流错的离谱?

这是很多同学都会问到的一个问题,Multisim仿真究竟准不准?很多同学在仿真时发现Multisim仿真结果和手册的差距太大,然后说是Multisim这个软件不行,其实不是这样的,不管

【RK3568+PG2L50H开发板实验例程】FPGA部分 | ROM、RAM、FIFO 的使用

接口列表

该部分介绍每个顶层模块的接口。

ram_test_top.v

rom_test_top.v

fifo_test_top.v

3.代码仿真说明

本次的顶层模块实际就是例化 IP

发表于 07-10 10:37

Simcenter FLOEFD BCI-ROM和Package Creator模块

优势采用独立于边界条件的降阶模型(BCI-ROM)加速执行瞬态热仿真,同时采用PackageCreator轻松创建电子封装热模型。求解速度比完整的3D详细模型快40,000倍,且不折损精度有效保持

LMK03318如何使用TICS将程序烧录进ROM?

请问 LMK03318芯片如何用TICS PRO烧录进芯片内部ROM?并且上电时钟就工作,有输出(就是上电程序自启动),急!!!

发表于 07-07 14:35

Simcenter Flotherm BCI-ROM技术:与边界条件无关的降阶模型可加速电子热设计

BCI-ROM可生成为矩阵类型、用于电路仿真的电热模型(VHDL-AMS格式)、用于系统仿真(FMU格式)的模型,甚至用于3DCFD的嵌入式BCI-ROM从根据热瞬态测试数

求助,关于FX3 ROM引导加载程序系统重启问题求解

加载程序。

该问题是否与已知勘误表问题(FX3 自供电时,USB 启动模式下 USB 枚举失败)有关,因为 USB 端口/电路板在系统重置期间不会完全断电? 如果是这样,那么就没有办法解决这个问题,让 ROM 引导加载程序在系统重置后正确显示,而无需执行 FX3 重置,

发表于 05-13 06:06

《聊一聊ZXDoc》之CAN总线仿真、面板仿真

ZXDoc支持CAN总线仿真、面板仿真功能,通过虚拟化通信环境,提前验证、优化和保障系统可靠性,降低开发成本与风险,面板仿真还使其画面实物化,便于操作和理解,仿真功能已成为ECU研发和

为了方便仿真这样写个ROM

为了方便仿真这样写个ROM

评论