Cadence Allegro在PCB中手动或者自动添加差分对属性

设计PCB过程中,若设计中有差分对信号,则需要将是差分的2个信号设置为差分对,设置差分对有2种方式:手动添加及自动添加

一、手动添加差分对:

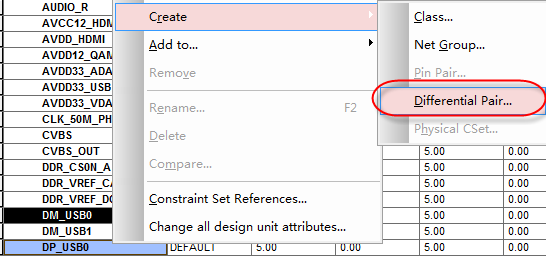

1、点击Setup-Constraints-Constraint Manager调出CM规则管理器,然后到Physical规则管理器下点击Net-All Layers,然后在右侧栏中选中2根需要设置为差分对的信号,按Ctrl键全选中后右击,选择Create-Differential Pair,如图1所示;

图1 创建差分对图示

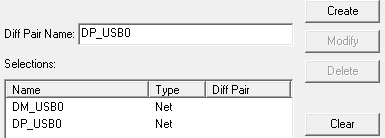

2、在弹出的对话框中设置好差分对的名称,点击Create,即可创建差分对规则,如图2所示;

图2 Create Differential Pair选项卡

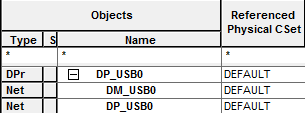

3、创建后即可在此管理器中生成差分对,如图3所示。

图3 手动创建的差分对图示

二、自动生成差分对:

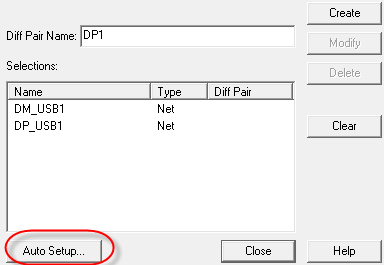

1、可以从上述步骤中的Create Differential Pair选项卡中点击Auto Setup选项,如图4所示;

图4Create Differential Pair选项卡

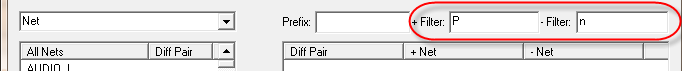

2、在弹出的对话框中,在Filter的2个对话框中输入差分对的后缀(一般是“+、-”或者“P、N”),如图5所示;

图5Differential Pair Automatic Setup选项卡

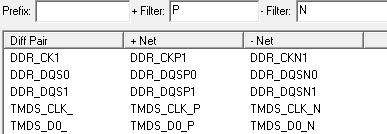

3、输入后,在Prefix的框中点击一下,软件会自动将识别出来的差分信号列在其下的方框内,如图6所示;

图6Differential Pair Automatic Setup选项卡

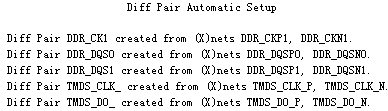

4、然后点击Create,即可自动将设计中的差分对自动创建好并且会生成Log结果列表,如图7所示。

图7Diff Pairs Automatic Setup Log File图示

声明: 本文凡亿教育原创文章,转载请注明来源!投稿/招聘/广告/课程合作/资源置换请加微信:13237418207 分享点赞在看“三连”支持!

点击“阅读原文”查看更多干货文章

分享点赞在看“三连”支持!

点击“阅读原文”查看更多干货文章

原文标题:Cadence Allegro在PCB中手动或者自动添加差分对属性

文章出处:【微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

-

pcb

+关注

关注

4420文章

24022浏览量

426967

原文标题:Cadence Allegro在PCB中手动或者自动添加差分对属性

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

12:如何把 PCB 上的铜皮扩大或缩小 I 芯巧Allegro PCB 设计小诀窍

11:如何在 Allegro 中添加自定义的测试点 I Allegro PCB 设计小诀窍

10.如何在Allegro中快速精准移动器件?| 芯巧Allegro PCB 设计小诀窍

08. 如何在 Allegro中设置禁止添加测试点区域?| 芯巧Allegro PCB 设计小诀窍

03. 如何把 PCB 板上的线变成铜皮?| 芯巧Allegro PCB 设计小诀窍

02. 如何在 Allegro 中快速自定义字体?| 芯巧Allegro PCB 设计小诀窍

01. 如何在 Allegro 中快速区别不同网络?| 芯巧Allegro PCB 设计小诀窍

技术资讯 I 在 Allegro PCB 中如何快速布局

技术资讯 I Allegro PCB 设计中布线优化

技术资讯 I Allegro设计中的过孔阵列设计

技术资讯 I 图文详解约束管理器-差分对规则约束

Allegro Skill布线功能-添加差分过孔禁布区

Cadence Allegro在PCB中手动或者自动添加差分对属性

Cadence Allegro在PCB中手动或者自动添加差分对属性

评论