越来越多的嵌入式和物联网设备需要更多的程序存储器,而不是使用嵌入式闪存或SRAM在片上经济地实现的存储器。对于这些设计,越来越多的设计正在转向就地执行(XiP)操作,其中代码直接从外部NOR闪存设备执行,通过这种方式可以实现其系统的可扩展性。

大多数设计人员通常会为其 XiP 系统选择四通道串行外设接口 (SPI) 存储器,因为它是成本最低的选择。但是,根据具体应用,设计人员在使用四通道器件时可能无法满足性能要求。

他们可以通过进行软件优化来解决这个问题,但这种更改通常需要软件团队花费数周甚至数月来优化设计,即使这样,优化仍然可能还不够。最终可能有必要从设计中消除特征。另一种选择是提高处理器的时钟速度以实现所需的性能,但这可能会提供递减的回报并增加系统能耗,并增加潜在的电池尺寸,从而降低成本。当然,一些设计已经让处理器以最大时钟速度运行,在这种情况下,可能需要升级到更快、更昂贵的处理器。

设计人员应考虑的一个选项是从四通道SPI器件转向八通道SPI器件进行设计。虽然此举不会对所有应用程序产生巨大影响,但有一些应用程序将受益匪浅。在那些对闪存性能敏感的应用中可以看到这种优势。

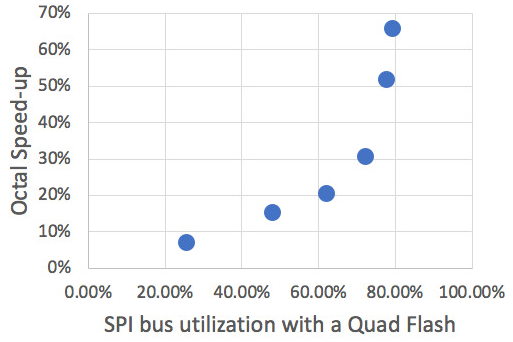

预测这一点的简单方法是查看SPI总线上的流量。如果应用程序大部分都在缓存中运行,则不会在总线上看到大量事务。当您开始看到总线的大量流量/高利用率时,您就会知道它更依赖于闪存。如果总线利用率很高,切换到像Adesto的EcoXiP这样的八通道器件的收益是相当可观的。最终,这可以转化为显着的能源和成本节约。

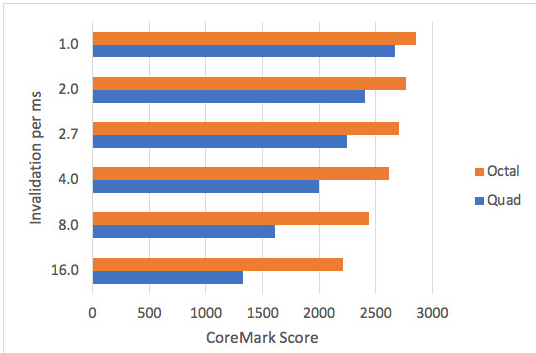

我们 使用 逻辑 分析 器 来 测量 四 通道 模式 的 SPI 总 线 利用率, 以 观察 在 切换 到 八 通道 器件 时 其 与 系统 加速 的 关联 关系。我们运行了 CoreMark 基准测试,通过以固定间隔清除缓存的内容(缓存失效),在总线上生成更多/更少的流量。这些缓存失效旨在模拟任务切换和中断频繁的实时系统场景。通过使间隔越来越短,我们增加了公共汽车上的交通量。

您可以看到,在某些领域,四元和八进制性能之间的差异并不大,但随后它会向上摆动。在这一点上,值得考虑转向八进制设备。当应用程序演示SPI总线利用率达到60%或更高时,您可以看到其优势。

在许多系统中,功率是一个重要的考虑因素。我们希望确保使用八进制器件可以获得的额外性能不会与更高的系统级功耗相权衡。我们使用相同的设置来测量恩智浦 i.MX RT1050 MCU在就地扩展模式下运行时的功耗。我们使用相同的技术,以固定的时间间隔注入缓存失效,并测量MCU和闪存的功率。下图显示,在我们测试的所有场景中,Octal EcoXiP 比传统的 Quad 设备更节能。EcoXiP 在每种情况下都提供了更多的每 mW 核心标记。同样有趣的是,EcoXiP 的功耗优势随着工作负载的加剧而增加,工作负载的缓存未命中次数更多,从而在 SPI 总线上产生更多流量。

如果您使用的是恩智浦 i.MX RT1050这样的器件,您可以轻松地将Quad器件换成八进制器件,因为该芯片的架构巧妙,可以同时支持两者。

审核编辑:郭婷

-

嵌入式

+关注

关注

5187文章

20170浏览量

329195 -

存储器

+关注

关注

39文章

7715浏览量

170916 -

物联网

+关注

关注

2939文章

47357浏览量

408570

发布评论请先 登录

UPS主机:企业信息系统的“电力心脏”,您选对了吗?

认识UPS设备电源:您设备的“电力保险”

Linux系统性能优化技巧

罗德与施瓦茨TCO模型帮您降低测试设备成本

服务专栏| 台风天特辑——您的三坐标测量机,我们与您共同守护

KaihongOS桌面版成功适配x86设备,邀您抢先体验!

升降速曲线对直线电机系统性能影响的研究

路侧设备RSU的电源不稳定是否困扰您?凌科工业连接器带来全新解决方案

HarmonyOS NEXT 原生应用/元服务-DevEco Profiler性能优化过程

探索 RK3576 方案:卓越性能与灵活框架,诚邀开发定制合作!

集创北方邀您相约2025年欧洲视听设备与信息系统集成技术展览会

使用NAGIOS XI增强您的IT基础设施

专为满足您的特定测试需求量身打造的系统:构建您的SG EVO以实现无与伦比的射频精度

您的四路设备是否可以满足您的系统性能

您的四路设备是否可以满足您的系统性能

评论