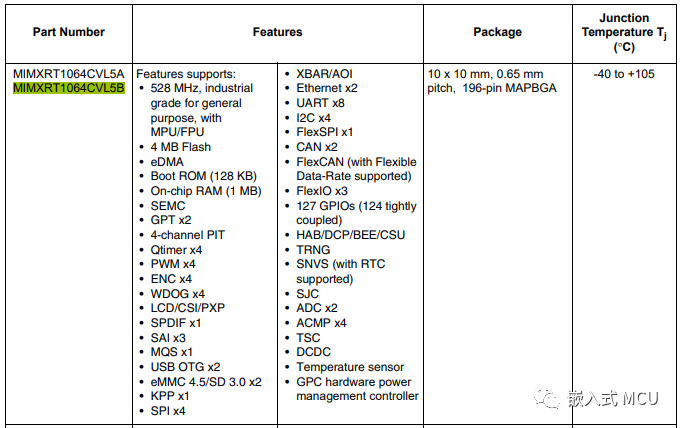

NXP MIMXRT1064CVL5B 能否支持使用SPI接口的HyperRAM?使用HyperRam的原因是为LCD存储帧或者USB记录数据或者以太网采集通信数据都需要缓冲区。使用NXP MIMXRT1062DVL6B MCU,SDRAM使用并行接口会占用很多GPIO引脚,把所有二进制软件从非易失性Nand闪存复制到SDRAM,大多数SDRAM资源将用于运行应用代码,最大速度为166Mhz,如果在SDRAM上添加帧或者数据缓冲区,速度会很慢。MCU上还可用的接口是使用HyperRam。在MIMXRT1064CVL5B的参考手册中,FlexSPI 模块支持HyperBus 器件(HyperFlash / HyperRAM)。可以使用 I.MX Pins配置工具进行管脚和时钟配置。

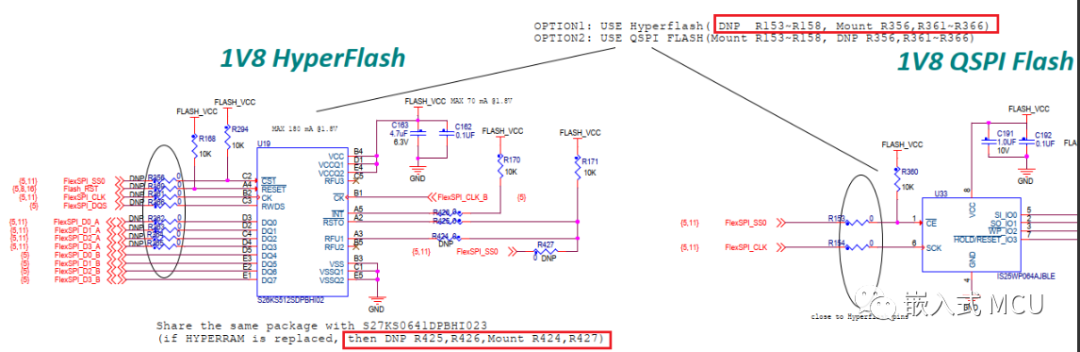

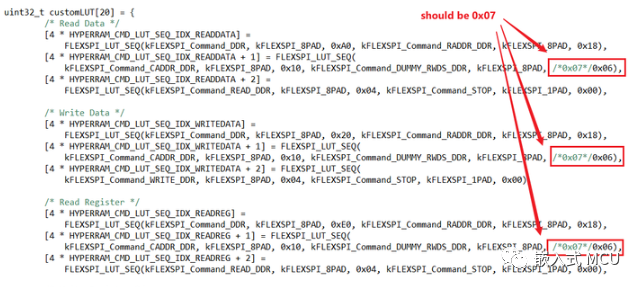

使用S27KL0642DP为3.0V HyperRAM,不适用于1V8 HyperFlash,RT1060-EVK开发板中的默认FLASH_VCC为1V8,如果要使用S27KL0642DP,则应将FLASH_VC更改为3V。或者将HyperRAM更改为S27KS0642DP。S27KL0642DP的冗余时钟数为7。

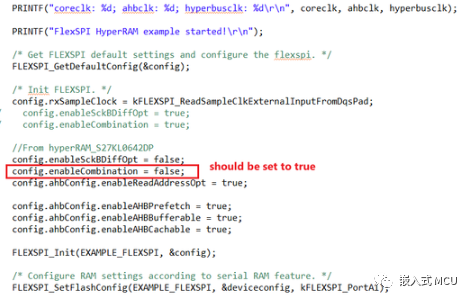

需要启用 combination。

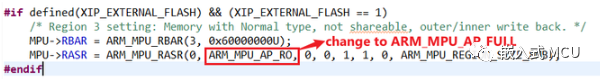

另外的 MPU 配置,设置存储器 0x60000000 为 ARM_MPU_AP_FULL,如下图所示。

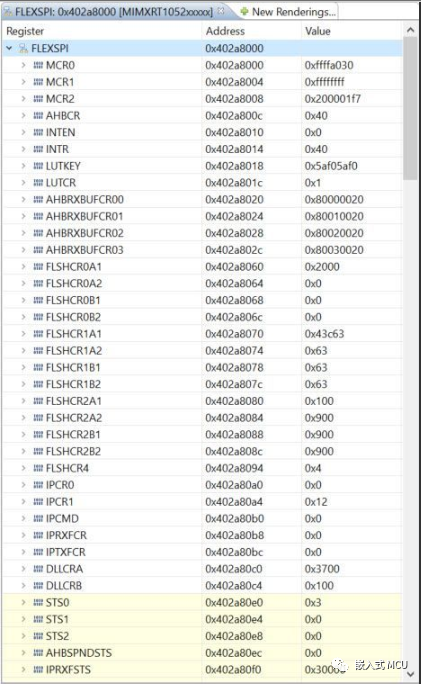

可以从调试器中获取 FlexSPI寄存器的状态。

不管应用程序如何使用内存,都能够在HyperRAM中启用不可缓存区域。虽然在HyperRAM中配置不可缓存内存没有问题,禁用缓存的外部内存性能将大大降低。需要仔细考虑如何在应用程序中使用它。例如,与USB或网口一起使用。在MCU中的多个主机之间共享RAM确实需要一个不可缓存区域,因为缓存仅由内核使用。因此,USB端点缓冲区或由内核以外的主机更新的任何RAM都应该是不可缓存的。理想情况下,内部OCRAM将用于这些共享RAM,因为它比外部存储器的性能高得多。特别是对于高速USB或任何需要RAM高性能的主机,使用较慢的外部RAM可能会导致一些带宽/延迟问题。通常,这些与其他主机共享的RAM较小,非常适合放置在内部OCRAM中。

此外,由于堆栈一直在使用,并且经常是非线性访问,因此存储在非缓存的外部内存中可能会对应用程序的性能产生影响。堆栈仅由内核主机使用。理想情况下,堆栈将放置在DTCM中。或者,如果它们不适合DTCM,那么使用缓存的OCRAM或外部内存将优化性能。

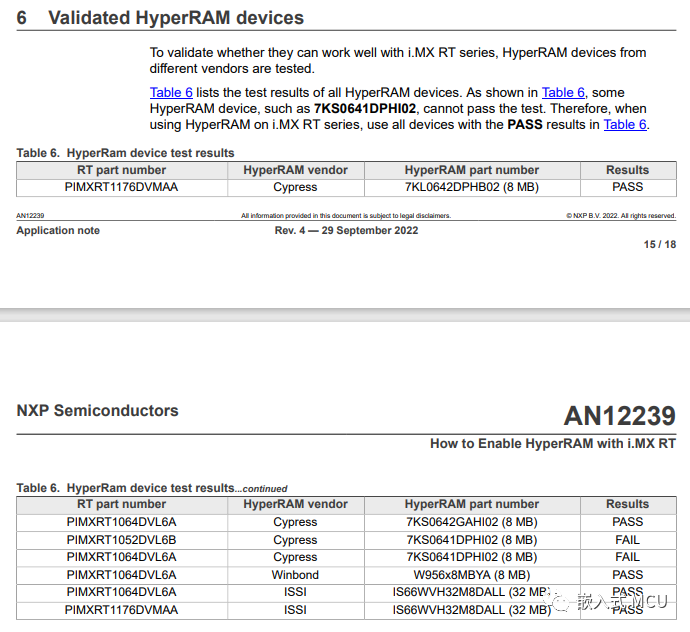

在AN12239里面提到了测试验证过的 HyperRAM列表。

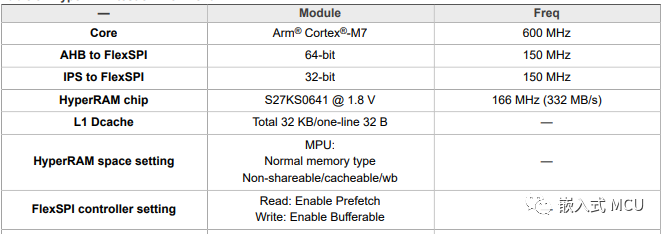

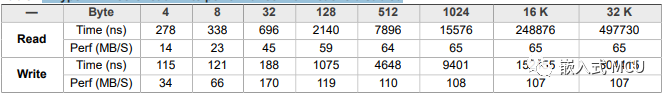

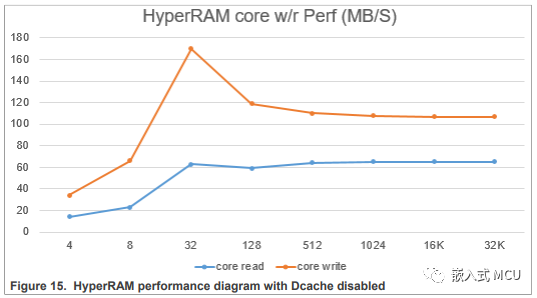

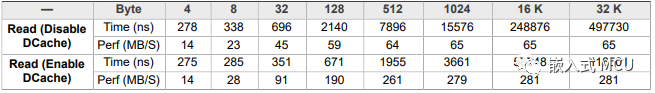

实际测试,当Cached禁止的时候,HyperRAM写测试比读操作性能更高。HyperRAM 读/写性能(Dcache禁止)

一些配置可能会影响HyperRAM性能:

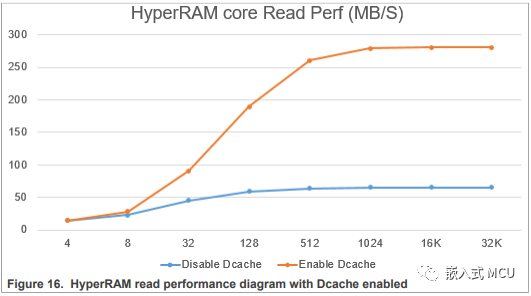

缓存影响——RT1060支持最大32K DCACHE和32K ICACHE,启用缓存后可以进一步提高性能。

预取缓冲区影响——RT1060支持1024KB的预取缓冲区,其策略如下:

可为指定的主控或多个主控配置共享同一缓冲区。自动将数据预取到缓冲区,直到缓冲区已满。检查是否命中预取地址范围,如果超出范围,则从FlexSPI 器件触发新的读取操作,否则,如果它已经在预取缓冲区中,则从AHB缓冲区读取,如果没有,则等待预取数据到缓冲区。

因此,需根据应用做不同的配置。如果每次数据访问都很小,并且访问地址不连续,建议设置较小的预取缓冲区大小。如果是连续地址访问,建议设置大的预取缓冲区大小。从HyperRAM测试性能来看,有以下建议:启用Cache缓存以进一步提高HyperRAM性能。

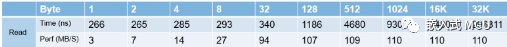

如下是 SDRAM(使能 Cache)测试数据:

如下是 Hyper RAM(使能Cache)测试数据:

HyperRAM性能与SDRAM相比,SDRAM读取吞吐量(ARM内核读取)比HyperRAM慢。HyperRAM MPU配置:( non-shareable,Cacheable,Write back,使能 Dcache)。另外从内存性能来看,SDRAM/Hyper RAM/HyperFlash/Octal Flash几乎具有类似的性能,需要平衡ARM内核和DMA访问超RAM 时隙,可以更改NIC-301SIM-M7寄存器以设置ARM内核和DMA访问优先级。

-

mcu

+关注

关注

147文章

19129浏览量

403993 -

NXP

+关注

关注

61文章

1410浏览量

199244 -

HyperRAM

+关注

关注

0文章

5浏览量

1819

原文标题:MIMXRT1064CVL5B 连接 HyperRAM

文章出处:【微信号:嵌入式 MCU,微信公众号:嵌入式 MCU】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

NXP品牌MCU系列最新优势到货型号:LPC4320FBD144,MCIMX6Y2CVM08AB,MIMXRT1051CVL5B等型号

如何搭建NXP MIMXRT1052CVL5B + 正点原子 + MCUXpresso IDE的开发环境?

MIMXRT1061CVL5B在断电然后上电后,微控制器无法启动的原因?

可以使用MIMXRT1062CVJ5A为基于MIMXRT1062CVJ5B的开发板构建SDK吗?

如何下载MIMXRT1051CVL5B的IAR IDE SDK?

PIMXRT1064DVL6A的MIMXRT1064-EVK板温度怎么可能比环境温度低这么多?

如何为 i.MIMXRT1064 EVK启用ETM(嵌入式跟踪宏单元)功能?

如何在MIMXRT1064评估套件上部署tflite模型?

如何使用MCUXpresso安全配置工具通过UART闪存MIMXRT1064?

将非缓存数据放在HyperRAM中有什么问题吗?

MIMXRT1051CVL5B MCU不唤醒的原因?

MIMXRT1051CVL5B VDD_USB_CAP 引脚浮动,是否有任何东西可能损坏或无法正常工作吗 ?

NXP MIMXRT1052CVL5B + 正点原子 + MCUXpresso IDE 开发环境搭建

MIMXRT1064CVL5B连接HyperRAM

MIMXRT1064CVL5B连接HyperRAM

评论