1 JTAG 标准中的描述

最新JTAG标准:IEEE_std_1149.1-2001

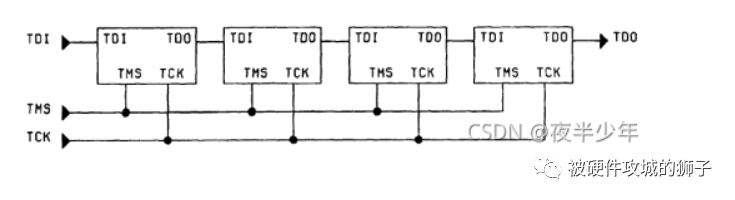

图1 JTAG原理

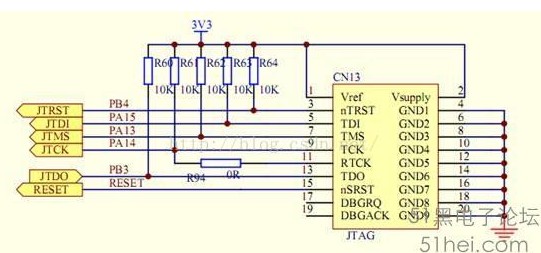

1.1 TMS

TMS是启动使能信号(标准PAGE-11),上拉:

1.2 TCK

TCK是时钟信号(标准PAGE-9)上升沿或下降沿有效,可以上拉也可下拉,根据具体的器件要求选择:

1.3 TDI

TDI是数据输入(标准PAGE-11),上拉:

1.4 TDO

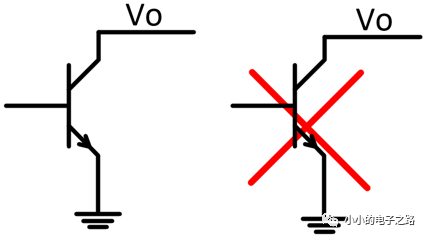

TDO是数据输出(标准PAGE-12),三态输出,可以和TDI做级联,上拉或浮空:

1.5 TRST

TRST 是复位信号(标准PAGE-13),低电平为复位状态,上拉:

3 总结(具体根据数据手册来确定)

上下拉电路一般在IC内部就已经做好,外部可以不加,如果外部添加,要与IC手册中的上下拉特性一致,TCK和TRST引脚有可能会不同,TDI和TMS都是上拉。TDO在IC内部都是浮空,由于TDO都是连接TDI,因此可以加上拉与TDI一致。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

JTAG

+关注

关注

6文章

415浏览量

75281 -

信号

+关注

关注

12文章

2931浏览量

80410

原文标题:JTAG信号的上下拉

文章出处:【微信号:被硬件攻城的狮子,微信公众号:被硬件攻城的狮子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

电阻上下拉功能实现原理详解

作为电路中最常见的电子元器件之一,电阻可以实现限流、隔离、上下拉等不同功能。以上拉为例,IIC通信接口SDA和SCLK都需要通过电阻实现上拉输入/输出。那么,电阻是如何实现上下拉功能的呢?

关于上下拉电阻大小讨论的计算

上下拉电阻大小计算,一直很困惑,这些大小计算来路,还恳请各位帮忙引导~~决定因子有那些.值得大家深入,问过公司好多同事,都说不出所以然.网友1:上拉或下拉取值一般选常用容易找到的阻值基本上就可以了

发表于 10-19 18:06

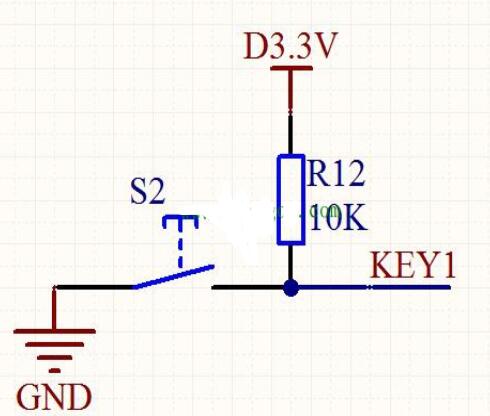

GPIO上下拉电阻的设置步骤

下拉电阻。上拉就是将不确定的信号通过一个电阻钳位在高电平,电阻同时起限流作用。下拉同理。也是将不确定的信号通过一个电阻钳位在低电平。不过从程序设计的角度讲,上拉就是如果没有输入

发表于 05-21 06:21

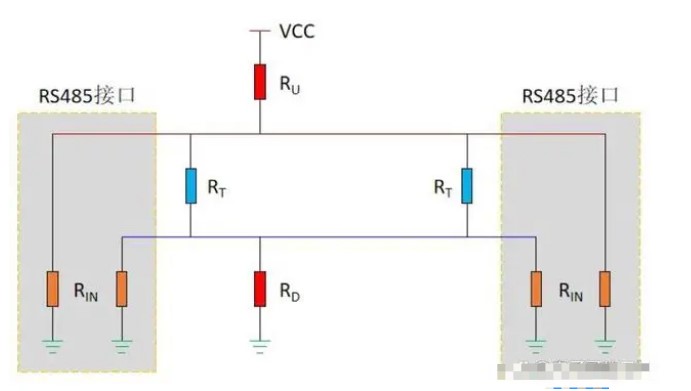

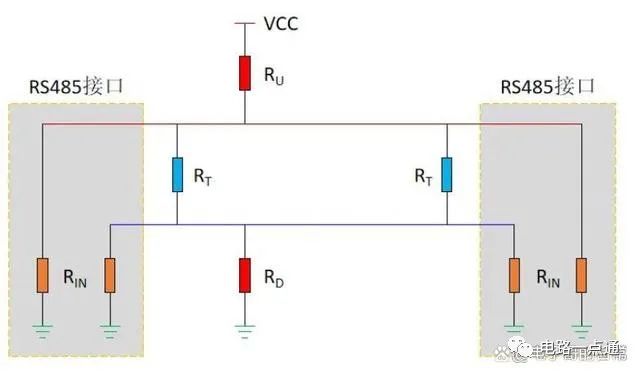

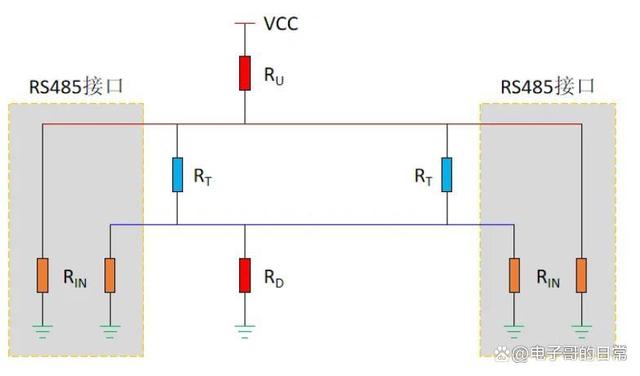

如何选择RS-485上下拉电阻?

。二、什么情况下需要加上下拉电阻?当遇到信号反射问题时,通常会通过增加匹配电阻来避免信号反射,以1对1通信为例,如图1所示。由于485总线通常使用特性阻抗为120Ω的双绞线,因此在485总线的首尾两端增加120Ω终端电阻来避免

发表于 05-21 07:10

什么是上下拉电阻?如何辨别呢

一、什么是上下拉电阻?上拉、下拉电阻统一称为拉电阻,作用是将状态不确定的信号线通过一个电阻将其箝位至高电平(上拉)或低电平(下拉)这里有人可能会疑惑?什么叫状态不确定的

发表于 01-14 08:58

单片机外部接上下拉电阻的好处是什么

1.不要太相信STM32内部的IO上下拉,必要的话,在外部接上下拉电阻。 2.当把JTAG的IO口当成普通IO口来使用时,要先禁止JTAG。 即:要使用到PB3、PB4、PA13、PA

发表于 11-02 16:27

•5184次阅读

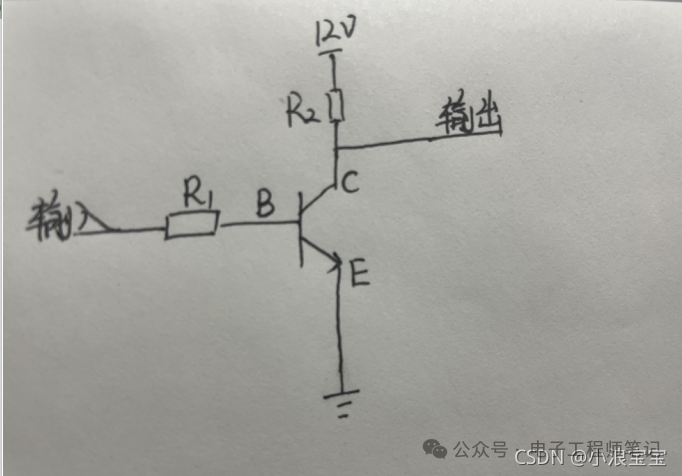

上下拉电阻在电路设计中的应用

“上下拉电阻应用很简单吗?”那可不一定。电路设计中,在哪些地方要加上下拉电阻?上下拉电阻加多大呢?是否要考虑它的功耗,以及它的灌电流大小,太大会损坏电子器件。一般情况下,元器件需要上下拉

电路设计:上下拉电阻应用很简单吗?

“上下拉电阻应用很简单吗?”那可不一定。电路设计中,在哪些地方要加上下拉电阻?上下拉电阻加多大呢?是否要考虑它的功耗,以及它的灌电流大小,太大会损坏电子器件。一般情况下,元器件需要上下拉

电阻是如何实现上下拉功能的呢?

电阻是如何实现上下拉功能的呢? 上下拉功能是指在电路中通过连接电阻来实现对信号的上拉和下拉控制。在数字电路中,上拉和下拉功能通常用于控制输入

JTAG信号的上下拉

JTAG信号的上下拉

评论