随着现代现场可编程门阵列 (FPGA) 片上系统 (SoC) 器件中可用的内容和 IP 选项的大量增加,灵活性的最后一个真正前沿是配置过程本身。期待看到下一代FPGA SoC,使这种灵活性在安全性、配置时间和单事件翻转(SEU)响应方面成为现实。

更强大的 FPGA 意味着更复杂的配置

FPGA 公司的产品每年都变得越来越复杂,包括各种强化 IP、处理器和数字加速功能。这些新产品有望在较少数量的微电路中提高功能集成度。但是,这种集成也意味着复杂的SoC配置。

许多其他 SoC 和专用标准部件 (ASSP) 产品已转向专用微处理器进行启动和配置管理。更重要的是,军方和其他具有安全意识的客户已经使用外部微处理器解决方案来管理FPGA和其他微电子器件的配置,以验证配置,检查签名,并确保配置过程中的“稳定状态”。

当今

如何完成配置 如今,FPGA 的配置过程主要由复杂的状态机(在 Altera 设备中称为“控制逻辑”)执行。比特流信息以串行方式加载到FPGA中,根据所选器件和用户选项进行可变解压缩、解密和身份验证;然后,在释放到操作模式之前配置整个设备。冒着过度简化少数公司技术的风险,配置过程大多是固定的,这意味着一个FPGA配置过程中的安全漏洞将成为所有其他设备的漏洞。

解决方案:添加专用微处理器进行配置

随着 SoC FPGA 产品的加入,设计人员可以继续获得固定的引导顺序,或者在选择器件的引导顺序时至少具有第一级的灵活性(FPGA 优先或 ARM 处理器优先)。

然而,FPGA 器件内置的专用微处理器带来了真正的配置灵活性,该微处理器可管理所有配置决策、配置文件的解密和身份验证、部分配置、对 SEU 的响应以及设备上的所有安全监视器。如果配置脚本或配置处理器的处理器指令本身可以加载到设备上并在现场更新,这将提供一组强大的工具,使设计人员能够探索安全性和配置时间之间的权衡空间。

自定义启动顺序

Arria 10 SoC 提供 FPGA 和 SoC 器件之间的启动顺序选择。但是,完全脚本化的配置过程将能够优先考虑FPGA或SoC中的部分设计,使用通过协议进行的配置以及当今FPGA可用的各种快速与高效方法。因此,配置过程和订单可以在非常精细的级别上进行管理,并可以根据设计进行定制。通过将 FPGA 结构划分为逻辑配置区域或扇区,这种设置变得更加灵活。

使用针对用户应用程序定制的脚本化配置可以限制跨设计配置漏洞的通用性。这意味着对一个设计的攻击不再必然适用于使用相同FPGA/SoC的所有设计。

在硬解密和身份验证加速器的帮助下,高度脚本化的配置过程可以决定是保护不保护、部分用户设计还是全部用户设计。在设计和逻辑重用的时代,并非设计的每个部分都需要保护或认证。但是,这是一个可以作为用户设计的一部分做出的决定,以便以安全性换取配置时间。

保护和验证配置数据的设计权衡是配置时间。即使使用快速结构和高速解密加速器,也存在与安全性(解密和身份验证)相关的配置时间影响。通过启用细粒度级别的安全性,用户设计将能够利用安全性和配置时间之间的全方位权衡。

对环境监测器和单个事件干扰

的响应 配置的最后一个重要元素是如何在发生辐射事件时恢复数据和设备操作,以及如何在FPGA SoC受到攻击时消除敏感的配置信息。

用于配置的专用处理器还可以提供对 SEU 事件的脚本和条件响应。这些可能包括重新配置整个设备或设计的一部分、将操作故障转移到设备的另一部分,或安全响应,例如擦除密钥和敏感数据。同样,专用配置处理器可以生成对环境监测器(如温度和电压)的高度脚本化响应,并通过FPGA SoC中密钥和配置数据的有序、受控和验证归零来做出响应。在大型设计中,数据归零的顺序可能很重要。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

20149浏览量

247186 -

FPGA

+关注

关注

1655文章

22287浏览量

630311 -

soc

+关注

关注

38文章

4514浏览量

227631

发布评论请先 登录

【VPX650 】青翼凌云科技基于 VPX 系统架构的 VU13P FPGA+ZYNQ SOC 超宽带信号处理平台

德州仪器AM68x Jacinto 8处理器技术解析

适用于Versal的AMD Vivado 加快FPGA开发完成Versal自适应SoC设计

面向四核应用处理器的PMIC DA9063-A数据手册

海光处理器有哪些型号

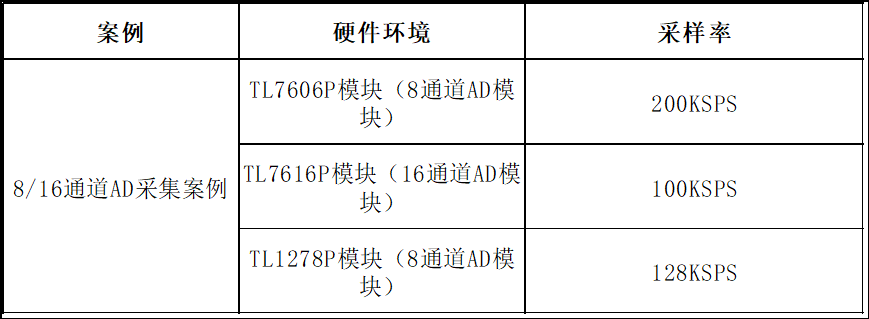

16通道AD采集方案,基于复旦微ARM + FPGA国产SoC处理器平台

EE-311:面向Blackfin处理器的VisualDSP闪存编程器API

EE-257:面向Blackfin处理器的引导压缩/解压缩算法

EE-367:面向ADSP-BF51xF16 Blackfin处理器的闪存编程器驱动程序

EE-306:PGO linker-面向Blackfin处理器的代码布局工具

面向FPGA-SoC的处理器驱动配置的安全价值

面向FPGA-SoC的处理器驱动配置的安全价值

评论