IAR Embedded Workbench for RISC-V 为 SiFive 最近推出的汽车 E6-A 和 S7-A 产品提供全面支持。

瑞典乌普萨拉 - 2022 年 10 月- 嵌入式开发软件和服务的全球领导者 IAR Systems 持续为 SiFive 的 RISC-V 车用 CPU IP 提供解决方案:IAR Systems 旗下的 IAR Embedded Workbench for RISC-V 支持最新的 SiFive 车用 E6-A 和 S7-A 产品系列,以满足信息娱乐、连接和 ADAS 等汽车应用的需求。IAR 的完整开发工具链帮助 OEM 和供应商的嵌入式软件开发人员充分利用 RISC-V 提供的能效、简单性、安全性和灵活性。

由于 RISC-V 在所有产品中使用单一的指令集架构 (ISA),因此提高了代码的可移植性,同时也能大幅降低汽车应用的成本并缩短上市时间。SiFive 车用处理器系列具有高度的灵活性,并提供多种选择,针对不同的完整性等级(如 ASIL B、ASIL D 或混合关键型)可进行面积和性能优化,满足 ISO26262 功能安全标准要求。其最近发布的 E6-A 系列针对各种实时的 32 位应用研发,覆盖系统控制、硬件安全模块 (HSM) 和安全岛,当然也包括独立的微控制器。而全新的 S7-A 是一颗 64 位的高性能实时内核,非常适合满足有高性能安全岛的现代 SoC 的需求,既能提供低延迟的中断支持,又可实现与主应用 CPU 一样的 64 位内存空间可见性。

IAR Embedded Workbench for RISC-V 是一个完整的开发工具链,内含强大的 IAR C/C++ 编译器和一个全面的调试器。利用工具全面的功能安全特性,客户可以为汽车应用生成具有最佳性能和功能安全性的代码并最大限度地减小代码规模。IAR Embedded Workbench for RISC-V 的功能安全版已通过 TÜV SÜD 的认证,符合10个功能安全标准要求,包括 ISO 26262 和 IEC 61508 等。为了确保汽车应用的代码质量,客户还可以利用无缝集成的 C-STAT 工具进行静态代码分析,确保代码符合 MISRA C:2012、MISRA C++:2008 和 MISRA C:2004 等工业标准。

SiFive 首席执行官兼董事长 Patrick Little 表示:“RISC-V 是一种现代指令集架构,围绕它诞生的生态系统正在快速增长,为汽车制造商和供应商带来了许多能效优势。SiFive 在市场唯一的端到端长期 RISC-V 路线图中结合了这些优点,旨在满足当前和未来的汽车需求。选择与 IAR Systems 合作,使得我们的生态系统如虎添翼,也进一步推动了 RISC-V 技术在汽车行业的应用。”

IAR Systems 首席技术官 Anders Holmberg 说道:“IAR Systems 是 RISC-V 社区的积极成员,因此我们能够与 SiFive 紧密合作,为其最新的 CPU IP 提供支持。汽车行业的客户可以充分利用我们的专业工具进行开发,加速产品开发过程,以实现更快的上市时间。”

IAR Embedded Workbench for RISC-V 的用户在许可证有效期内可享受 IAR Systems 提供的支持服务、验证服务包以及对已知漏洞和问题的定期报告。此外,IAR Systems 还在国内设立了直销团队,为客户提供快速、专业、本地化的技术支持服务。

-

cpu

+关注

关注

68文章

11326浏览量

225836 -

IAR

+关注

关注

5文章

414浏览量

38664 -

嵌入式软件

+关注

关注

4文章

251浏览量

28151 -

sifive

+关注

关注

0文章

37浏览量

9813

原文标题:IAR Systems RISC-V 功能安全版开发工具支持最新 SiFive 汽车解决方案

文章出处:【微信号:IAR爱亚系统,微信公众号:IAR爱亚系统】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

IAR即将亮相上海汽车电子与RISC-V顶级盛会

重磅合作!Quintauris 联手 SiFive,加速 RISC-V 在嵌入式与 AI 领域落地

SiFive车规级RISC-V IP获IAR最新版嵌入式开发工具全面支持,加速汽车电子创新

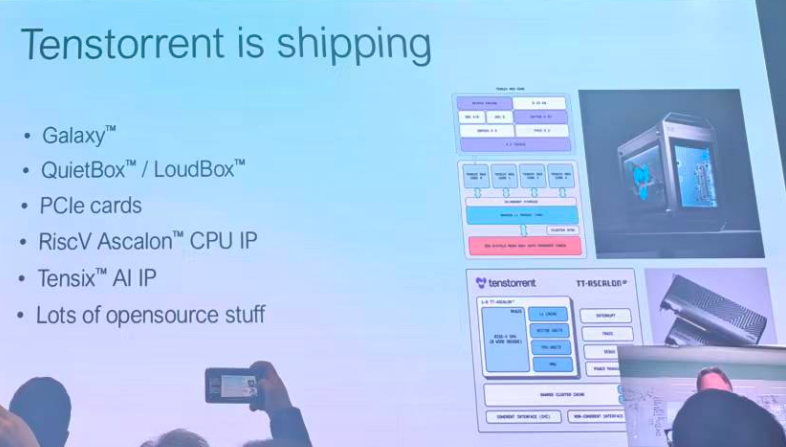

Jim Killer掌舵,Tenstorrent CPU IP进军高性能计算,AI令RISC-V势在必得

高通收购Ventana Micro Systems,深化RISC-V CPU技术专长

润和软件旗下润开鸿获评2025年度RISC-V优秀产品与解决方案

为什么RISC-V是嵌入式应用的最佳选择

兆松科技ZCC-FuSa编译器全面支持晶心科技车规级RISC-V处理器IP核

IAR携手矽力杰与普华基础软件加速RISC-V车规芯片发展

SiFive 上海芯伍科技邀您参加2025 RISC-V中国峰会!

IAR发布RISC-V开发工具链v3.40.1版本

智芯公司RISC-V高性能CPU芯片获得权威认可

RISC-V架构CPU的RAS解决方案

DC-ROMA RISC-V AI PC 正式发布!

IAR Systems持续为SiFive 的RISC-V车用CPU IP提供解决方案

IAR Systems持续为SiFive 的RISC-V车用CPU IP提供解决方案

评论