首先看下下面的这个示例:

module PU;

int A[2:0][3:0][4:0], B[2:0][3:0][4:0], C[5:0][4:0];

initial

begin

A[0][2][4] = 1024; //row 0, column 2, element #4

//display index #4 (i.e., 5th element)

$display("A[0][2][4]=",A[0][2][4]);

//display 5 elements of row 0, column 2

$display("A[0][2]=",A[0][2]);

//display row 0 (4 columns; 5 elements each)

$display("A[0]=",A[0]);

//display 3 rows * 4 columns of 5 elements each

$display("A=",A);

$display("

");

B[1][1][1]=512; //row 1; column 1; element #1

// assign a subarray composed of fve ints

A[2][3] = B[1][1];

//display 5 elements of row 2, column 3

$display("A[2][3]=",A[2][3]);

B[0][0][0]=128; //Assign only to the last unpacked element

A[1] = B[0];

$display("

");

$display("A[1]=",A[1]); //display row 1 (4 columns; 5

elements each)

C[5][4]=64;

A[0][1] = C[5];

$display("

");

$display("C[5]=",C[5]);

$display("A[0][1]=",A[0][1]);

end

endmodule

仿真log:

A[0][2][4]= 1024 //index #4 (i.e., 5th element)

A[0][2]='{1024, 0, 0, 0, 0} //5 elements of row 0, column 2

A[0]='{'{0, 0, 0, 0, 0}, '{1024, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}}

//4 columns of row 0 with value assigned to column 2, element #4 (5th position)

A='{'{'{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}}, '{'{0, 0, 0, 0,

0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}}, '{'{0, 0, 0, 0, 0}, '{1024, 0, 0,

0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}}}

//Entire 3 rows*4 columns (12 entries – 5 elements each with value assigned to

column 2, element #5)

A[2][3]='{0, 0, 0, 512, 0} // display 5 elements of row 2, column 3

A[1]='{'{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 128}}

// display row 1 (4 columns; 5 elements each)

C[5]='{64, 0, 0, 0, 0} //Row 5, 5 elements with index 4 assigned

A[0][1]='{64, 0, 0, 0, 0} //Row 0, column 1 of 5 elements

V C S S i m u l a t i o n R e p o r t

Packed和Unpacked数组作为子程序的参数

数组可以作为参数传递给子程序,当数组作为值传递给子程序时,会将这个数组复制一份传递给子程序。

task trial (int a[3:1][3:1]); //’a’ is a two-dimensional array

//(2-D unpacked)

上面是一个SystemVerilog task声明的示例,该task会将一个2维unpacked数组作为参数值传递。

int b[3:1][3:1]; // OK: same type, dimension, and size

int b[1:3][0:2]; // OK: same type, dimension, & size

// (different ranges)

logic b[3:1][3:1]; // ERROR: incompatible element type

// (logic vs. int)

event b[3:1][3:1]; // ERROR: incompatible type (event

vs. int)

int b[3:1]; // ERROR: incompatible number of dimensions

int b[3:1][4:1]; // ERROR: incompatible size (3 vs. 4)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Verilog

+关注

关注

31文章

1374浏览量

114749 -

数组

+关注

关注

1文章

420浏览量

27484

原文标题:SystemVerilog中数组的赋值、索引和切片

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

MySQL慢查询分析与索引调优全流程

MySQL 性能问题在生产环境中的表现通常是渐进式的:业务量增长、数据量膨胀,某天突然发现 P99 响应时间从 50ms 涨到 2s。慢查询是最常见的根因,而索引设计不合理又是慢查询的主要来源。

PCB切片分析新方案:Bamtone MS90集成AI的智能测量解决方案

在电子制造业飞速发展的今天,PCB切片分析作为评估PCB内部结构质量的关键手段,正经历着一场由人工智能技术驱动的深刻变革。作为国内领先的PCB测量仪器、智能检测设备等专业解决方案供应商——班通科技

Bamtone S/SV系列自动取样机:一种PCB电路板自动切片取样机及取样方法

在电子制造中,传统PCB切片取样依赖于手工操作,不仅效率低下,且存在取样位置偏差、样品损伤率高等问题,难以满足现代电子制造业对高精度、高效率质量检测的需求。作为国内领先的PCB测量仪器、智能检测设备

数组的初体验

程序中也需要容器,只不过该容器有点特殊,它在程序中是一块连续的,大小固定并且里面的数据类型一致的内存空间,它还有个好听的名字叫数组。可以将数组理解为大小固定,所放物品为同类的一个购物袋

发表于 11-25 08:06

二维数组介绍

] = { {1, 2,3}, {4, 5,6},{7, 8, 9}};array[1][1] = 5;

或许你以为在内存中 array 数组会像一个二维矩阵:

123456789

可实际上它是这样

发表于 11-25 07:42

三维成像技术:共聚焦成像vs光片成像的光学切片

随着科技的进步,多种显微成像技术应运而生,其中共聚焦显微镜和光片显微镜因其优异的光学切片能力备受关注,这两类设备分别依托共聚焦成像与光片成像技术实现切片功能,且在成像原理、适用场景及实际应用效果上

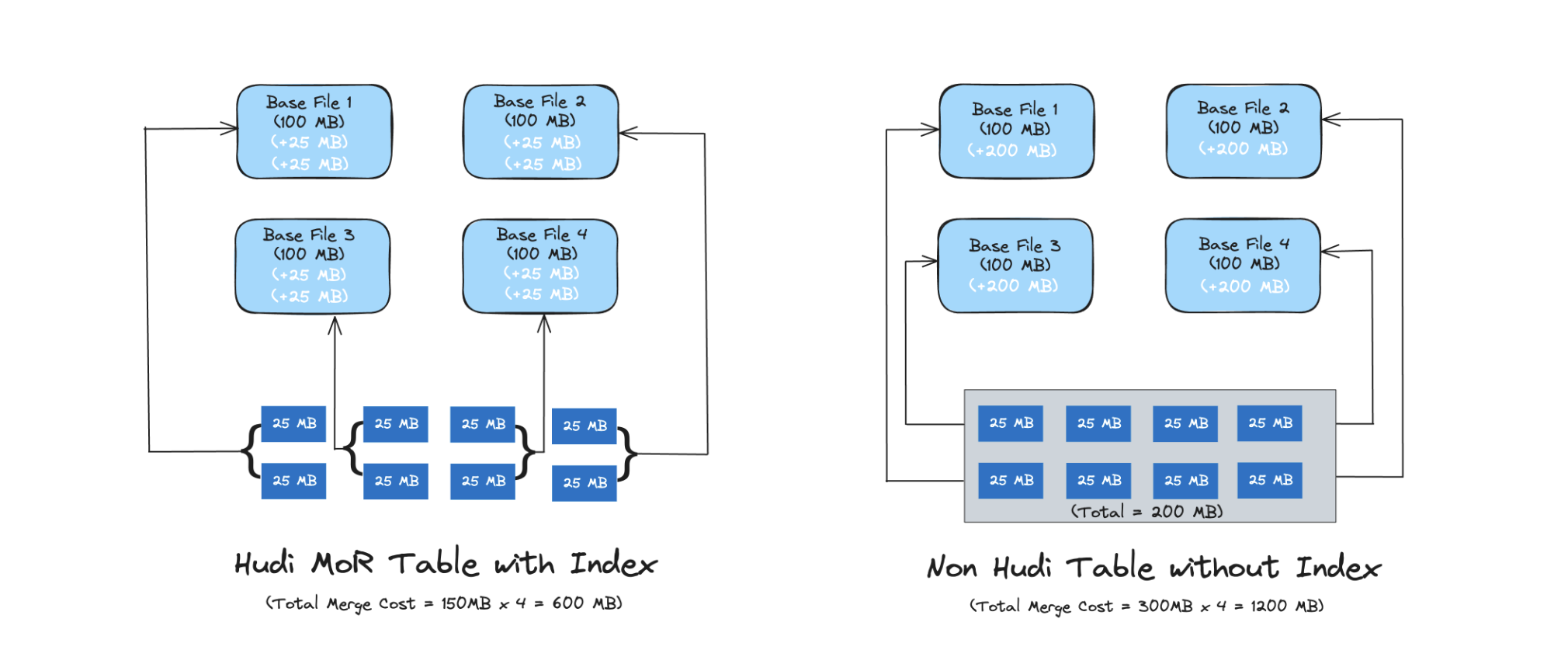

Hudi系列:Hudi核心概念之索引(Indexs)

上的Instant action操作类型 ▪1.4 时间线上State状态类型 ▪1.5 时间线官网实例 ◦二. 文件布局 ◦三. 索引 3.1 简介 3.2 对比其它(Hive)没有索引的区别 3.2

华纳云香港服务器数据库索引优化策略

在香港服务器环境中,数据库索引优化是提升整体性能的关键因素。随着企业数据量的不断增长,高效的索引管理能显著提高查询速度并降低服务器负载。本文将深入探讨如何针对香港服务器(特别是其独特的地理和法律要求

请问keil+Env怎么把很大的数组定义到SDRAM中?

keil+Env怎么把很大的数组定义到SDRAM中?

RTT自带的SDRAM程序运行正常,能够申请里面的空间。

但是没有办法把很大的数组——ltdc_lcd_framebuf[1280][800]

定义到SDRAM

发表于 10-11 16:10

aicube的n卡gpu索引该如何添加?

请问有人知道aicube怎样才能读取n卡的gpu索引呢,我已经安装了cuda和cudnn,在全局的py里添加了torch,能够调用gpu,当还是只能看到默认的gpu0,显示不了gpu1,gpu0是集显,训练速度太感人了

你只有一块英伟达的卡,aicube不支持AMD的显卡,所以搜索到的只有一张卡

发表于 07-25 08:18

matlab appdesigner 表格组件赋值问题,求助

如上图所示,我在用matlab2021Ra APP模块进行编程的时候,想在表格中调入自己编写的结构数组,我从网上AI了一个程序语句,看着没问题,但是就是给表格赋值不了,还请各位大神帮忙看一下这个是怎么回事,我是初学者,请各位帮

发表于 07-12 11:45

如何使用闪存来保存 CYBT-343026 中的数组等数据?

您好,我正在尝试使用 CYBT-343026 构建一块电路板。

我想将数据存储在一个简单的数组中。T

即使断电,数据也应该保留。我可以使用EEPROM,但由于数据非常简单,所以我想使用内部闪存。

有没有办法在内部闪存中存储大约2

发表于 06-25 06:33

SystemVerilog中数组的赋值、索引和切片

SystemVerilog中数组的赋值、索引和切片

评论