Hello everybody,我们接着上期的Process(1)-产生进程的方式继续讲解SystemVerilog中对于process的多种控制方式。 本期黄鸭哥主要给大家讲解 named block、wait_order、wait_fork、disable,还有SystemVerilog中的内建类:process类。

1

Namedblock

Block,也就是语句块,SystemVerilog提供了两种类型的语句块,分别是begin…end为代表的顺序语句块,还有以fork…join为代表的并发语句块。 这两种block都是工程项目中常用的block,但是,大家可能都不知道block也是可以命名的,就像我们每个人的名字一样,名字是我们每个人的一个标识。 通过这个标识,我们可以访问block中的变量、parameter等。

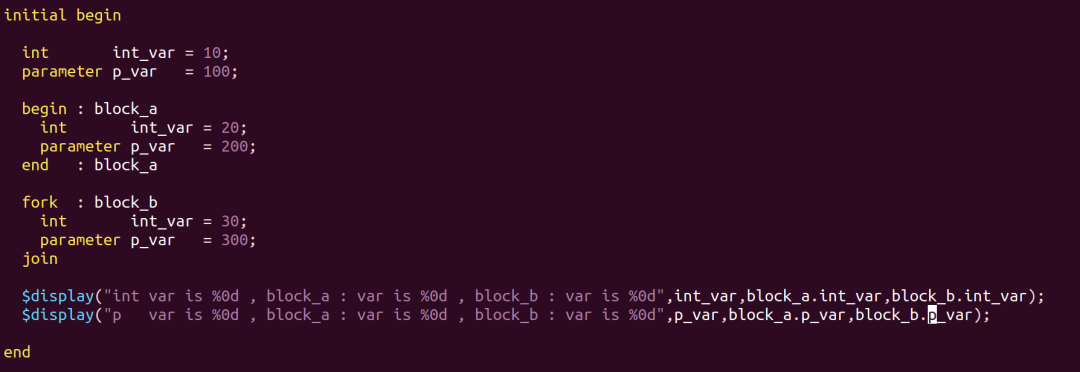

图1

图1中,initial begin…end中有两个named block,分别为顺序执行的block_a和并发执行的block_b。

我们可以通过在block的开头和结束编写上标识名,也可以只在开头进行编写;

如果是在block的开头和结束都有对应的标识名,则这两标识名必须相同,否则会编译报错。

图2

从图1和图2中我们还可以看到,int类型的变量和parameter的作用范围都是在各自block范围内的。

所以,我们要记住,如果需要访问block中的变量或者parameter,则需要给block进行命名,并且,block中的变量、parameter都是相互独立的。

2

wait_order、wait fork

SystemVerilog提供了两大类process的控制方式,分别为wait和disable。 wait中又包含了三小类:wait、wait_order、wait fork。 其中,wait相对简单,在这就不说了,黄鸭哥只介绍后两种。 那么,什么是wait_order? 黄鸭哥总结一句:wait_order会阻塞等待多个事件的触发,并且要求这几个事件间发生的顺序和设置的一致。 这句话该怎么理解呢?我们来看下例子:

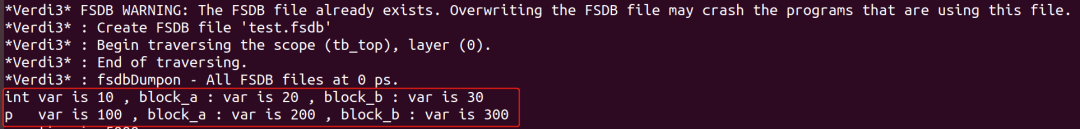

图3

例子中包含3个event,3个event分别在3个并发进程中进行触发,event_1在第50个timeunit被触发,event_2在第30个timeunit被触发,event_3在第100个timeunit的时候被触发。

wait_order需要阻塞到3个事件依次按照event_2、event_1、event_3的顺序进行触发后才能往下执行。这就是wait_order的用法。

wait中另外一个重要的用法是wait fork,关于它的用法,黄鸭哥总结了三句话:

① wait fork会引起调用进程阻塞,直到它的所有子进程结束;

② wait fork的目的是用来确保所有子进程执行结束;

③ wait fork作用父进程下的子进程,而不包括子进程下的子进程。

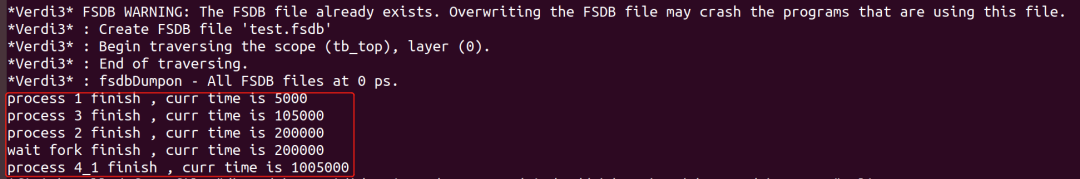

图4

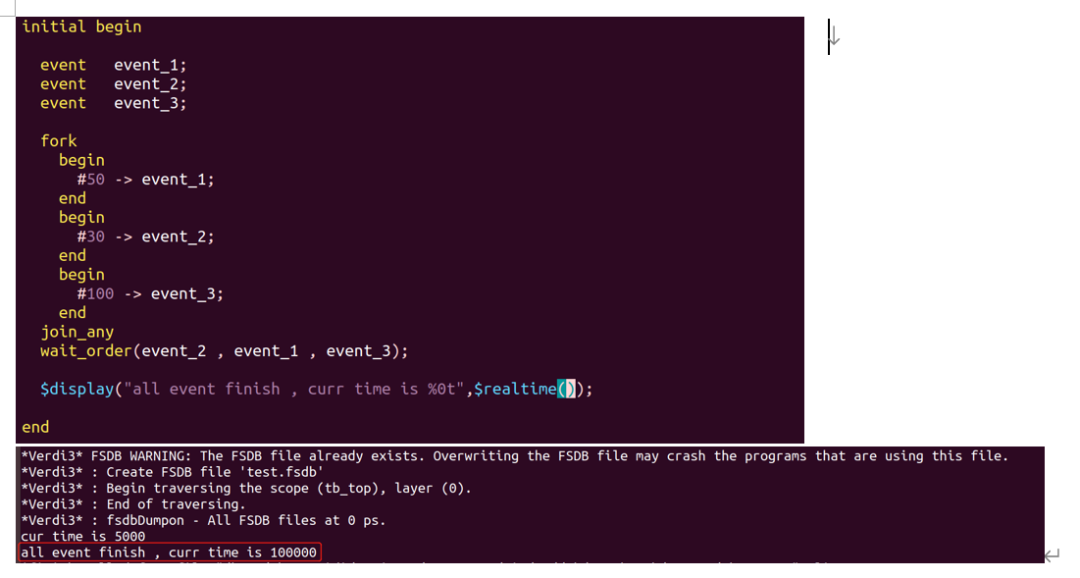

图4中initial语句块包含4个子进程,proc_1~proc_4。

其中,proc_4子进程中还含有一个子进程proc_4_1,此进程就是initial语句块的子进程的子进程。

按照上面黄鸭哥总结的三点来看,wait fork应该只需要等待到第2个子进程:proc_2执行结束,因为wait fork只会作用到子进程,不会作用到子进程的子进程(不论是fork…join,fork…join_any还是fork…join_none产生的进程)。

我们来看下仿真结果验证下我们的理论:

图5

果然,wait fork只等待到proc_2,在第200个timeunit就打印出了“wait fork finish”。

3

disable 、disable fork

上面说完了wait,我们接着说SystemVerilog中第二大类的进程控制方式:disable。 disable语句常用的多种方式包括:disable named_block、disable task_name和disable fork等,调用disable语句将会终止指定的进程。

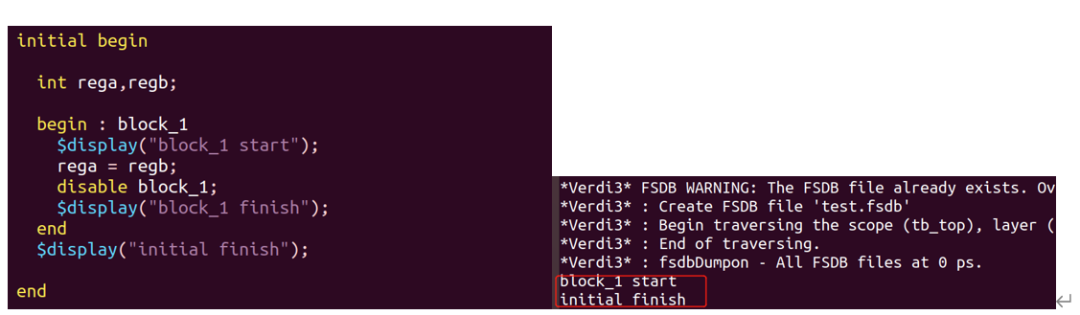

图6

图6里调用了disable,终止了对应的带标识名的block,从仿真截图中可以看出,block_1并没有正常结束,而是中途被终止了。

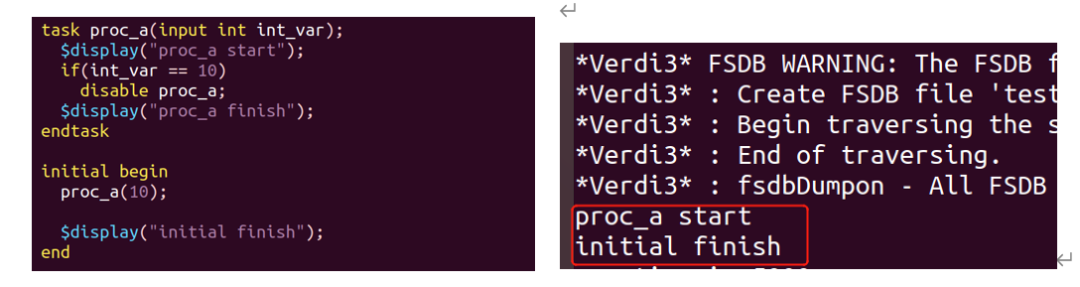

图7

上图中disable proc_a相当于return,它会直接终止当前的task。

而关于disable fork,这个是我们工程项目中使用的最多的一类,也是最容易踩坑的一类,disable fork的用法我推荐大家学习下Q哥的一篇文章:disable fork,你真的会用吗?

感兴趣的同学可以点进去看看,他在里面有很详细的描述,黄鸭哥在这里就不多说了。

4

内建类:process

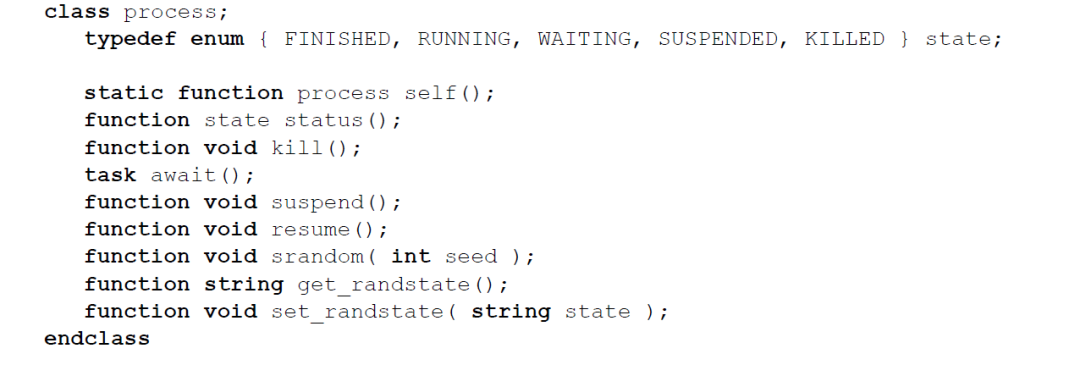

SystemVerilog中内建了一种class,可以对进程进行访问和控制,此种class就是process,我们先来看下process类的原型:

图8

process类中定义了一个枚举变量state,表示当前进程的几种执行状态:FINISHED,RUNNING,WAITING,SUSPENDED,KILLED。

另外,还声明了几种task和function,我们通过下面的表格来简单了解下:

表1

有人会问了,这么多的method,我们都该记住吗?

黄鸭哥觉得不是的,只需要记住这里面常用的几个method:self(),status(),kill()就可以了,我们最后再来看个例子,加深下理解:

| Method | Describe |

| self() | 获取当前进程的句柄,process类不能主动的通过new来进行创建,只能通过initial…begin…end,final…begin…end,4个always procedure,3个fork procedure和dynamic process来产生 |

| status() | 获取当前进程的状态:FINISH: 该进程已经结束了RUNNING: 该进程正在运行WAITING: 该进程等待阻塞条件SUSPENDED:该进程停止了,等待resume,当前状态只能通过调用process类中的resume函数来解除KILLED: 该进程被强制终止了 |

| kill() | 终止该进程以及该进程的子进程 |

| await() | 等待其他进程结束,不能在该进程中,调用该方法,只能是别的进程调用本进程的await()来阻塞本进程 |

| suspend() | 挂起该进程 |

| resume() | 恢复该进程 |

| srandom(int seed) | 设置进程的随机种子 |

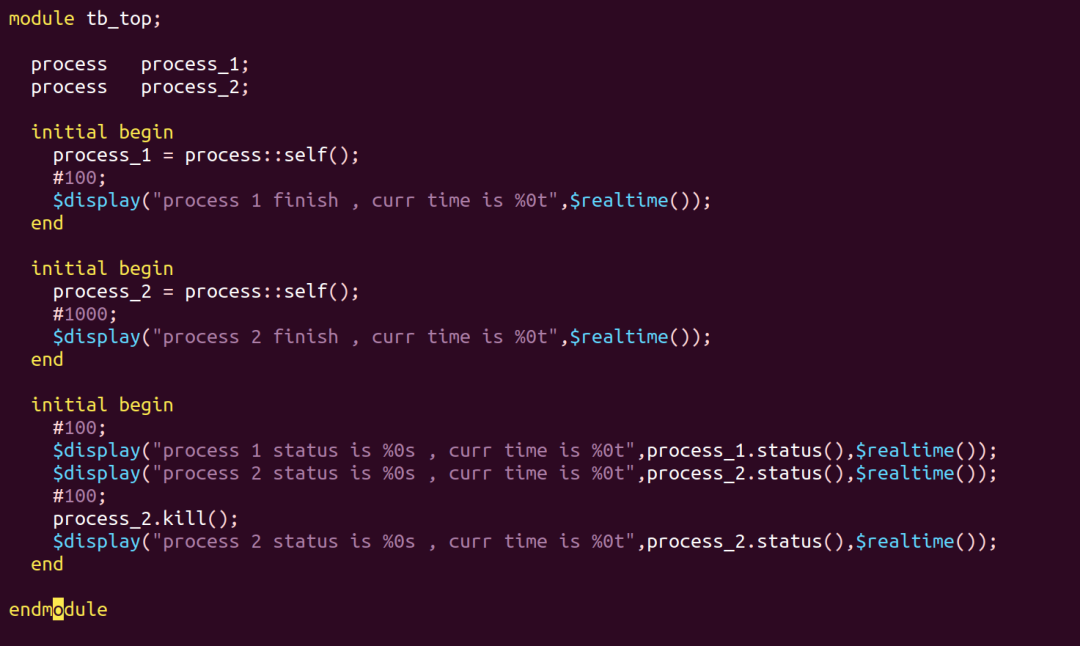

图9

图10

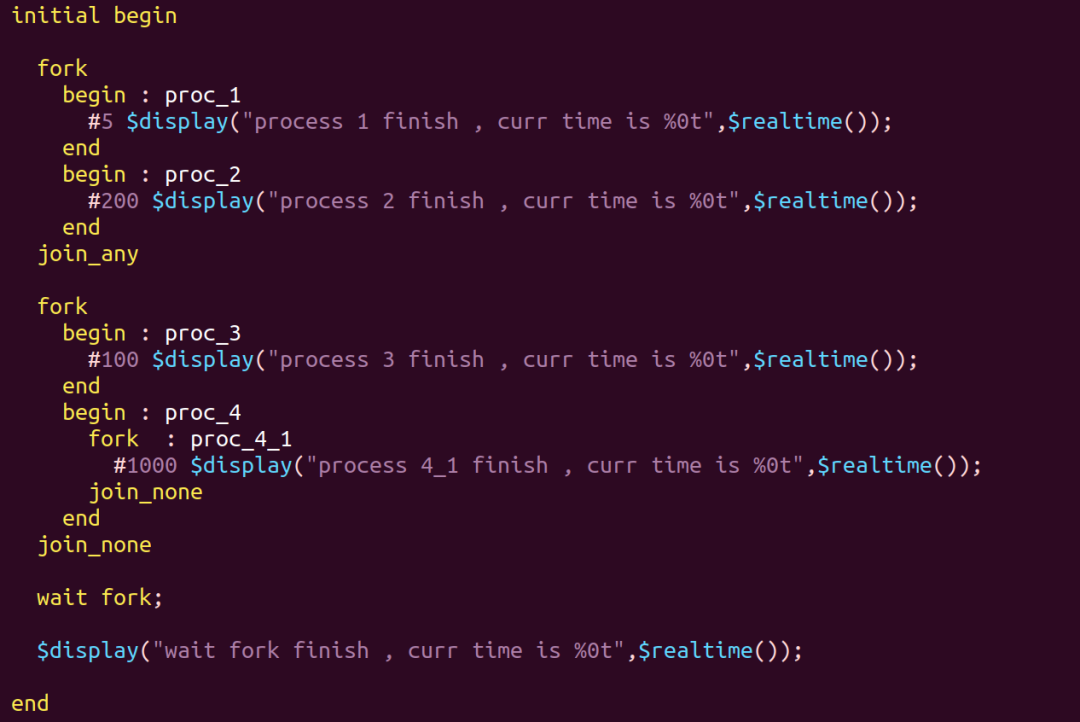

图9展示了这三个method的用法,通过self()获取进程的句柄,然后传递给定义的两个process类;

调用status()可以获取到process_1和process_2进程的执行状态,在100个timeunit的时候,process_1已经执行结束,而process_2则处于阻塞状态;

当再次经过100个timeunit时,调用kill()终止了process_2的继续执行,从这里可以看出,要终止一个进程,除了disable、disable fork之外,还可以调用process.kill()。

总结

process就讲到这了,我们再回顾下今天的要点: 1、block可以进行命名,命名之后就可以通过标识名访问block内部的变量和parameter,还可以通过disable named_block终止此block。 2、进程的两大控制方式:wait、disable。 3、SystemVerilog内建类,process类,可以通过process类访问进程和控制进程。 4、三种终止进程的方式:disable、disable fork、process.kill()。 审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Verilog

+关注

关注

31文章

1374浏览量

114716 -

Block

+关注

关注

0文章

26浏览量

15174 -

Process

+关注

关注

0文章

17浏览量

12492

原文标题:扒一扒SystemVerilog中的Process之进程控制

文章出处:【微信号:Rocker-IC,微信公众号:路科验证】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

几个方面了解变频器v/f控制方式

变频器的V/F控制方式,核心思想是 保持电机磁通恒定 ,从而实现平滑调速。为了让你全面了解它,我整理了以下几个关键方面: 核心原理:恒磁通调速 V/F控制的基本原理,是让变频器输出的电压(V)和频率

无刷减速电机MCU控制方式与间隙要求

无刷减速电机作为一种高效、低噪音、长寿命的驱动装置,广泛应用于工业自动化、机器人、医疗设备等领域。其核心控制依赖于微控制器单元(MCU),而机械传动中的间隙问题直接影响系统精度和稳定性。本文将深入探讨无刷减速电机的MCU

RGB时序灯条的工作原理讲解

图文配合讲解了RGB时序灯条的应用场景、什么是RGB时序灯条、信号格式与传输规则、灯珠芯片的工作流程、颜色与动态效果控制方式等

发表于 02-06 11:36

•0次下载

博世GTM IP模块在车载系统中的具体实现方式与优势

在汽车电子系统中,如何充分发挥 GTM IP的功能,以满足复杂的系统级应用场景,是用户实现高效控制与精确响应的关键。本文将聚焦几个典型且核心的应用实例,探讨GTM IP在车载系统中的具体实现方

串口通信有哪些方式

串口通信(Serial Communication)是一种通过串行方式逐位传输数据的通信方式,广泛应用于嵌入式系统、工业控制、仪器仪表等领域。其通信方式可根据不同的分类标准划分为

如何在LTspice中添加电压控制开关

电压控制开关是 LTspice 的基本电路元件,能够以简洁的方式在电路中实现开路或短路行为,并支持在仿真过程中动态切换。完善原理图后,设计人员最终可能需要采用更精确的FET或开关模型,

TCP攻击是什么?有什么防护方式?

出DDoS高防产品、CC防御产品,但是对于TCP攻击的防护不是特别的理想。那么, TCP攻击是什么?有什么防护方式? TCP攻击是什么? TCP攻击是指利用TCP协议中的漏洞或者缺陷对网络进行攻击的行为。这种攻击

芯资讯|广州唯创电子WT2003H语音芯片控制方式全解析

在智能硬件开发中,语音芯片的控制方式直接影响设备的功能设计与用户体验。广州唯创电子WT2003H系列语音芯片凭借其多样化的控制接口和灵活的交互设计,成为工业设备、智能家居及新能源汽车等

【干货分享】开关电源环路补偿设计步骤讲解

1. 理论讲解 本文将讲述实际环路补偿的设计步骤。 对于硬件工程师来说,开关电源和运放的信号处理电路是最常遇到的,都是典型的带负反馈的闭环控制系统。因此,这两类电路设计的稳定性和控制理

发表于 04-28 17:02

如何合理地选用变频器控制方式?

合理地选用变频器的控制方式,需要根据实际的应用场景、负载特性以及控制需求等多方面因素进行综合考虑。以下是一些具体的选用原则和建议: 一、应用场景与控制需求 1. 节能需求: ●

讲解SystemVerilog中对于process的多种控制方式

讲解SystemVerilog中对于process的多种控制方式

评论