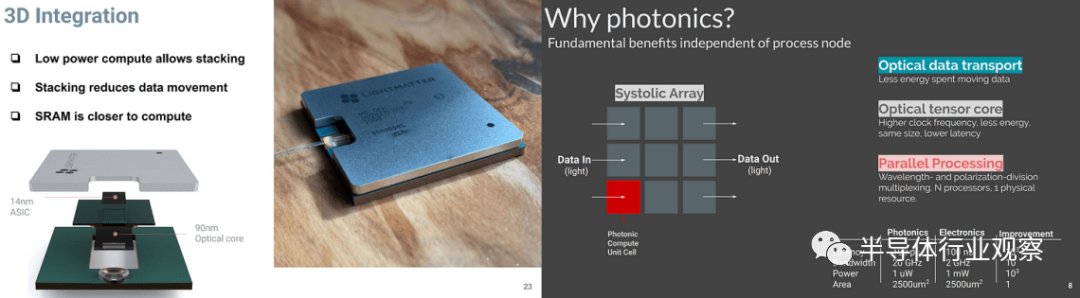

几年前,Lightmatter 通过展示人工智能加速器 Mars 引起了轰动,该加速器重新思考了电子计算和移动数据的范式。他们展示了一种使用光子学进行计算的处理器。该芯片承诺将延迟、带宽和功率提高多个数量级。由于芯片所涉及的软件和计算结构的刚性,这最终没有成功。

Lightmatter 已经创建了名为 Envise 的第二代 AI 计算产品,但这不是今天帖子的重点。我们想分享 Lightmatter 在他们的最新产品 Passage 上展示的内容。总结就是,Lightmatter 希望通过 Passage 打破高级封装和 IO 的限制。

众所周知,AI 和 HPC 等领域的问题规模呈指数级增长,但摩尔定律无法跟上。

因此,该行业已转向使用chiplet来组合更大的封装,以继续满足计算需求。将芯片分解成许多chiplet并超过标线限制(光刻工具的图案化限制的物理限制)将实现持续缩放,但这种范例仍然存在问题。即使采用先进的封装,将数据移出芯片的电力成本也将成为限制因素。此外,即使采用最先进的封装形式,带宽仍然有限。

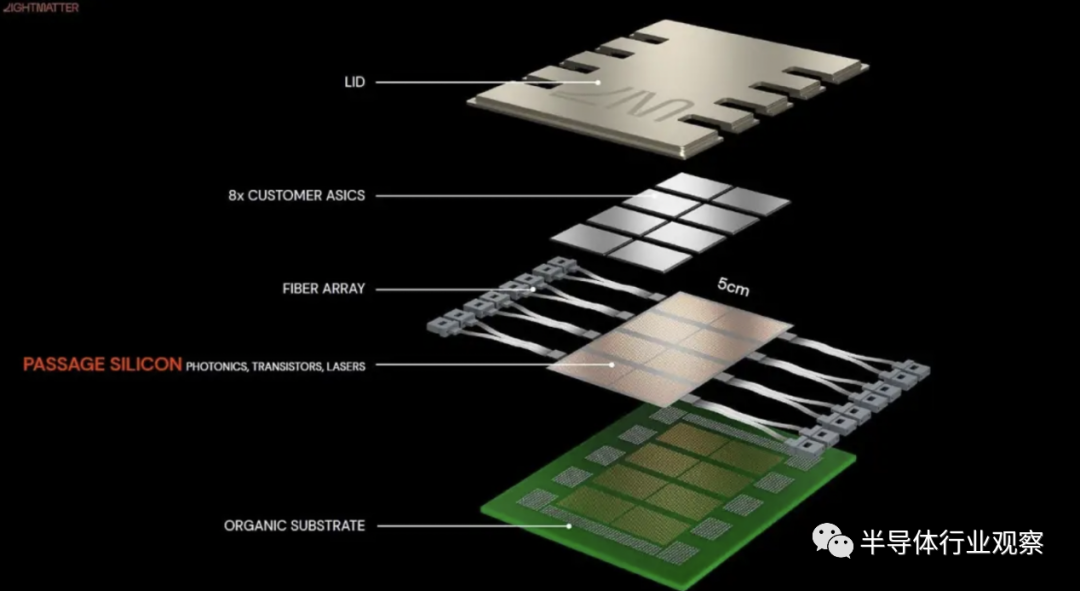

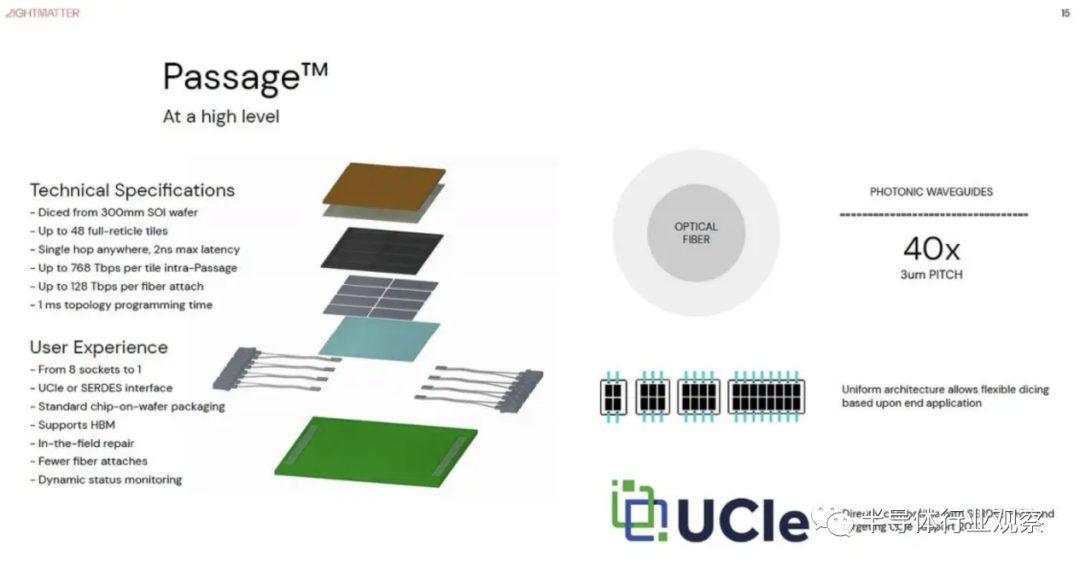

Lightmatter 不想将硅放在硅上,而是希望通过 Passage 颠覆先进的封装游戏。Passage 连接到光学中介层上的 48 个客户芯片。Passage 建立在GlobalFoundries Fotonix 45CLO 工艺技术之上。它旨在以非常高的带宽和性能连接许多芯片。这种optical interposer打破了带宽限制,在每个tile之间提供每秒 768 太比特,并且可以以每秒 128 太比特扩展到多个interposers,这是传统封装无法达到的能力和规模水平。

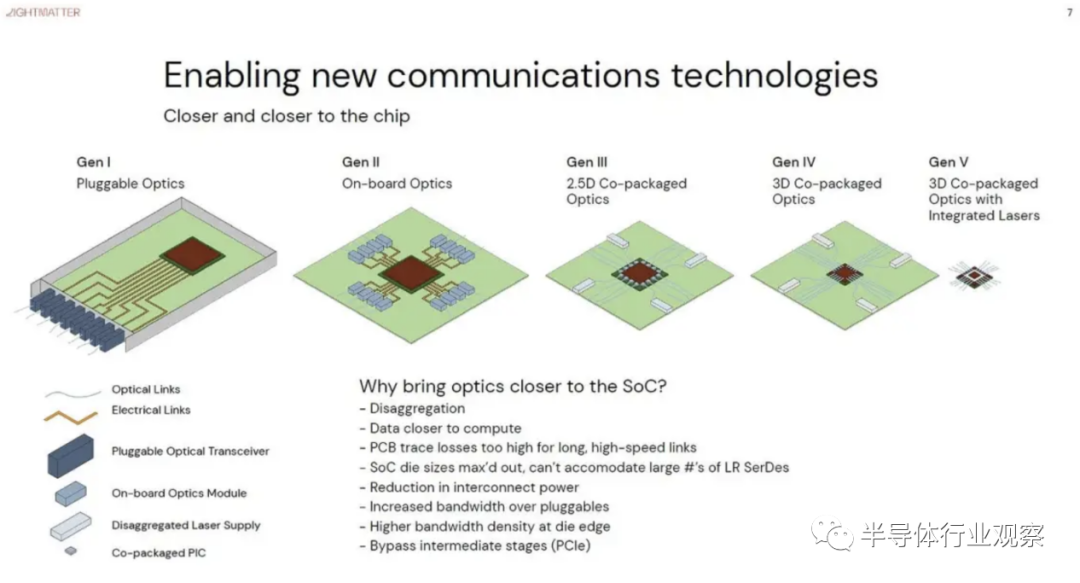

几十年来,光学一直承诺解决电气 IO 的瓶颈。技术在这方面的进展缓慢。Lightmatter 称之为 Gen 1 的可插拔光学器件多年来一直用于连接数据中心内的交换机。由于英特尔和Ayar Labs等公司,第 2 代和第 3 代光学器件(将光学器件放在同一个封装上或直接连接)开始进入网络交换机和计算领域。Lightmatter 想通过 Passage 直接跳到第 4 代和第 5 代。

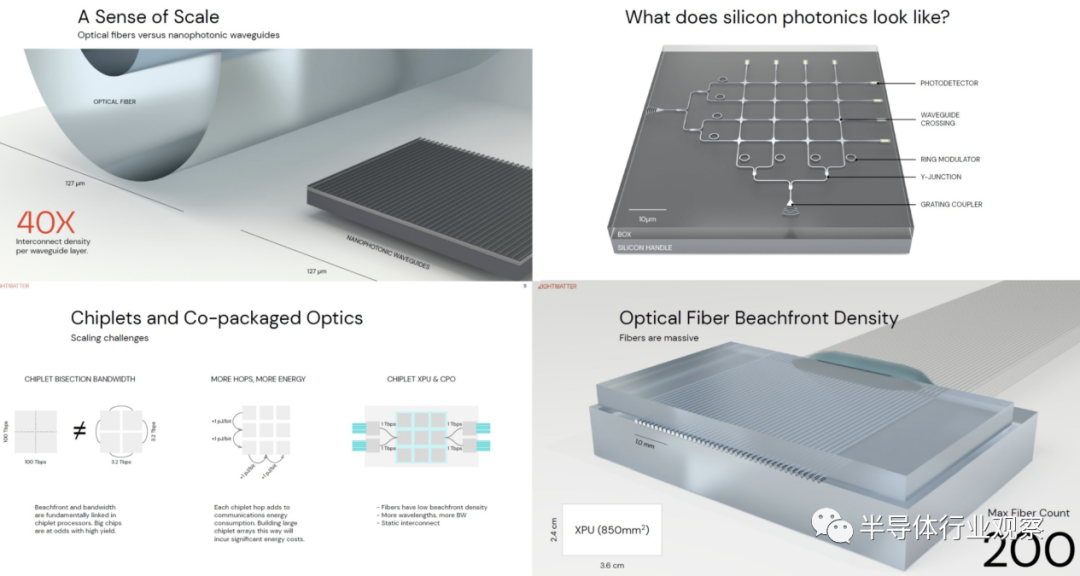

英特尔和 Ayar Labs 等标准联合封装光学器件的规模比 Lightmatter 使用的光学中介层解决方案低一个数量级。其互连密度高出 40 倍,因为单个芯片中只能插入大约 200 根光纤。此外,互连是完全静态的,而 Passage 具有可动态配置的结构。

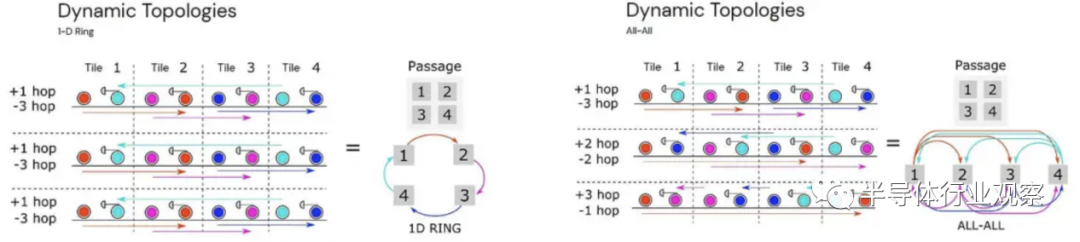

这种光中介层可以在芯片之间进行交换和路由。整个互连可以在 1ms 内重新配置。

Lightmatter 表示,他们可以支持所有拓扑,例如 all to all、1D ring、Torus、Spine 和 Leaf 等等。Passage 的交换和路由在 48 芯片阵列上的任何芯片与任何其他芯片之间的最大延迟为 2ns。

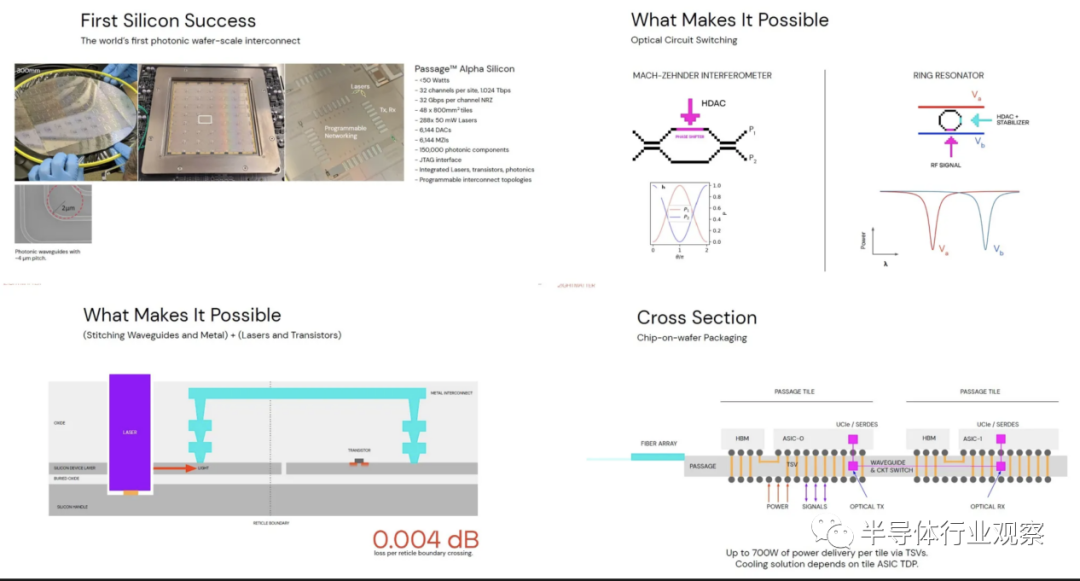

切换是通过使用环形谐振器调制颜色并使用马赫-曾德干涉仪来引导它们来实现的。

Lightmatter 的光子晶圆级中介层具有 A0 硅,并声称每个站点使用的功率不到 50 瓦。每个站点有 8 个混合激光器驱动 32 个通道;每个通道运行 32Gbps NRZ。

Lightmatter 的晶圆级硅光子芯片主要采用硅基制造技术;它有许多相同的限制。即光刻工具的标线限制。GlobalFoundries 和 Lightmatter 通过缝合波导解决了这个问题。纳米光子波导的光罩间连接在每个光罩交叉处仅具有 0.004 dB 的损耗。波导损耗为 0.5 dB/cm,每个 Mach-Zehnder 干涉仪损耗为 0.08 dB。每次交叉也有 0.028 dB 的损耗。

Lightmatter 表示,借助 UCIe,他们可以运行最高规格的 32Gbps chiplet到中介层互连。如果使用直接 SERDES,他们相信它们可以以 112G 的速度运行。客户 ASIC 被 3D 封装在中介层之上。然后 OSAT 将组装这个最终产品。它可以有多种变体,从 48 个芯片到只有 8 个芯片的更小的interposer。passage封装还必须为封装在顶部的芯片供电。它通过使用 TSV 为每个tile提供高达 700W 的功率来做到这一点。在这个功率级别需要水冷,但如果客户 ASIC 消耗较少,他们可以使用空气冷却。

请注意,声称的 768Tbps 似乎在很大程度上被浪费了。它们的功能似乎允许它们将一个输入耦合到一个输出。这使得大部分互连空闲。为了让他们找出不冲突的途径,这将是必要的。这些路径是被动的,在不使用时几乎不会浪费电力。MZI 元素向左或向右。没有混合(blending),没有多播(multicasting)。一进一出。

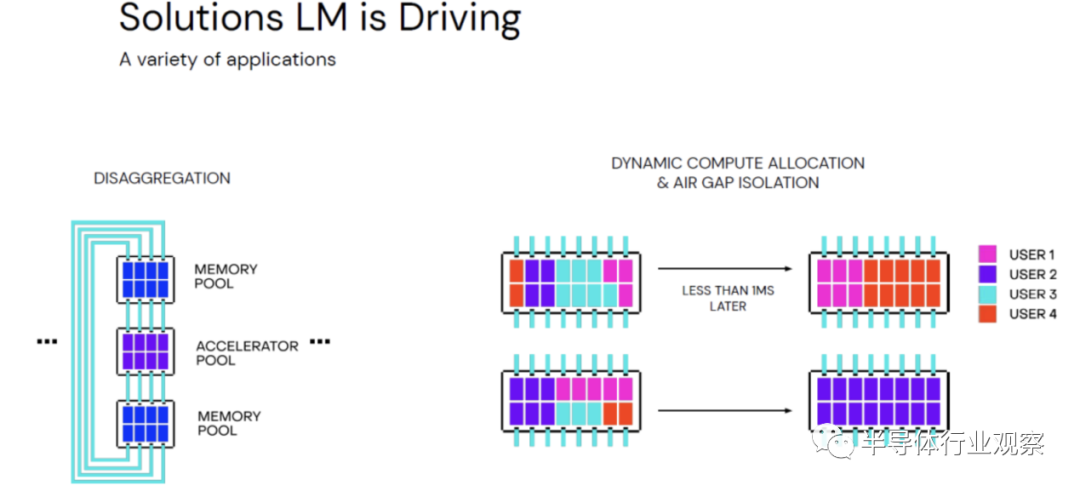

Lightmatter 还举了一个分解内存设计和多租户架构的例子。他们开始他们的 interposer可以支持任何协议,包括 CXL。interposer顶部的客户 ASIC 可以通过重新配置网络实现气隙,因此在特定芯片之间传递数据是不可能的。最大的问题是产品是否会出现以及何时会出现。这可能只是vaporware,也可能是高端领先的分类服务器设计的未来。Lightmatter 必须吸引其他公司为这个平台制造芯片。这些公司必须将其昂贵的开发信任与未经证实的合作伙伴。

审核编辑 :李倩

-

封装

+关注

关注

128文章

9330浏览量

149044 -

人工智能

+关注

关注

1820文章

50324浏览量

266932 -

chiplet

+关注

关注

6文章

499浏览量

13648

原文标题:颠覆先进封装,光芯片走向Chiplet

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

长电科技亮相先进封装开发者大会机器人与汽车芯片专场

先进封装时代,芯片测试面临哪些新挑战?

多Chiplet异构集成的先进互连技术

西门子EDA如何推动Chiplet技术商业化落地

当芯片变“系统”:先进封装如何重写测试与烧录规则

Chiplet核心挑战破解之道:瑞沃微先进封装技术新思路

Chiplet封装设计中的信号与电源完整性挑战

解构Chiplet,区分炒作与现实

Chiplet与先进封装全生态首秀即将登场!汇聚产业链核心力量共探生态协同新路径!

华大九天推出芯粒(Chiplet)与2.5D/3D先进封装版图设计解决方案Empyrean Storm

Chiplet与3D封装技术:后摩尔时代的芯片革命与屹立芯创的良率保障

光芯片走向Chiplet,颠覆先进封装

光芯片走向Chiplet,颠覆先进封装

评论