在摩尔定律的驱动下,存储器和逻辑芯片半导体制造商通过提高晶体管密度来减少产品成本、提升性能[1]。在NAND flash技术中,市场主流是3D结构而不是2D平面结构,这样可以通过增加3D NAND芯片堆叠层数从而线性地增加存储密度[2]。同时,图形化方案的优化也可以提高3D NAND的有效器件密度。本文中,我们将分析不同TCAT (terabit cell array transistor) 3D NAND节点台阶(stair)和狭缝结构(slit)各种图形化方案的优缺点并分析它们对晶体管密度的影响。本研究中使用的方案和数据基于(或取自于)TechInsights发布的逆向工程报告,建模工具是Lam Coventor SEMulator3D 。

图形化方案对制造工艺的影响

在3D-NAND中,决定存储单元和台阶面积的两个最重要因素是狭缝节距和台阶节距。传统上,可以通过减小狭缝和台阶结构的尺寸和节距来减小存储单元和台阶面积,但是会给光刻、蚀刻以及填充工艺带来许多挑战。例如,狭缝节距减小,则通孔节距减小,同时通孔的CD也会变小,这导致蚀刻过程中容易出现通孔之间的桥连,以及通孔和衬底虚连等缺陷。另外,随着台阶尺寸的减小,获得更好的台阶均匀性和更小的尺寸误差的难度也随之加大。很好的工艺窗口控制是非常重要的,只有让接触通孔正好落在台阶正中央才能避免其与台阶侧壁上别的字线短接。在不牺牲工艺窗口(process window) 的情况下如何提高晶体管密度是3D NAND技术开发的一个关键问题。

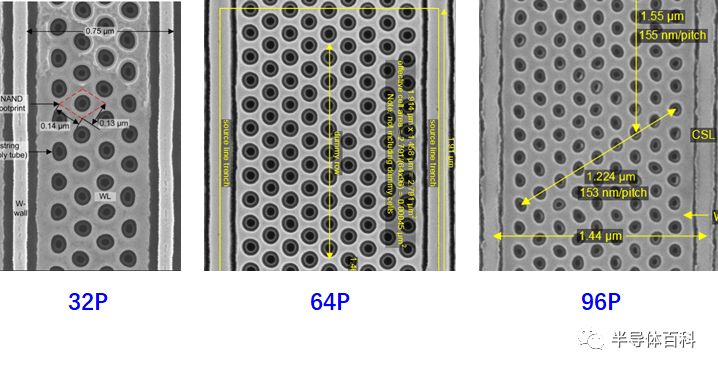

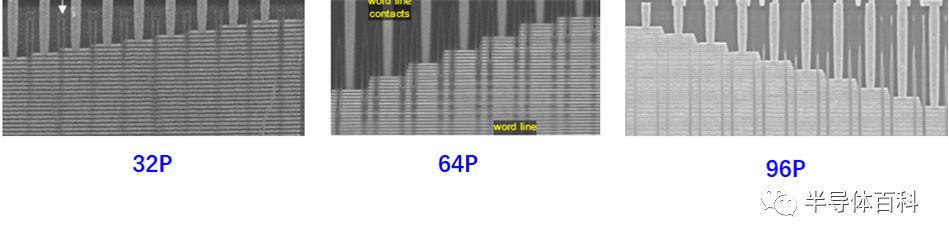

为了进一步探讨这个问题,我们基于TechInsights的逆向工程报告,对32P、64P和96P TCAT 3D NAND进行了建模。图1显示了32P、64P和96P节点的3D NAND狭缝和沟道孔的俯视图,图2是截面图,表1是建模结构的基本尺寸信息。表1中,更高级的节点(64/96P),狭缝和台阶间距被我们加大以增加工艺窗口。64P和96P两个节点,我们增加了每个狭缝的通孔数以及每个台阶的字线(word line)数。我们将讨论如何通过改变图形化方案,在不缩小沟道孔CD和节距的情况下提高存储密度。

图1,不同节点的狭缝和沟道孔俯视图。来源:TechInsights

图2,不同节点台阶横断面图。来源:TechInsights

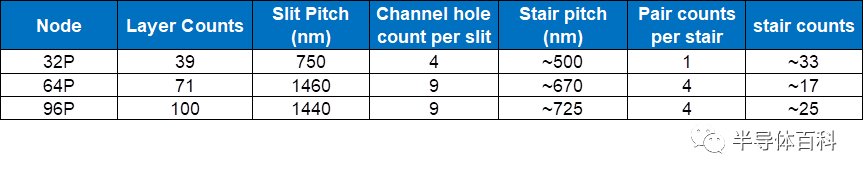

表1,不同节点狭缝和台阶的基本尺寸

超细狭缝图形化方案

在32P TCAT技术节点,每4个存储单元(cell)中的1个可以使用位线和字线的组合在任意两个狭缝之间进行独立寻址。而64P和96P工艺节点,采用了一种超细狭缝(ultra-mini-slit)工艺,切割中间一排通孔,将9排通孔分成左右各4排。这个超细狭缝将NO堆叠顶部的3层分为2个部分,对应着两个独立的字符串线(string line)。通过位线、字线和字符串线的组合,每9个存储单元中的1个可以进行独立寻址。引入超细狭缝有三个好处:

节省了位线方向的面积。与普通狭缝相比,超细狭缝的尺寸更小,相邻通孔之间的空间更小;

工艺难度小。通孔均匀性——尺寸和深度——变得更好;

物理结构更强,因为只有最上面3层被切割,每两个深狭缝之间只有9个通孔。

然而,这这些优点是需要增加了工艺步骤和光罩数来获得的。此外,横向蚀刻和沉积距离较大,使得RMG工艺更具挑战性。

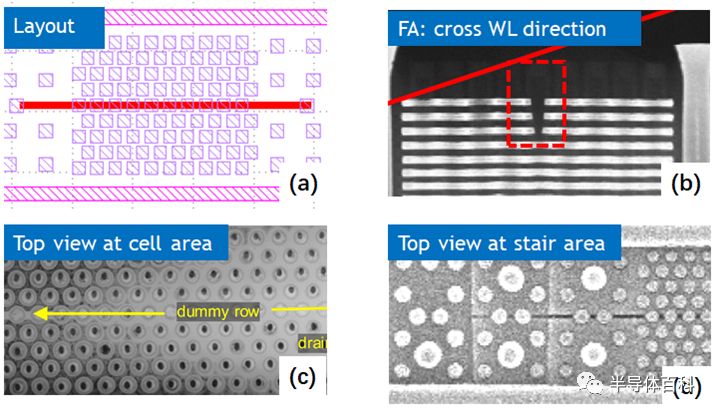

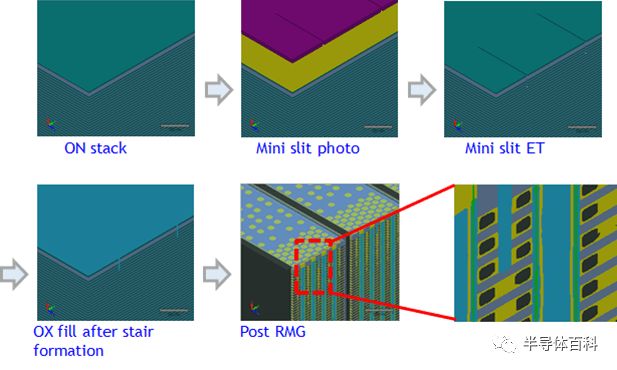

图3显示了超细狭缝版图设计、截面面以及俯视图。图4是SEMulator3D建模的超细狭缝工艺流程图。该工艺流程包括两个步骤,叠层形成后的超细狭缝曝光和蚀刻工艺,以及台阶蚀刻后的超细狭缝和氧化层填充工艺。

图3,超细狭缝(a)版图,(b)截面图,(c)存储单元区域的俯视图,(d)台阶区域的俯视图。来源:TechInsights

图4,微缝形成过程的工艺步骤

台阶工艺分析

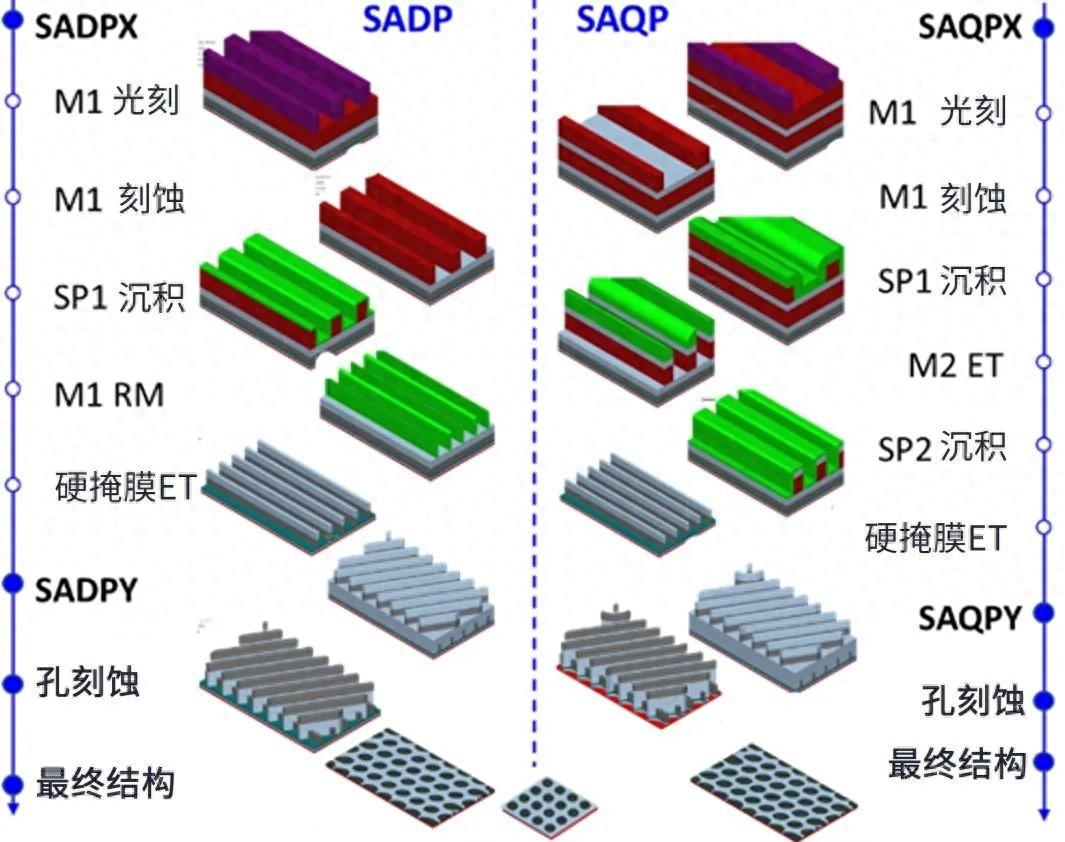

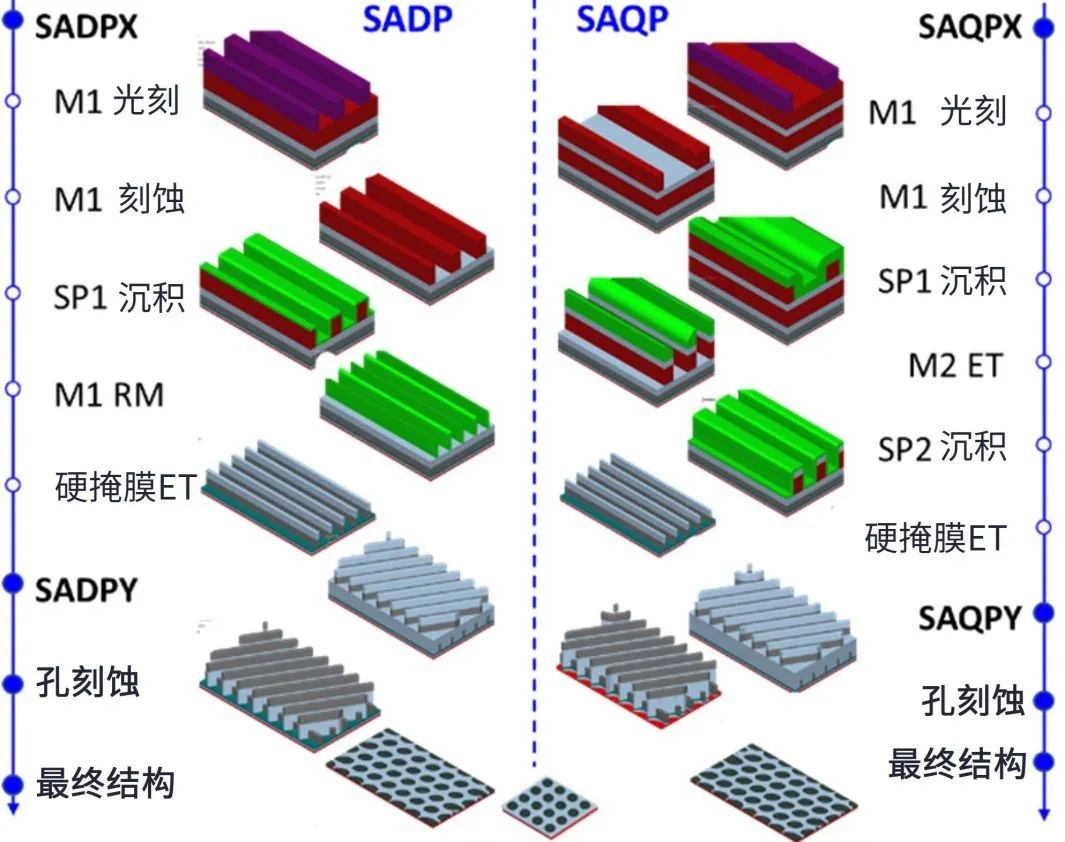

在3D NAND中,字线通过台阶接触孔与后段金属相连,每一层台阶的字线接触孔彼此分开。在32P TCAT工艺(见图2)中,每层台阶对应一条字线,而在64P和96P工艺中,每层台阶包括4条字线,传统上我们需要2张光罩才能将这4组字线区分开来。但是通过厚(光刻)阻工艺和台阶修剪(trim),我们只需要一张光罩就能做到这一点。

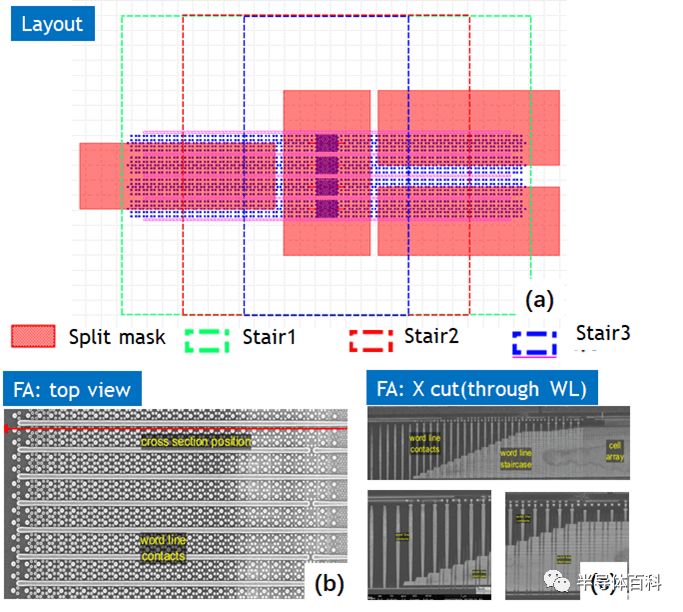

图5是64P工艺的版图设计。我们假设位线是y方向,而字线是x方向。整个存储单元通过3层台阶(图中绿红蓝3种颜色)分为4个不同深度。

j‘a

图5,(a)光罩拆分和台阶光罩的版图设计,

(b)台阶区俯视图,(c)横截面图(垂直位线方向)。来源:TechInsights

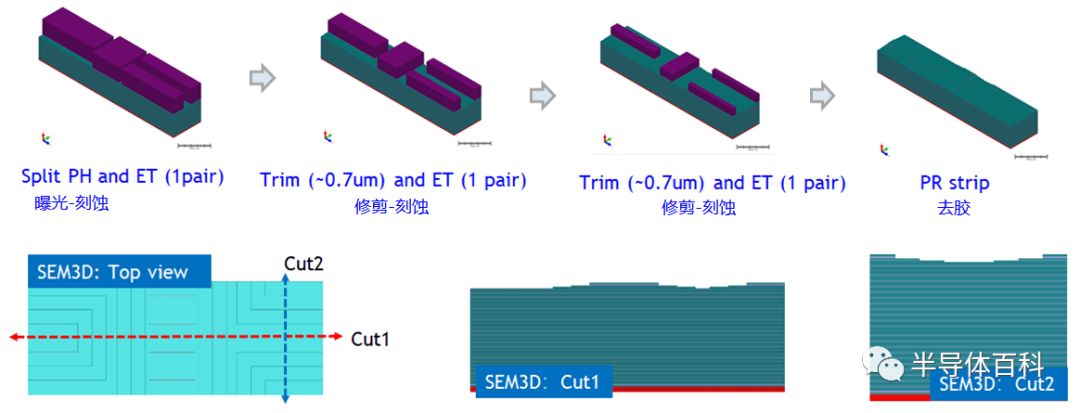

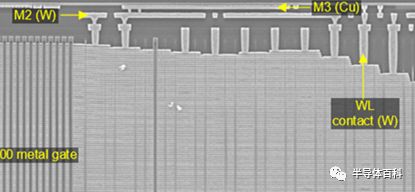

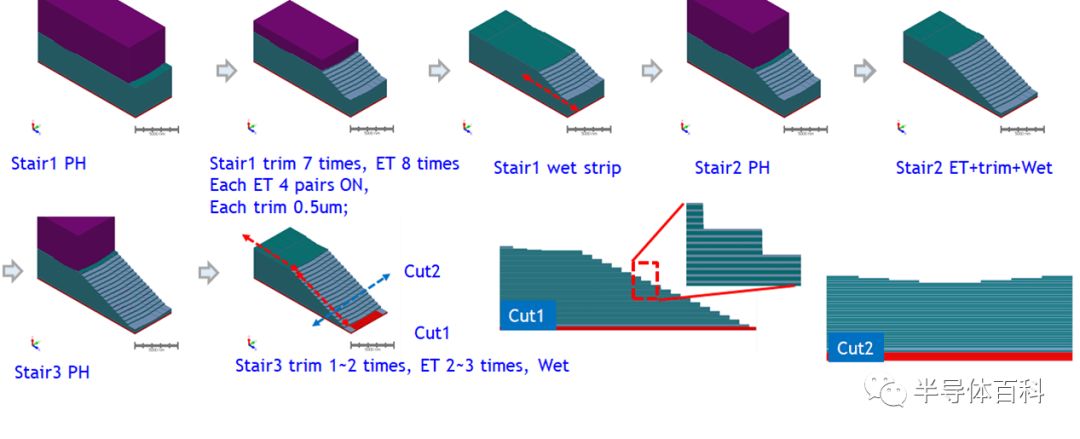

图6是台阶成型过程的三维示意图,完整的成型过程需要1次曝光、3次蚀刻和2次修剪。Y方向上,通过光刻,蚀刻将光阻的边缘与狭缝或小狭缝对齐,每次修剪会在x和y方向消耗约740nm的光阻。图7是一个实际芯片存储单元的台阶剖面图,与图6中的Cut1基本一样,证明了我们模型的准确性。

图6,台阶叠层拆分的工艺步骤

图7,存储单元边缘的台阶剖面图。来源:TechInsights

图8是顶层(4层)台阶形成之后下层台阶(16层)的成型过程,一共需要3次曝光,每次曝光之后需要几次蚀刻和几次修剪,每次修剪消耗约670nm的光刻胶。图8的截面图(Cut1)与图5(c)中的实际SEM图像非常类似,显示了我们建模的准确性。需要注意的是,光刻过程可以是1-》2-》3也可以是3-》2-》1。这种台阶成型方案可以提供多种好处,只需要一张光罩就能区分4组字线,此外,在X方向也只需要更少的光罩。

图8,台阶成型工艺步骤

在这项研究中,我们使用SEMulator 3D来建立3D NAND分割和台阶图案方案的处理模型。SEMulator 3D虚拟制造平台提高了对这些复杂3D-NAND集成方案及其产生的3D结构的理解和可视化,同时提供了一种高效益的时间和成本优化方法。

-

摩尔定律

+关注

关注

4文章

640浏览量

80613 -

晶体管

+关注

关注

78文章

10252浏览量

146279 -

3D结构光

+关注

关注

0文章

12浏览量

680

原文标题:3D NAND 的图形化方案

文章出处:【微信号:半导体设备与材料,微信公众号:半导体设备与材料】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

[分享]图形化系统的设计

labview图形化编程分享!

浅析Mixly图形化编程软件

Mixly图形化编程软件介绍

怎样才能缩短开发图形化系统设计的时间?

浅析半导体行业图形化工艺之光刻工艺

EUV工艺不同多重图形化方案的优缺点及新的进展研究

使用虚拟制造评估先进DRAM电容器图形化的工艺窗口

图形化方案对制造工艺的影响

图形化方案对制造工艺的影响

评论