由于许多行业参与者为其开发做出了贡献,因此在最新的 PCIe 迭代中可能几乎没有什么惊喜——PCIe 特别兴趣小组 (SIG) 现在拥有 900 名成员。在过去的二十年里,PCIe在计算中已经变得无处不在,它支持其他成熟和新兴的标准,例如非易失性内存快速 (NVMe)和计算快速链路 (CXL)。

与其前身类似,PCIe 6.0 针对数据密集型环境,例如数据中心、高性能计算 (HPC)、人工智能和机器学习。但是,随着现代汽车继续演变为轮式服务器(不,轮式数据中心),许多存储技术正在进入汽车应用领域,包括同时使用 NVMe 和 PCIe 的固态驱动器 (SSD)。

PCIe SIG 总裁兼董事会主席 Al Yanes 表示,鉴于 PCIe 是存储空间和 NVMe 的代名词,从战略角度来看,汽车是一个焦点。更不用说汽车正朝着更高的带宽需求发展,就像智能手机自问世以来一样。

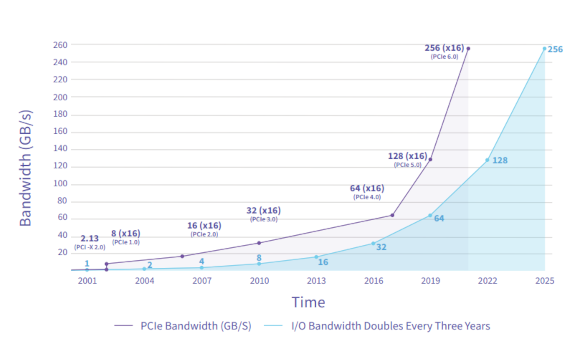

然而,加速器以及 AI 和 ML 应用程序最需要PCIe 6.0 提供的带宽,Yanes 在接受 EE Times 采访时表示这是“革命性的飞跃”。这是因为 PCIe 6.0 提供的带宽是其前身的两倍,可通过 x16 配置提供 64 GT/s 和高达 256 GB/s 的原始数据速率。

PCIe 规范每三年将 I/O 带宽翻一番(来源:PCIe SIG)

PCIe 6.0 还实施了脉冲幅度调制 4 级 (PAM4) 信令和基于流控制单元 (Flit) 的编码,支持 PAM4 调制并与新添加的前向纠错和循环冗余检查结合使用,以实现带宽加倍。Yanes 解释说,所有这些都是在不牺牲延迟的情况下完成的,同时仍然向后兼容 PCIe 5.0。

不是每个人都需要 PCIe 6.0,但它确实提供了在保持带宽的同时减少引脚数的选项,Yanes 说。PCIe SIG 成员了解路线图也很有帮助,这样他们就可以在规划产品时做出明智的决定。

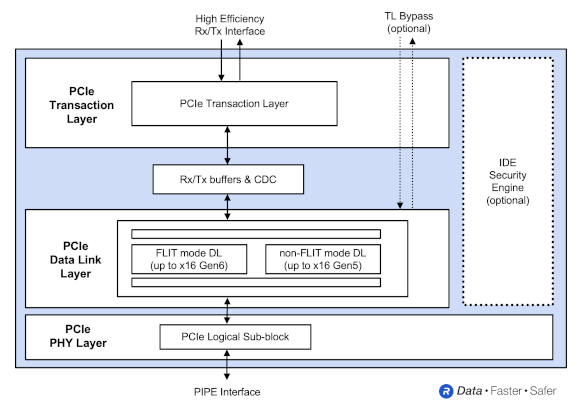

当市场准备就绪时,帮助客户整合最新的 PCIe 迭代是Rambus 宣布推出其 PCIe 6.0 控制器的动力,该控制器旨在满足快速推进的 AI/ML 和数据密集型工作负载的预期需求。它的 PCIe 6.0 控制器还提供安全功能,包括监控和保护 PCIe 链路免受物理攻击的完整性和数据加密 (IDE) 引擎。

Rambus 的 IP 内核总经理 Matt Jones 表示,控制器开发的关键考虑因素之一是 PCIe 6.0 和 CXL 3.0 将共享相同的电气接口。这是因为延迟成为 PCIe 和 CXL 数据平面连接的关键。

“我们已经做了一些非常聪明的事情,基本上使它成为添加我们的 IDE 的零延迟命中,”Jones 说。Rambus 利用了 Flit 功能,例如,允许控制器中的逻辑得到更优化。

准备好支持几个月甚至几年都不会采用的技术对于 Rambus 来说并不少见。高带宽内存 (HBM) 3 规范才刚刚正式推出,但该公司已经通过其HBM 3-ready 内存接口帮助其客户准备好设计,这些设计可能要再过 18 个月才会出现在产品中,该接口由一个完全集成的物理层和数字内存控制器。

支持 PCIe 6.0 的 Rambus 解决方案(来源:Rambus)

已经宣布 PCIe 6.0 解决方案的其他公司包括 Tektronix,它声称这是业界第一个与 PCI Express 6.0 兼容的基站发射机测试解决方案。与此同时,PCIe 6.0 的采用还有一点路要走,因为 PCIe 4.0 才刚刚获得广泛的关注。例如,美光科技最新的 SSD 使用 PCIe 4.0及其 176 层 3D NAND。

审核编辑 黄昊宇

-

AI

+关注

关注

91文章

41326浏览量

302731 -

PCIe

+关注

关注

16文章

1483浏览量

88979

发布评论请先 登录

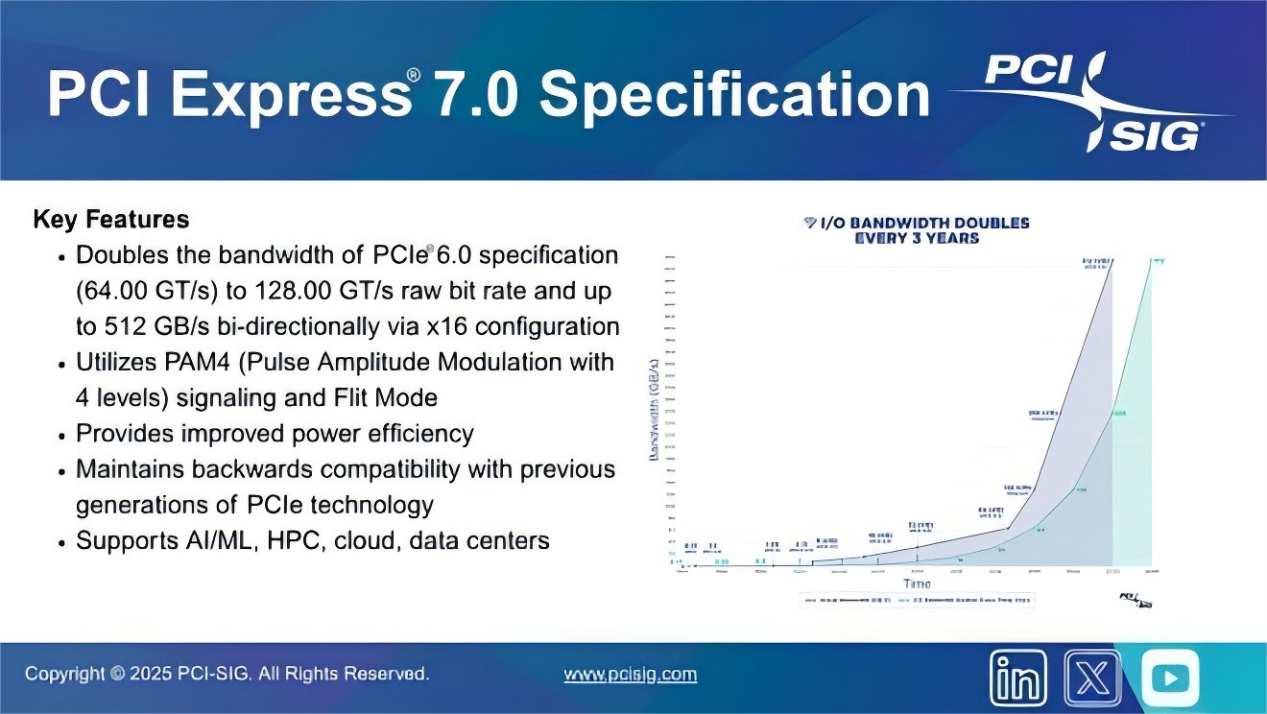

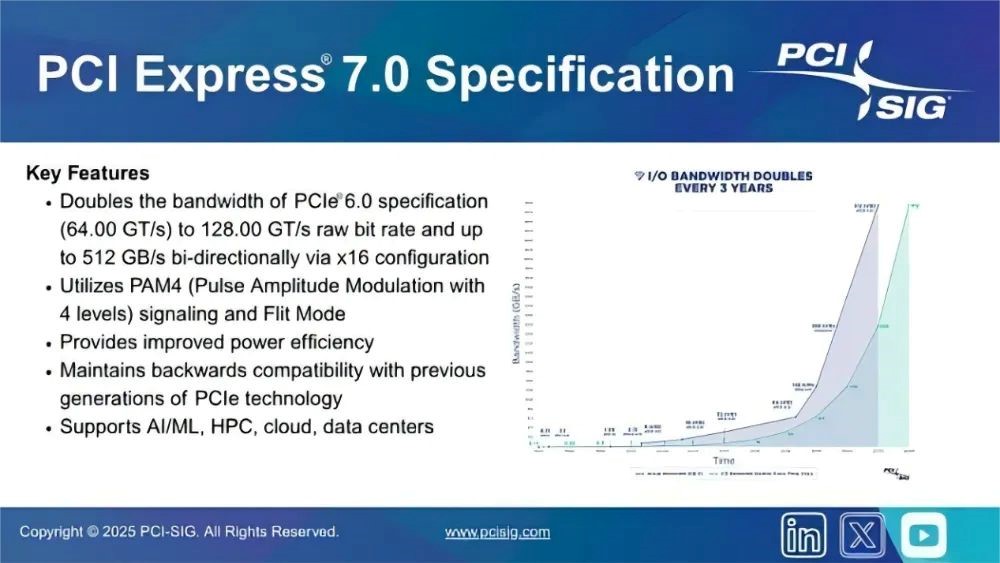

PCIe 7.0发布:16通道双向512GB/s,拥抱光纤未来

君鉴科技|PCIe 6.0 测试全套方案:从研发到量产,一站搞定

【PCIe 6.0 连载 · 下篇】测试才是关键:PCIe 6.0 如何保证稳定量产?(行业干货)

【PCIe 6.0 连载 · 中篇】从设计到实现:高速信号如何做到又快又稳?

【PCIe 6.0 连载 · 上篇】64GT/s 时代来临:AI与算力爆发下的高速互联新基石

PCIe协议分析仪的核心功能与工作原理

PCIe-8052 双口万兆光纤图像采集卡:万兆传输赋能,解锁工业采集新速度

采用 QFN 封装的 0.6 至 6.0 GHz 4xSPST 分流 MIPI 天线调谐开关 skyworksinc

PCIe 6.0 SSD主控芯片狂飙!PCIe 7.0规范到来!

曙光存储超级隧道技术助力应对PCIe 6.0时代

PCIe协议分析仪能测试哪些设备?

PCIe 4.0/5.0仍是主流!三家SSD企业抢滩高性能存储市场,新品相继亮相

高级工作负载推动 PCIe 6.0 的采用

高级工作负载推动 PCIe 6.0 的采用

评论