影响板级屏蔽罩效能的几大因素

板级屏蔽罩(BLS)广泛应用于各种电子产品或系统中,在解决电磁兼容问题(如电磁干扰辐射、系统内部干扰、射频问题等)中发挥重要作用。随着终端客户的要求不断升级,对 BLS 的设计要求也日益提升。如今,客户需要更高的频段、更轻、更小巧,或较低高度的屏蔽材料等等。因此,工程师如何评估 BLS 产品的屏蔽效能 (SE) 就成为了关键。本文通过介绍实际模拟和测试汇总出影响板级屏蔽性能的几个关键因素。本文可在工程师设计或选择电磁干扰屏蔽解决方案过程中提供一定参考

孔径对屏蔽效能的影响

要设计出一个完全封闭的 BLS 是不现实的,设计师通常需要在 BLS 上开一些孔,以达到通风排气,或者进行信号收发,器件避让等目的。本文提供了一些典型的 BLS 设计模型,通过比较这些模型的屏蔽效能,我们可以从中得出一些有用的 BLS 屏蔽应用的设计原则。

孔径大小的影响

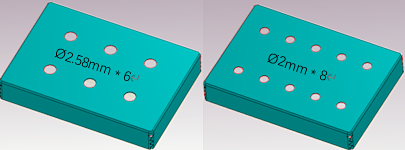

在大部分应用场景中,孔径均不超过 2mm,在电磁学领域,这与电磁干扰波长相比只是很小的长度(即电小尺寸)。因此,单孔不可能形成有效的天线。现在,假设我们需要在 BLS 盖板上开一列圆孔。以下哪种设计更适合用于电磁干扰屏蔽?(孔的总面积保持不变。)

通过对比电磁干扰模拟,莱尔德获得了两个设计模型的屏蔽效能数据。数据表明,孔越小,BLS 的屏蔽效能越好。 也就是说,孔尺寸对屏蔽效能的影响大于孔数量所产生的影响。

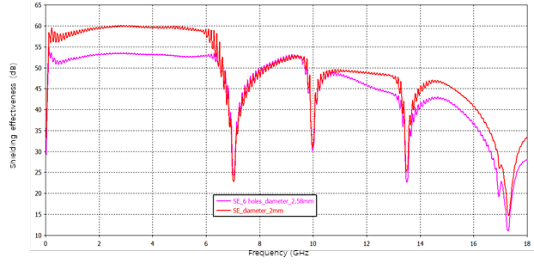

孔径/间隙结构的影响

在侧壁或 BLS 框架与盖板之间通常采用条状孔。对于两件式 BLS,由于装配的局限性,盖板和框架之间会有一定的间隙。这就形成了波导效应,会导致电磁干扰泄漏。所以我们应该考虑增加一些搭接点来阻断辐射路径,下面中的例子显示了不同设计带来的不同屏蔽效能。要注意,即使我们将间隙宽度保持在 0.01 mm,这个微小的孔隙仍然会导致屏蔽效能大幅下降。

有更多研究表明,孔径的长边尺寸对屏蔽效能起着决定性作用,而短边则几乎无此影响。因此,在实际应用中,工程师应避免采用长狭缝孔设计,即使空隙非常狭小。

材料对屏蔽效能的影响

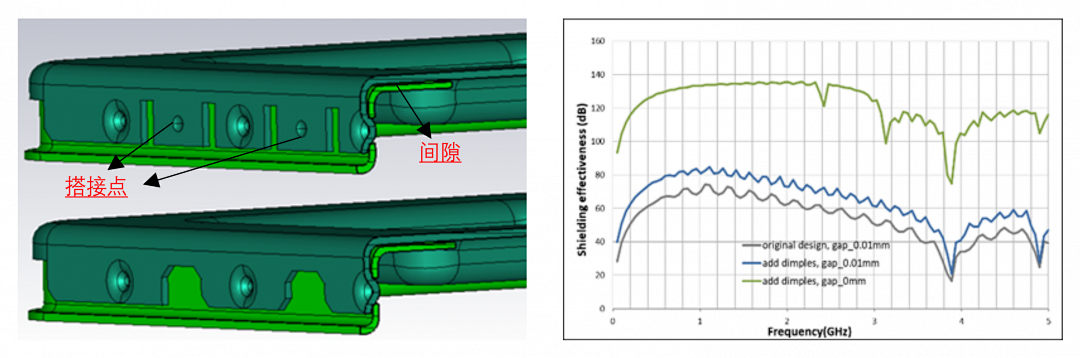

BLS 最常使用的材料是冷轧钢、不锈钢和洋白铜。这些材料的导电性均很高。鉴于此,在计算屏蔽效能时,我们可以忽略渗透率的影响。SE 的理论公式为:

SE ≈ R = 20 ·lg(η0/4η)

其中,η0是电磁干扰源的波阻抗,在平面波中此值为 377ohm;η是屏蔽材料的阻抗。为简单起见,其表达方式为:

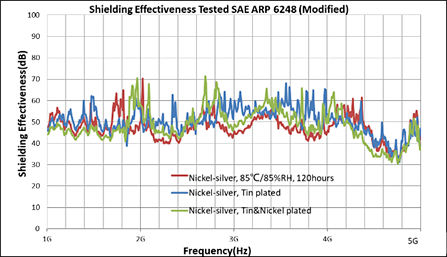

因此,材料的传导性 (σ) 是影响屏蔽效能的关键因素。要探明不同材料制成的 BLS 的屏蔽效能,一如往常,莱尔德进行了多次比较模拟和测试。这些实验表明,不同材料的屏蔽效能值基本相同。甚至在完成了高温高湿的老化测试后,屏蔽效能的结果也没有发生明显变化。

影响屏蔽的另一个重要因素是趋肤效应。这是指高频电流倾向于通过导体的外表面,而不是导体的内部。因此,如果电磁屏蔽结构采用了金属化电镀,那么屏蔽性能主要取决于此电镀材料;而基底材料则不是那么重要。

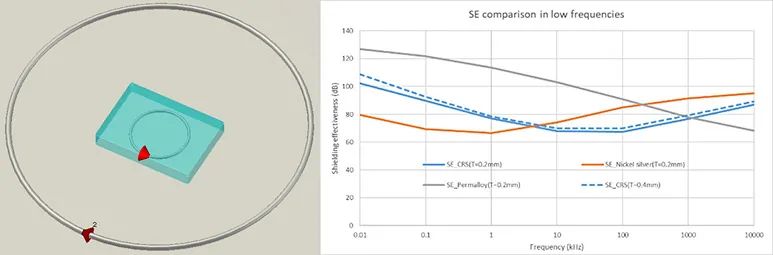

在低频率下,BLS 产品通常用于抑制通常由低阻抗源(例如,电感器、变压器)引起的磁场。在这种情况下,电磁干扰屏蔽机制会变得较为复杂。在准静态磁场中,磁通量将被诱导通过具有较高磁导率的材料。因此,屏蔽效能是由屏蔽结构材料厚度和磁导率决定。当频率升高时,涡电流引起的反射损耗将占主导因素。也就是说,材料的传导性成为影响屏蔽效能的关键因素。为了量化分析在低频下不同材料的屏蔽效能,我们建立了一个模型来计算 BLS 的屏蔽效能。我们在 BLS 的内部和外部放置两个线圈,并在 BLS 下方设置一个理想地平面。然后,我们通过测量有无 BLS 的情况下线圈的耦合量数据来计算其屏蔽效能,此时屏蔽效能SE可表示为:

SE(dB)=S21(无 BLS)- S21(有 BLS)

| 材料 | 电导率 | 相对磁导率 |

| CRS(马口铁) | 6*106(S/m) | 100 |

| 洋白铜 | 3.57*106(S/m) | 1 |

| 坡莫合金 | 1*106(S/m) | 20000 |

下图显示了电磁仿真模型和结果。使用三种典型材料进行建模。电性能参数如上表所示。我们发现坡莫合金在低于 100kHz 的频率下表现最好。CRS 材料也适合用于低频应用,高于100k Hz 时,镍银成为最佳屏蔽材料。此外,如果将材料厚度增加一倍,我们可以看到,屏蔽效能也会随之提升。

* 注意,我们在模拟中设置的磁导率是一个常数,在现实中,金属材料的磁导率会随着频率的增加而急剧下降。

其他因素(EMI干扰源、接地方式等)

本质上,电磁干扰屏蔽的目标是形成一个法拉第笼,将电磁场内外隔离开来。但 BLS 只提供了五个屏蔽面,它需要与 PCB 形成接地连接,以形成一个完整的笼体。我们还需要考虑其他可能会影响整体屏蔽性能的因素。以下是对我们研究结果的讨论。

EMI干扰源

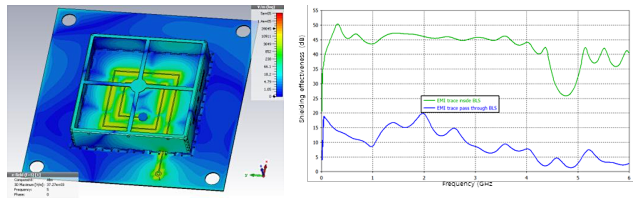

首先,我们注意到EMI干扰源(天线)的阻抗对屏蔽效能的影响微乎其微。通常情况下,高阻抗天线(如偶极子天线)会带来更高的屏蔽效能或动态范围,但我们无法给出一个量化的数据,因为不同的天线结构本身会产生不同的影响结果。另一个需要重视的因素是屏蔽体和干扰源之间的距离。如果干扰源位于泄漏点附近,那么显然会导致屏蔽效能减弱。这里有一个极端情况的示例。当有信号线穿过 BLS 的孔径时,电磁干扰泄漏就会变得非常严重。

下图显示了信号轨迹穿过 BLS 的城堡状槽口时电磁场的分布情况。如果我们进行比较试验,就会发现,两种场景下(电磁干扰源在 BLS 内部以及穿过 BLS 时)的屏蔽效能截然不同。

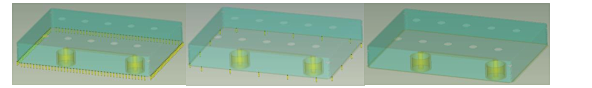

BLS 接地

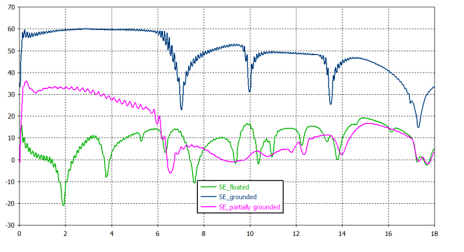

大多数 BLS 是通过贴片安装方式焊接到 PCB 上。在某些情况下,也需要穿孔组装。这实际上是形成了源于 BLS 的部分对板接地。接地孔的数量也可能影响屏蔽质量。因此,莱尔德完成了对三种接地方法的模拟研究。这些方法包括完全接地(通孔间隙_0.8mm)、部分接地(通孔间隙_7mm)和浮动式(无接地通孔)。下图显示了三种不同接地方式的模型。

显然,完全接地时的屏蔽效能最好。其次是部分接地。浮地的效果最低。此外,当 BLS 用浮地方式装配在 PCB 时,寄生电容起着重要的屏蔽作用。我们发现,腔体的谐振点发生了改变,在某些频率下时,屏蔽效能值可能是负值。

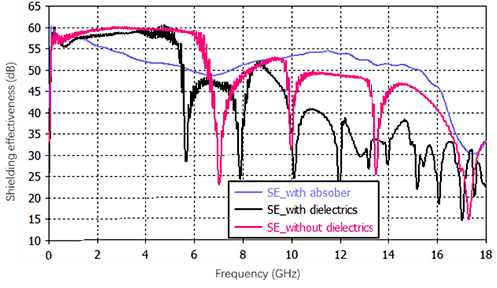

BLS 内部的介质材料

在之前的研究中,我们并没有考虑介质材料对屏蔽效能的影响。但是,在实际工程应用中,有许多电介质元件安装在 BLS 内(例如,PCB 材料、导热垫、电磁干扰吸波材料)。这些电介质将影响屏蔽效能,尤其是改变腔体的谐振频率点。一般而言,介质材料会压缩在其内部传播的电磁波的波长,这是因为它比空气或真空具有更高的介电常数 (ε=1)。介质材料内的波长(εr.)是

其中λ0 是真空下的波长。εr 是介质材料的介电常数。波长被压缩会导致屏蔽出现两种结果。其一,空腔谐振频率点将被转移到更低的频率。其二,随着波长越来越短,电磁波更有可能从孔中漏出。因此,屏蔽效能会减弱。如图所示,在 BLS 内部涂一层吸波材料会得到不同的结果。由于吸波材料附着在内部,BLS 成为一个损耗腔。谐振频点被全部消除。这就是 BLS 和波材料组合解决方案的一个典型应用,莱尔德通常将其称为多功能解决方案。

结 论

仅从结构来看,BLS 只是一块简单的金属壳体。但在电磁干扰屏蔽性能方面,仍然有许多因素可以决定实际的屏蔽效能。总而言之,BLS 的主要考虑因素是孔径/孔,而与材料的电导率和磁导率有关的因素并非主要因素,但在低频屏蔽应用时应考虑这类因素。在较高频率下,空腔谐振会大大削弱屏蔽效能。然而,目前已证明全波电磁干扰模拟在解决这些问题方面特别有用。结合使用吸波材料,可以有效抑制高频电磁干扰辐射。

审核编辑 :李倩

-

电磁干扰

+关注

关注

36文章

2506浏览量

108085 -

孔径

+关注

关注

0文章

11浏览量

11997 -

BLS

+关注

关注

0文章

7浏览量

17069

发布评论请先 登录

如何使用 powerquad 加速器中的一些功能以及 CMSIS 原始实现中的一些功能?

时钟缓冲器的一些主要应用领域介绍

爬壁机器人磁铁的一些常见问题

关于六类网线一些问题的解答

贴片电容精度J±5%的一些详细知识

对浮点指令扩展中一些问题的解决与分享

蜂鸟E203的浮点指令集F的一些实现细节

在Ubuntu20.04系统中训练神经网络模型的一些经验

Simulink模型测试典型问题分享——模型库管理问题

Siumulink模型测试典型问题分享——模型层级设计不合理

射频工程师需要知道的一些常见转接头

一些典型的BLS设计模型

一些典型的BLS设计模型

评论