我们所知道的第一个半导体路线图可能是摩尔观察到的,以他为名字的“摩尔定律”预计,芯片的计算能力随着时间的增长呈指数增长。这促使芯片制造商定期对芯片进行升级,而这些厂商的设备和材料供应商也需要了解未来的技术将如何发展,因此制定了国际半导体技术路线图(ITRS)半导体路线图。芯片制造商之间合作,并进行了对未来需求和挑战的预测,以提供对行业发展方向和需求的公开描述。

该路线图已演变为国际设备和系统路线图或IRDS路线图,与ITRS路线图的不同的是,它更多地是由上而下,而不是由下而上推导出来的。换句话说,它不是由芯片制造商的需求驱动的,而是通过预测未来器件性能的进展,然后确定什么类型的器件和结构可以提供未来所需的性能,其中包括了很多部分。本文重点介绍了2021年更新的光刻路线图中的光刻部分。

有关芯片光刻路线图的一些知识

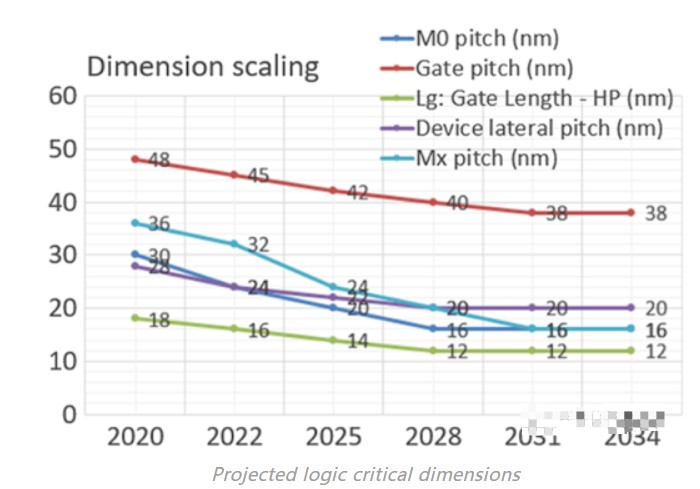

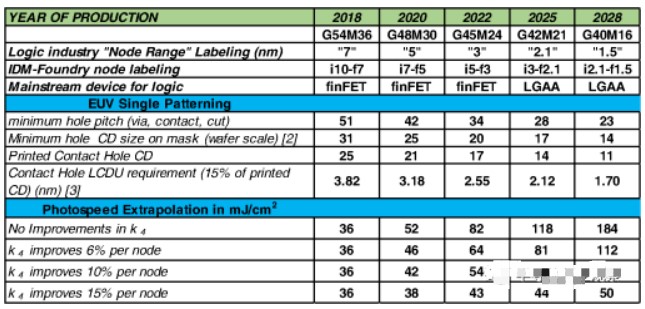

IRDS路线图中More Moore部分预测了传统逻辑和存储芯片的改进。这部分升级是由大数据、物联网、云计算和性能改进的一般需求驱动的。据预测,高性能逻辑器件将推动分辨率提高,而动态随机存取存储器(DRAM)器件的分辨率将落后于逻辑器件。非易失性存储器已经主要转向3D堆叠,将不会提高分辨率。关键逻辑节点的相关数据如图所示。在接下来的10年里,尺寸会变得更小,然后随着逻辑切换到3D堆叠,预计尺寸将停止缩小。

Projected logic critical dimensions

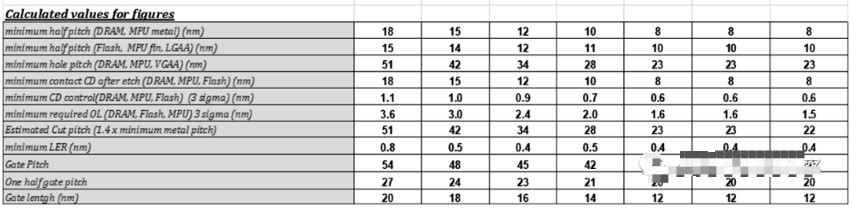

图2显示了2021年光刻路线图中逻辑和DRAM预测的光刻需求。注意,节点的名称用引号括起来,因为节点名称不再代表任何逻辑产品中的实际物理维度。

逻辑和DRAM的投影光刻要求。

白色的单元格表示存在可制造解决方案来满足这一要求,并正在进行优化,黄色的单元格表示已知可制造解决方案,可以实施,红色的单元格表示未知可制造解决方案。

历史上,光刻路线图关注的一个关键挑战就是分辨率,预计未来几代芯片需要比目前光刻系统更好的分辨率。现在情况已经不同了,如果使用双重图案化,则已经通过在制造中使用的EUV系统来解决路线图上的最小线和空间尺寸。对于接触孔(contact holes)和其他孔类型水平(hole type levels),使用当前工具的双重曝光可以解决直到2025年的“1.5 nm”所需的最小间距问题。“1.5 nm”节点将可以使用当时预计的High NA EUV工具进行双重曝光。在此之后,预计不需要进一步的分辨率改进。

包含分辨率数据的单元是黄色的,“可制造的解决方案是已知的”,其中使用EUV的双重图案化已经可以产生这种尺寸。在没有High NA EUV的情况下,EUV双重图案化是无法满足的,或者在光刻委员会认为双重图案化的图案质量有问题的情况下,单元被编码为红色,“可制造的解决方案是未知的”。

未来10年光刻技术面临的主要挑战主要与噪声和缺陷有关,Overlay预计也将是一个挑战。

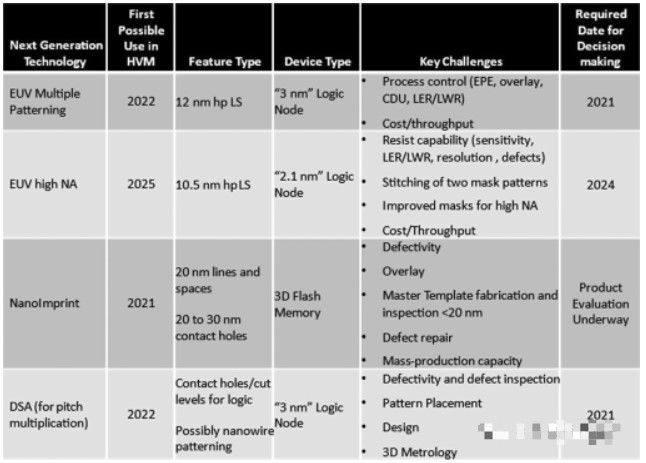

光刻路线图的一部分是对未来挑战潜在解决方案的描述。

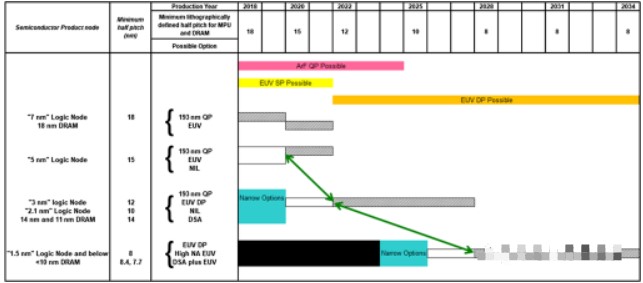

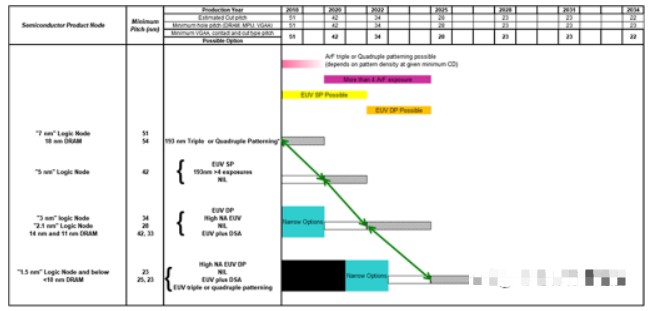

图3和图4分别显示了线和间隔以及接触孔。在这些图形中,水平方向是时间,也是需要图案的最小CD。这些行反映了不同逻辑和存储芯片的节点。灰色条表示节点预计何时投入生产。白色条形表示已选择并正在实施的模式选项,但尚未投入生产的时间段。在这种实现之前的时间段内,芯片生产商必须从有限的可能性集合中选择要使用的模式选项,这被称为“窄选项”。

Line and space potential solutions.

Contact hole potential solutions

对于线和间隔,EUV双图案可以为任何未来预计的临界尺寸提供足够的分辨率,虽然最终可能不是首选的解决方案。对于接触孔和其他孔型图案,NA=0.33的EUV双图案可能不能提供足够的分辨率,需要新的解决方案,High NA和EUV双图案是一个潜在的解决方案。

随机性(Stochastics)指的是成像过程中组件的随机变化,可以认为是噪声。成像中的噪声有多种来源,其中最主要的是由于光子噪声引起的空间图像的随机变化,以及由于构成光刻胶的化学成分的数量和位置的随机性而引起的化学变化。

在EUV中,二次电子的产生和传播也存在噪声,而二次电子驱动了EUV光刻胶中的辐射化学。这些噪声因素通过影响线边缘粗糙度(LER:line edge roughness )、线宽度粗糙度(LWR:line width roughness )和临界尺寸均匀性(CDU:critical dimension uniformity )来影响图案质量。

在EUV中,噪声也会导致某些类型的缺陷,如missing contacts 、line opens 以及 bridges。LER、LWR和CDU的要求随着分辨率的变化而变化,因此当尺寸变小时,这些要求就会变得更严格。

随机变化与临界维度的缩放方式不同,因此它们的显著性随着临界维度的减小而增,这是一个光刻界一直在努力解决的矛盾。EUV的出现带来了噪声问题。对于给定的曝光能量(以单位面积能量衡量),不仅光子少14倍,而且印刷特征尺寸大约比ARF浸没小两倍或更多倍,导致对所有噪声源更敏感,噪声限制了EUV可以打印的最小特征尺寸。

噪声的一个控制因素是光刻胶的”印刷“剂量。较慢的光刻胶往往比较快的光刻胶显示出更少的噪声,但光刻胶越慢,EUV曝光通量越差。EUV曝光工具的成本远远超过一亿美元,因此这些工具的高效使用和快速吞吐量非常重要。如果未来对低噪声成像的需求迫使使用慢速EUV光刻胶,这可能会影响半导体产业沿着IRDS路线图发展的进展。对于2020年IRDS路线图,光刻团队进行了缩放计算,以预测作为关键尺寸函数的预期打印剂量。

我们对于噪声问题的代理(proxy)是接触孔印刷的预期CDU。光子统计量(photon statistics)、电子统计量(electron statistics)或接触小孔的化学变化(chemical variation)应该直接转化为CD变化。

我们计算的起点是“7nm”逻辑节点,对于某些关键级别,该节点正在使用EUV进行批量生产。我们假设生产该节点的晶圆厂使用最快的EUV光刻胶,仍然给出可接受的缺陷和噪声水平。路线图显示了每个节点所需的最小接触孔尺寸和最小目标CDU。我们将使用CDU规格用于印刷CD 15%的接触孔,对于3.82nm的7nm接触孔尺寸来说,这给出了预期的3σ变化。较小的CDU将需要相应较小的CDU,在其他条件相同的情况下,将强制使用较慢的光刻胶。假设使用类似的单次曝光光刻胶工艺来印刷所讨论的所有CD,通过计算必须改变多少光刻胶的光刻速度才能提供这种较低的CDU,我们可以预测未来所需的光刻速度。

可以认为CD变化主要来自两个来源:曝光中光子的散粒噪声(shot noise)和光刻胶中发生的所有化学和电子相关过程的变化。散粒噪声将与要打印的剂量的平方根成比例。如果所有的CDU变化仅来自于该因素,则每次目标CD收缩30%时,印刷剂量将必须加倍,才能让接触孔CD变化对新节点和旧节点的比例相同。

另一方面,如果所有的CDU都是由随机光刻胶(random resist)工艺引起的,则光刻胶必须在每个节点上提高20%到30%,才能将CDU降低到目标水平。这两种限制情况都不现实,因为已知光刻胶特征尺寸变化来自这两个来源。最好的办法就是将每个变化源(source of variation)的影响分开,分别预测每个变化源的改进,并将各个变化元分别组合起来,以预测整体的光速变化。然而,我们无法找到适合此任务的令人满意的噪声源分类,因此我们使用了不同的方法。

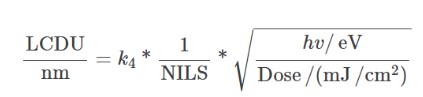

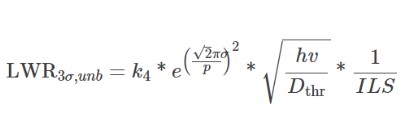

这个K4局部临界尺寸均匀性(LCDU:local critical dimension uniformity)的方程于2019年由GEH引入,它将LCDU计算为通过normalized image log slope(NILS)测量的空间图像质量、打印剂量、用于成像的光子能量和无量纲因子的函数。K4:

这个K4因子以与瑞利相同的方式测量用于使接触孔成像的工艺和光刻胶的质量K1因子表征给定光刻胶和工艺的分辨率。光子能量由用于所讨论的工艺的波长设置,因此对于我们的目的,它是一个常数,因为EUV光刻假设用于所有曝光。NILS受曝光工具因素(如NA、像差(aberrations)和光斑(flare))、使用的照明条件、特征尺寸和掩模效应的影响。我们选择预测NILS从节点到节点大致恒定,值为2.5。这等同于假设曝光工具、掩模版、工艺和设计改进将以足以补偿由于较小的特征尺寸,而导致NILS损失速率额(at a rate sufficient to compensate)发生,并且意味着从节点到节点成像的显著改进。

如下文所述,我们使用这些假设来预测用于印刷临界尺寸的EUV光刻胶的未来印刷剂量。我们在2020年的SPIE微光刻会议上介绍了这项工作。在同一次会议上,对K4介绍了配方。在修订后的公式中,有一个新的术语[e(√2πσ/P)2]如下面的等式所示,添加了包含光刻胶的blur(σ)和 pitch(P)为LWR测量的特征。

这个新等式调整了K4观察到光刻胶是图案间距的函数。

这个新的因素“模糊间距“(blur pitch)是必要的,因为resist blur影响光刻胶中图像的有效NILS。在原来那个K4等式,相同的光刻胶以不同的节距印刷将给出不同的K4数值。利用修正后的方程,K4通过间距(pitch)是恒定的。

然而,在我们对印刷的EUV剂量的预测中,隐含的是,不同的光刻胶将用于每个节点和每个临界尺寸,并且还隐含了,光刻胶将针对被印刷的特定尺寸进行优化。当临界尺寸缩小时,最佳resist blur也将缩小。用于反应扩散的最佳resist blur被报告为半节距CD的35%,这意味着用于每个CD的优化光刻机将具有恒定的比率σ向P。按比例减少blur并不是微不足道的,诸如二次电子blur的因素必须与诸如acid diffusion等传统因素一起解决。

从历史上看,光刻胶开发人员已经根据需要减少了Blur,我们假设他们未来将继续这样做,虽然这并不是必然的,前面的等式中的blur间距因子将是常数。原来的K4,假设resist blur对于每个连续的临界尺寸被优化,等式表现出了用于外推到印刷剂量的适当缩放。注意,该方法假设由于随机效应导致的CD控制的损失是选择光刻胶的限制因素。但是随机效应也会产生不想要的缺陷,例如缺失或合并的接触孔。据报道,这类缺陷比简单地使用其平均值和标准偏差来推断CD分布更常见。了解这类缺陷形成对光刻速度和良率的影响是下一个路线图的工作。

估计未来多久K4能够得到改善,我们转向历史数据抵抗改善。2002年,Dammel17回顾了历史上的光刻胶分辨率改进,并将这些改进转化为等效K1改进。他发现I线和KrF光刻胶的分辨率每年都有一致的改善,并且改善率相似。假设逻辑节点间隔2年,每年的分辨率改进转化为每个逻辑节点6%的改进。

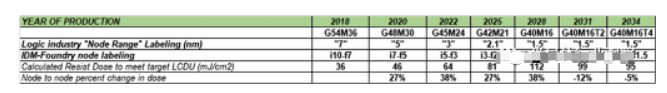

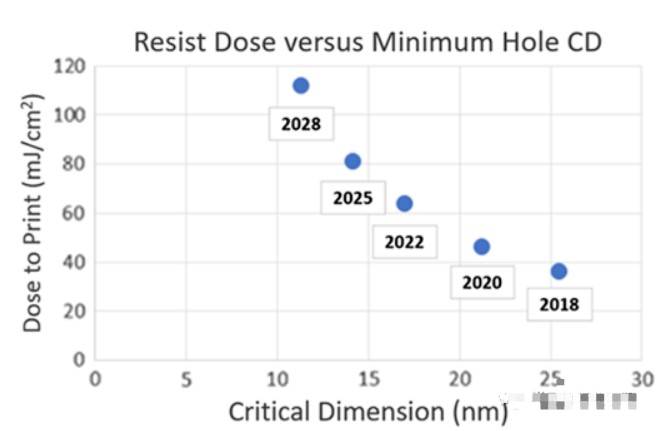

对给定光刻胶改进的预测,我们对恒定NILS的预测以及路线图对LCDU的要求,然后可以计算将使K4方程工作。插入NILs的值,K4,和7nm节点,LCDU目标到公式中K4给出打印的标称剂量36mj/cm2对于7nm临界尺寸的接触孔。使用6%的改进K4对于每个连续的未来节点,并且使用目标LCDU给出了要为每个未来节点打印的预计剂量。每个逻辑节点的计划打印剂量如图所示。以及与前一节点相比,打印每个节点的剂量增加的百分比。每个逻辑节点的计划打印剂量如图所示。以及与前一节点相比,打印每个节点的剂量增加的百分比,结果如图所示。请注意,预计印刷剂量在2031年开始下降,因为逻辑切换到3D堆叠,关键尺寸不再缩小,但预计光刻胶将继续改善。

EUV dose to print roadmap

EUV dose to print versus critical dimension.

打印的剂量预计将上升到100mj/cm2,该预测与最近的EUV光刻胶化学的随机模拟一致。这些模拟包括electron blur,并且他们预测,除非印刷剂量结束,否则挂你科教成分因素的任何组合都不会导致GIA感冒了快哦阿婆在没有不可接受的缺陷水平的情况下,成像10nm线和间隔100mj/cm2。我们宏观尺度的匹配K4基于该文献详细的物理特性,可以确信每个节点6%的改进是可以实现的。

灵敏度分析表明,如果启动K4对于7nm逻辑节点假设的值或起始NILS值是变化的,则对于7nm节点图案的印刷剂量将变化,但是从节点到节点的印刷剂量的百分比增加将是相同的。然而,印刷剂量的增加速率对光刻胶的改善灵敏度,如通过K4.图7显示了不同改善率的预期打印剂量与节点的函数关系。

Increase in dose to print for different rates ofk4k4improvement.

如果光刻胶随机性不随光刻胶优化而改善,那么印刷的光刻胶剂量将在5个节点上增加五倍。如果光刻胶随机性改善这么多K4,每个节点都能提高15%,在相同的五个节点上,打印剂量增加不到50%。考虑到这种对光刻胶随机改进速率的巨大依赖性,未来或许可能使改进慢于或快于公布的路线图,估计每个节点提升6%的因素是有用的。

在已发表的关于EUV光刻胶改进的研究中,一些研究显示每年的改进非常小。(参考文献显示新光刻胶落在与旧光刻胶相同的LER感光速度曲线上)。新光刻胶沿着印刷剂量和线粗糙度之间的现有平衡下降。但是最近的一些论文已经显示了用于特定应用或特定成像条件的光刻胶有了很大的改进。这种二分法的一部分可能是因为在当前使用的两类EUV光刻胶中,存在大部分或全部使用有机化学的化学放大光刻胶,并且大部分使用金属氧化物作为关键EUV成像组分的无机光刻胶。

化学放大系统的工作原理在应用于KrF和ARF成像时已得到很好的确立,基于已经为ARF应用中随机性优化的成熟机制,很难期望光刻胶可以得到快速改进。有些人可能会争辩说,噪声的来源是众所周知的,并且可以实现的LWR、LER或CDU有一个下限。

无机光刻胶是一类新的光刻胶,不限制于以前的波长,因此可以预期,它们将比EUV化学放大光刻胶改进得更快,用于EUV的基于金属的光刻胶在性能上已经与传统的化学放大光刻胶相匹配。然而,无机光刻胶仅在 negative tone中可用,在某些应用中比基于有机的化学放大光刻胶具有优势。

这里描述的方法是高层次的,并不考虑如何进行实际改进的细节。例如,它不考虑光刻胶中的具体问题,比如电子模糊或竞争EUV引起的反应;也不考虑替代工艺,比如,能让低EUV剂量打印成为可能的缺陷DSA修复。这是基于我们对过去技术进步的理解而做出的推断,它显示了存在哪些挑战,但没有给出解决这些挑战的解决方案。从历史上看,这个行业过去在创新和增量改进方面都遇到了困难的挑战,整个光刻委员会都希望这种情况在未来继续发生。

IRDS认为在K4上6%的改善也将代表光刻胶改进的相当大的速率。但是,最终这个6%的数值是一个专家委员会对未来的预测,而不是一个通过实验确定的数字。

由于吞吐量的减少,以及曝光工具成本的增加,预计印刷剂量的增加将给EUV用户带来很大的成本。一种替代方案是使用EUV双重曝光,这将增加光刻成本,但由于光刻胶中较大的印刷尺寸而提供改进的随机性。比较EUV应用的单次曝光和两次曝光的研究已经在进行中。

另一种策略是接受不良的随机因素,但找到提高图案质量的工艺替代方案。双重图案化是一种这样的工艺,定向自组装也显示出能够使用快得多的光刻胶的潜力。(一篇由G. Singh, E. Han和F. Gstrein在2020年SPIE微光刻大会上发表的论文“用DSA使摩尔定律生效”。遗憾的是,没有会议记录文件。2021年,参考文献提交了一份后续论文。)。或许能对流程改进有所帮助。工艺改进的一个例子,就是印刷比所需更大的通孔以获得更少的CDU,然后通过蚀刻或一些其他工艺来缩小它们,还可能出现新的光刻胶类型和工艺。最近报道了关于干沉积和显影光刻胶的工作,但是没有足够的公开数据来比较它们与当前材料的随机性。

除了与噪声相关的模式质量之外,还有其他挑战。Edge placement error(EPE)是未来节点面临的主要挑战,对EPE的要求是最终特征尺寸的函数,并且EPE要求随着CD变小而缩小。放宽印刷CD要求的工艺,如双重图案,通常会使EPE变得更糟糕。随着印刷特征尺寸的减小,保持可接受的NILS将需要改进掩模、曝光工具和源掩模优化,以及可能的芯片设计变化,更容易成像。NA为0.55的,更高NA的EUV曝光工具预计将在2023年或2024年推出。与较低NA成像相比,这些较高NA工具将改善特定特征尺寸的NILS,这些工具将具有当前工具的一半曝光区域大小,并且对于某些产品设计可能需要区域缝合。它们将需要改进的掩模版。由于对聚焦敏感的EPE,曝光工具中较高的照明和成像角度可减小聚焦深度,并且还减小图像对比度,但这些挑战的解决方案尚未展示。

当前行业正在积极研究替代印刷技术,如纳米压印、定向自组装和直接写入。纳米压印已经显示出实质性的最新进展,但没有展现出用于批量存储芯片生产的足够的生产率,也没有显示出足够低的缺陷水平来考虑用于前沿逻辑应用。它还需要在用于逻辑的覆盖方面进行改进,但定向自组装仍未在批量生产中得到证实。虽直接写入对于高容量芯片生产没有足够的吞吐量,但对于不需要前沿尺寸的低容量生产具有优势。最近的论文描述了正在开发的新的直接写入工具。

从长远来看,当逻辑开始垂直发展而不是缩小关键尺寸时,良率和工艺复杂性将成为关键挑战。路线图预测,3D逻辑将在2031年投入生产,但解决其挑战和开发此类设备必须比这早得多,2021年光刻困难挑战如图所示。

IRDS 2021 lithography difficult challenges.

IRD路线图预测,未来半导体面临的挑战以及应对这些挑战的可能解决方案。它表明,在未来大约10年内,逻辑器件将推动关键尺寸的缩小和图案化的改进。之后,逻辑将切换到垂直缩放。IRDS路线图的光刻部分解决了这些图案化挑战,包括投影图案要求和可能的图案选项。一个主要的挑战是成像中的噪声。随着印刷特征变得更小,对低缺陷和良好图案质量的要求将驱动EUV印刷剂量的增加。即使假设在光刻胶、工具和其他成像基础设施等方面有实质性的改进,打印的剂量也会超过100mj/cm2,预计将到2028年,才能没有实施减轻噪声影响的替代工艺或设计,这估计对预测的抵抗随机性的改善灵敏度。即使假设随机性被控制得,足够好能给出足够的LWR和CDU,其他因素,例如缺失或合并的特征,或者在减小的尺寸下不能可靠起作用,也可能是未来EUV使用的障碍。其他主要的挑战是改进EPE,以及高NA EUV成像的开发和实施。该行业正在积极寻求替代的图案化技术,特别是纳米压印光刻、定向自组装和直接写入。

从长远来看,随着半导体缩放改变为3D堆叠,良率和工艺复杂性将成为特定图案化的挑战。

审核编辑:刘清

-

芯片

+关注

关注

462文章

53535浏览量

459132 -

DRAM

+关注

关注

40文章

2373浏览量

188164

原文标题:芯片光刻路线图

文章出处:【微信号:半导体科技评论,微信公众号:半导体科技评论】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

俄罗斯亮剑:公布EUV光刻机路线图,挑战ASML霸主地位?

全球唯一?IBM更新量子计算路线图:2029年交付!

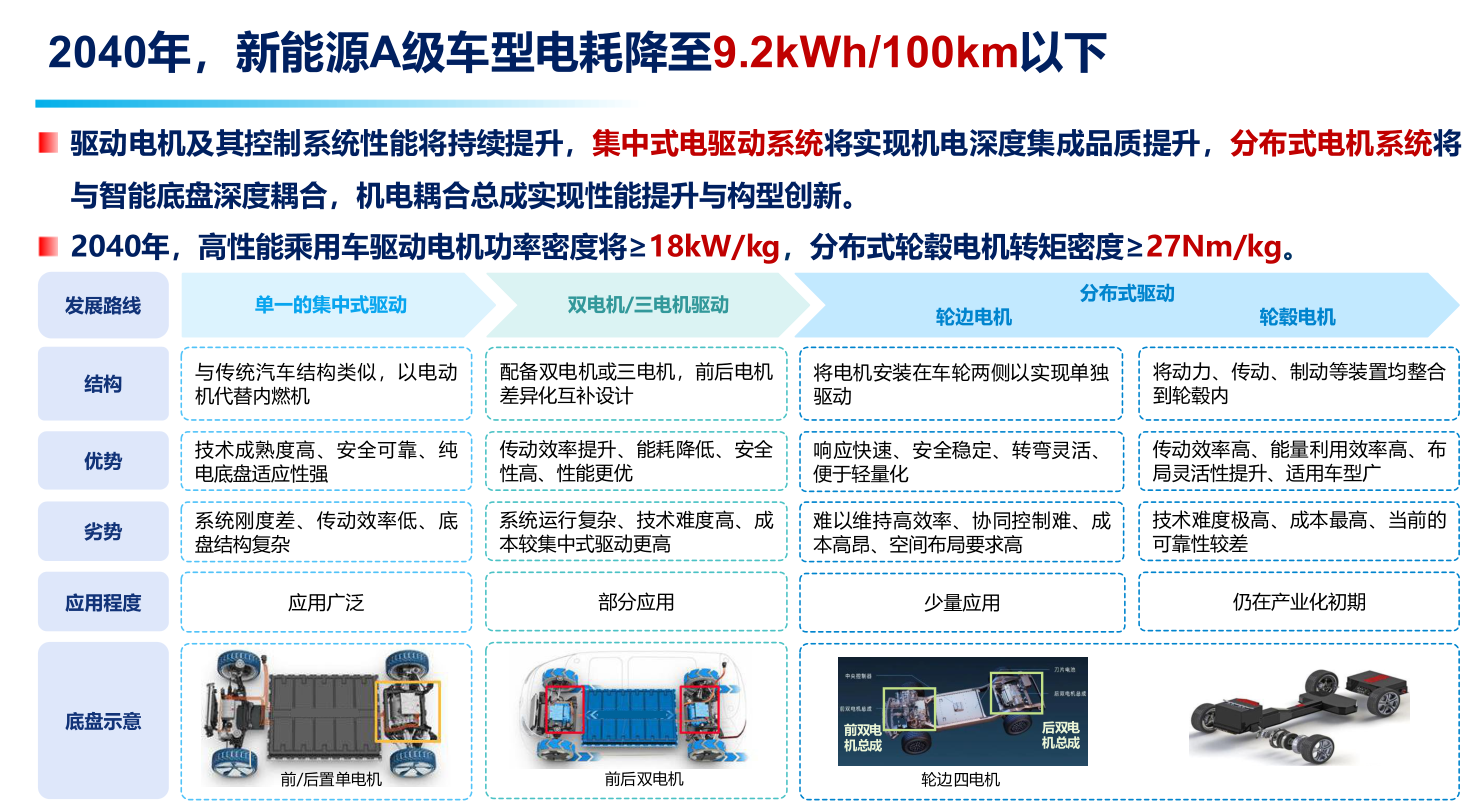

中国2040年汽车技术路线图发布!内燃机还能再战15年?

纳芯微参编节能与新能源汽车技术路线图3.0正式发布

分享一个驱动开发工程师学习路线图

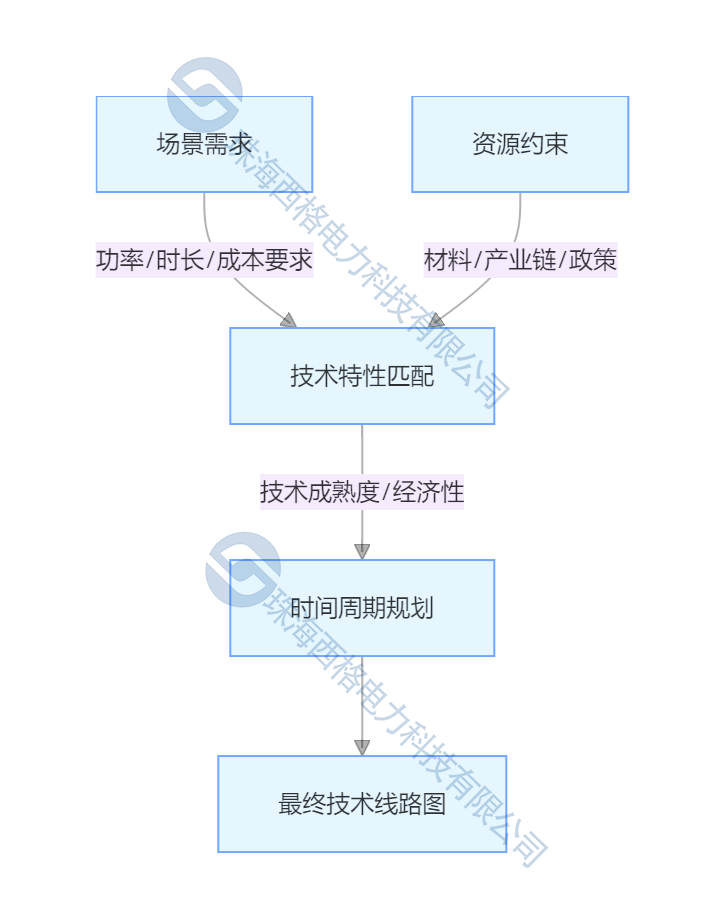

西格电力储能技术路线图的破局之道,实现从精准规划到高效落地

曦华科技参编节能与新能源汽车技术路线图3.0正式发布

储能战略规划:企业级储能技术路线图的制定方法与实践指南

四维图新参与编制两轮车智能化技术发展路线图

华为首次公布昇腾芯片新路线图

《AI芯片:科技探索与AGI愿景》—— 勾勒计算未来的战略罗盘

关于芯片设计的一些基本知识

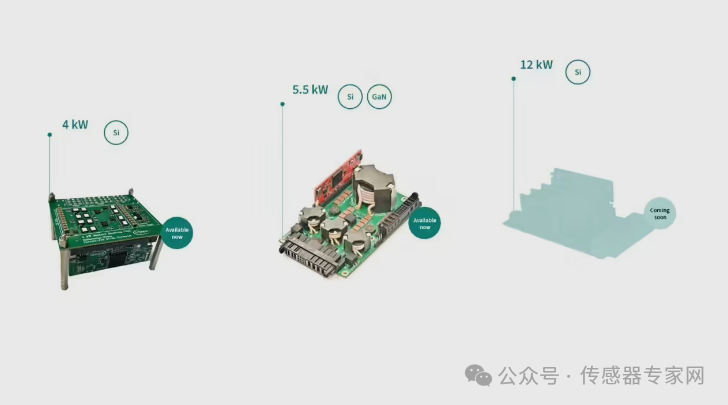

英飞凌公布AI数据中心电池备份单元BBU路线图,全球首款12kW系统在列

有关芯片光刻路线图的一些知识分享

有关芯片光刻路线图的一些知识分享

评论