1,reg与wire的区别:

相同点:

都能表示一种类型类型。

不同点:

wire

连线型数据,线网类型;

表示元件间的物理连线,不能保存数据;

线网是被驱动的,可以用连续赋值语句或把元件的输出连接到线网等方式进行驱动;

给线网提供驱动的赋值元件就是“驱动源”,线网的值由驱动源来决定;

如果线网没有连接到驱动源,线网的缺省值为“Z”。

reg:

寄存器型数据类型,通常用于对存储单元进行描述;

这种变量可以保持它们自身的数值,直到该变量被指定了新的值为止 ;在过程被赋值的变量必须定义为reg型;

只能存放无符号数;

有符号数寄存器变量:integer 。

2,$stop:

表示停止命令,常用格式为,位于initial语句中:

#时间(N) $stop;

表示在(N)个时间单位后,停止仿真。

3,参数声明parameter:

在程序中需要多次使用同一个数字时,可以考虑采用参数来提高代码的简洁度,降低代码的设计量。

参数一经声明,就视其为一个常量,在整个过程中值不在改变。

其定义方式如下:

《变量名》=《变量定义》;

例如:

parameter SET_TIME_1S=27‘b50_000_000;

//把常量50000000用标识符SET_TIME_1S来代替。

用同一个 parameter 同时定义多个参数时,各个参数之间用“ , ”来隔开。

使用参数可以提高代码的可读性,也便于修改。

4,仿真时的端口定义

与模块输入端口相连的信号端口是产生仿真信号的端口,需定义为reg类型;

与模块输出端口相连的信号端口是被输出信号所驱动的端口,需要定义为wire类型;

5,阻塞与非阻塞赋值语句

1,非阻塞赋值语句

用操作符“《=”来标识“非阻塞赋值语句”;

在begin-end串行语句中,一条非阻塞赋值语句的执行不会阻塞下一条语句额执行,也就是说,在本条非阻塞型过程赋值语句对应的赋值操作执行完之前,下一条语句也可以开始执行。

仿真过程在遇到非阻塞型过程赋值语句后,首先计算其右端赋值表达式的值,然后等到仿真时间结束时将该计算结果赋值变量。也就是说,这种情况下的赋值操作是在同一时刻上的其他普通操作结束后才得以执行。

2,阻塞赋值语句

用操作符“=”来标识“阻塞赋值语句”;

在begin-end串行语句中的各条阻塞型过程赋值语句将它们在顺序快中的排列次序依次得以执行。

阻塞型赋值过程赋值语句的执行过程:首先计算右端赋值表达式的值,然后立即将计算结果赋值给“=”左端的被赋值变量。

原文标题:verilog的一些技巧

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

-

Reg

+关注

关注

0文章

20浏览量

11792 -

端口

+关注

关注

4文章

1098浏览量

33828 -

代码

+关注

关注

30文章

4941浏览量

73136 -

Wire

+关注

关注

0文章

24浏览量

16232

原文标题:verilog的一些技巧

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

分享1-Wire接口数字温度传感器IC型号

如果在WL_REG_ON/BT_REG_ON为低时输入PCIe REFCLK,会有什么问题吗?

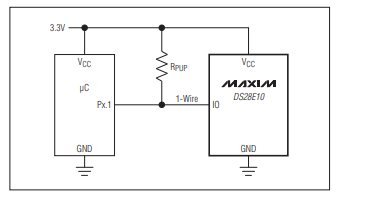

DS28E10 1-Wire SHA-1认证器技术手册

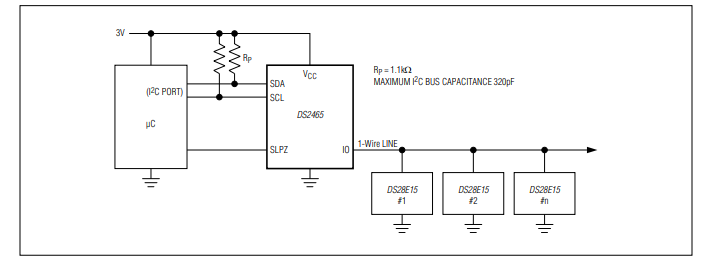

DS2465 DeepCover安全认证器具有SHA-256协处理器和1-Wire主机功能技术手册

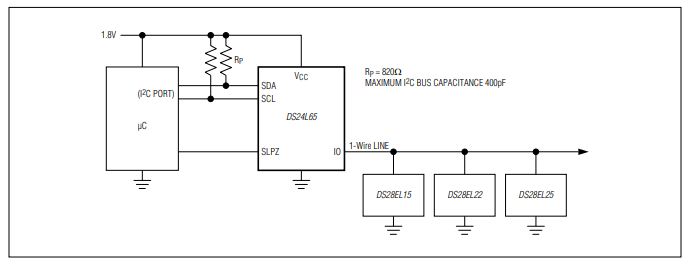

DS24L65 DeepCover安全认证器,具有SHA-256协处理器和1-Wire主机功能技术手册

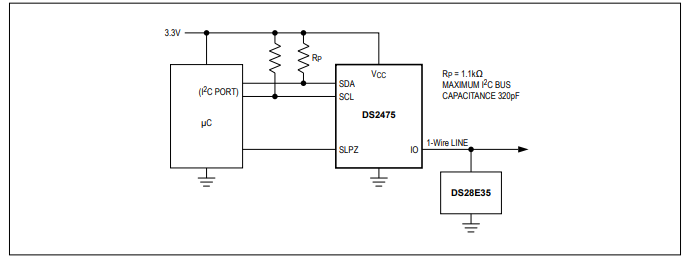

DS2475带1-Wire主机的DeepCover ECDSA协处理器技术手册

DS28E16 1-Wire SHA-3安全认证器技术手册

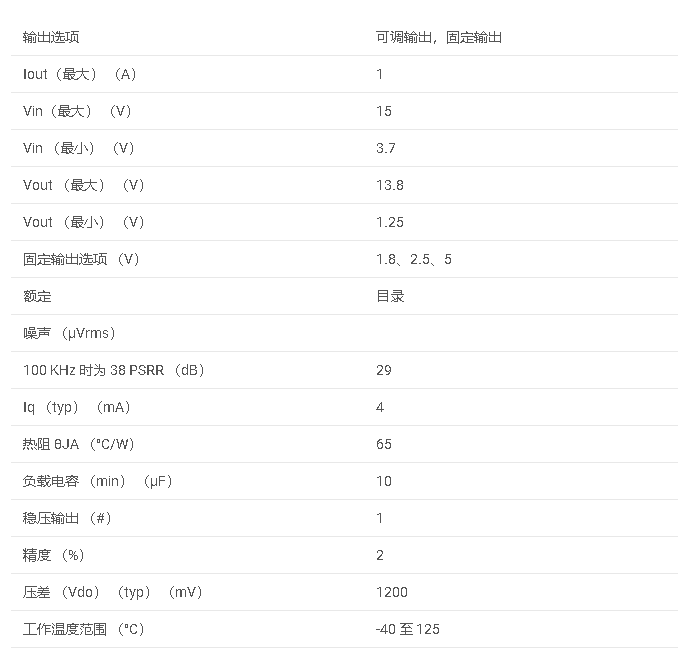

REG1117A 1A、15V、线性稳压器数据手册

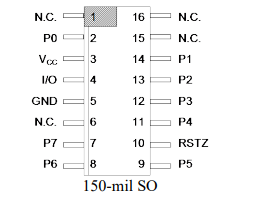

DS2408系列1-Wire、8通道、可编程 1-Wire IC技术手册

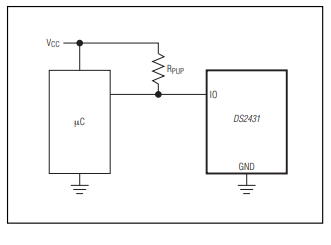

DS2431 1024位1-Wire EEPROM技术手册

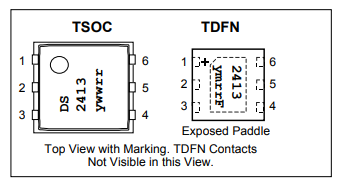

DS2413系列双通道可编程1-Wire芯片技术手册

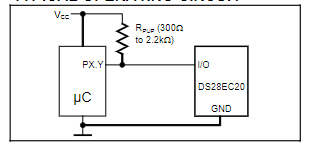

DS28EC20 20Kb 1-Wire EEPROM技术手册

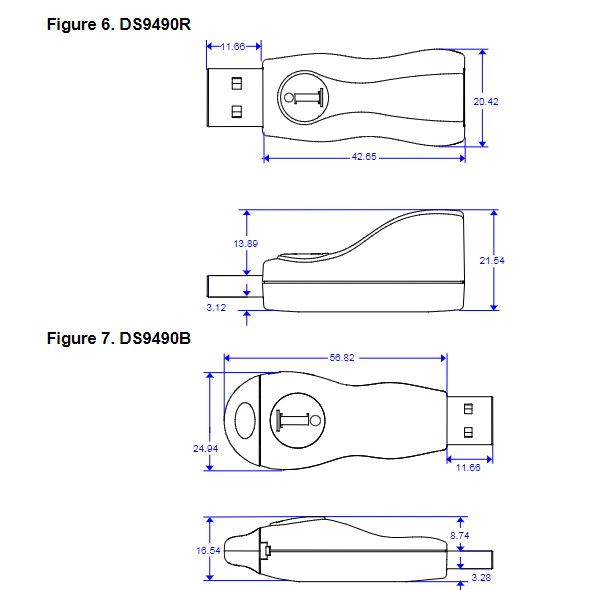

DS9490 USB至1-Wire/iButton适配器技术手册

reg与wire的区别

reg与wire的区别

评论