在许多电气和传感器应用中,SOI(绝缘体上硅)晶片已经取代了传统的硅晶片,SOI晶片具有不同的掩埋氧化物(BOX)和SOI层厚度,粘合界面的强度通常用裂纹张开法测量,然而,当一种或两种结合材料是易碎的,例如玻璃或薄晶片时,使用裂纹张开方法是相当困难的,在这些情况下,刀片的插入通常导致晶片之一的破裂,而不是裂纹的形成;另一个限制是刀片需要有插入的地方,例如两个圆形晶片之间的开口,因此表面能只能从靠近晶片边缘的区域测量,裂纹张开法在测量强键时也有问题,在这项工作中,我们华林科纳将提出粘接界面的高频蚀刻作为评估粘接强度的替代方法。

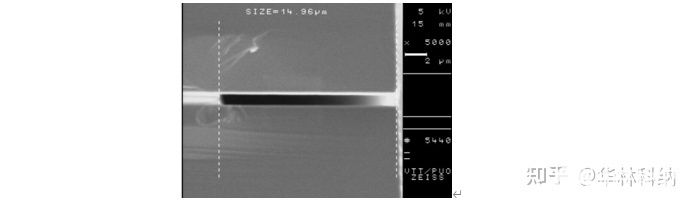

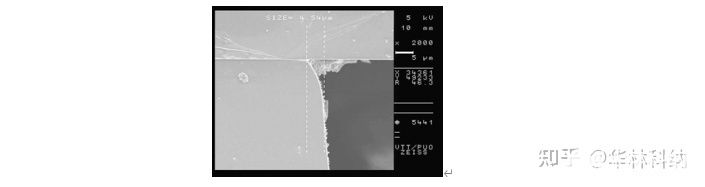

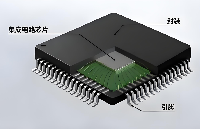

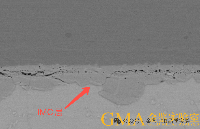

为了评估这种方法,我们创建了不同的键合界面(硅/氧化物、氧化物/氧化物、硅/玻璃、氧化物/玻璃),在100 ℃- 1100℃下对晶片对进行退火,为了进行蚀刻测试,使用划片机在键合晶片的表面上切割凹槽,随后样品在50% HF溶液中蚀刻10分钟,在SOI结构中,通过使用扫描电子显微镜(SEM)测量了从凹槽到氧化物壁的蚀刻距离(图1),在硅/玻璃结构中,测量了“肩部”的宽度(图2)。

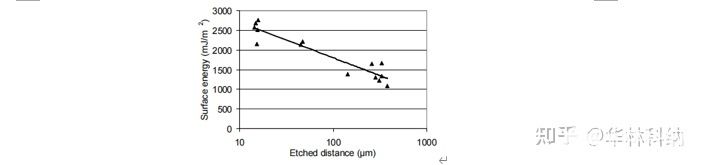

为了比较,用裂纹张开法测量了SOI样品的有效表面能,表面能和蚀刻距离之间的关系如图3所示,在所有测量的SOI结构中,键合界面处的蚀刻发生得比氧化物的其他部分更快,然而在强接合的情况下,蚀刻速率之间的差异相对较小(图1),在硅/玻璃键合中,发现“肩”的长度随着退火温度的升高而减小。

在本文中我们华林科纳证明了在裂纹张开法不适用的许多实际情况下,HF腐蚀试验可用于评估粘结强度。

审核编辑:符乾江

-

半导体

+关注

关注

339文章

31238浏览量

266562 -

蚀刻

+关注

关注

10文章

431浏览量

16687

发布评论请先 登录

中电科正式发布全自动高真空键合设备及TCB热压键合机两款先进封装核心装备

高频超声键合技术:引线键合工艺优化与质量检测方法

半导体封装引线键合技术:超声键合步骤、优势与推拉力测试标准

一文读懂引线键合可靠性:材料选型、失效风险与测试验证全解析

NTC热敏芯片键合工艺介绍

谁更有效?解码焊球剪切与键合点拉力测试的真实对比

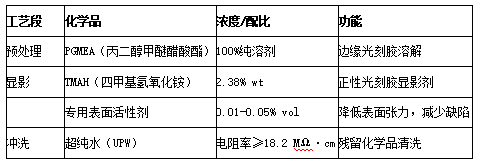

定义光刻精度标准——华林科纳显影湿法设备:纳米级图形化解决方案

IGBT 芯片平整度差,引发键合线与芯片连接部位应力集中,键合失效

芯片制造中的键合技术详解

什么是引线键合?芯片引线键合保护胶用什么比较好?

华林科纳通过HF蚀刻法表征键合界面

华林科纳通过HF蚀刻法表征键合界面

评论