共读好书

高晓义 陈益钢

(上海大学材料科学与工程学院 上海飞凯材料科技股份有限公司)

摘要:

在先进封装的铜种子层湿法蚀刻工艺中,电镀铜镀层的蚀刻存在各向异性的现象。研究结果表明,在磷酸、双氧水的蚀刻液体系中,因电偶腐蚀造成的凸点电镀铜蚀刻量约为铜种子层蚀刻量的 4.9 倍。通过分析凸点上锡、镍镀层的能谱数据及蚀刻效果,发现该凸点结构中的锡、镍镀层表面存在钝化层,导致锡、镍镀层的蚀刻量远低于铜镀层。在加入不同添加剂的蚀刻液中,通过络合铜或破坏锡、镍镀层表面钝化层的方法,均能达到抑制凸点上铜镀层发生电偶腐蚀的效果。其中,复合型添加剂可以使凸点上铜镀层的横向蚀刻量降低约 82%,并且添加剂无残留风险。

1 引言

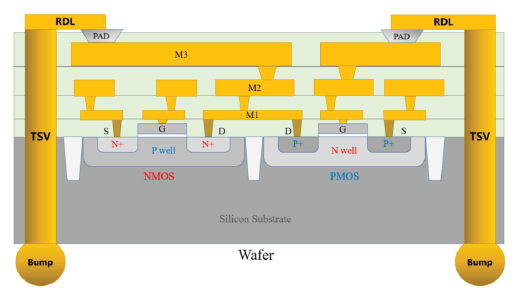

随着半导体产业的发展,先进封装技术被广泛应用于高性能消费电子产品。其中,晶圆级芯片尺寸封装能够通过制作扇入或扇出型铜再布线层(RDL)在晶圆表面排布更多的 I/O 端子,实现高密度、高集成度的互联。凸点技术是在 IC 表面制作 I/O 端子的关键 [1] 。

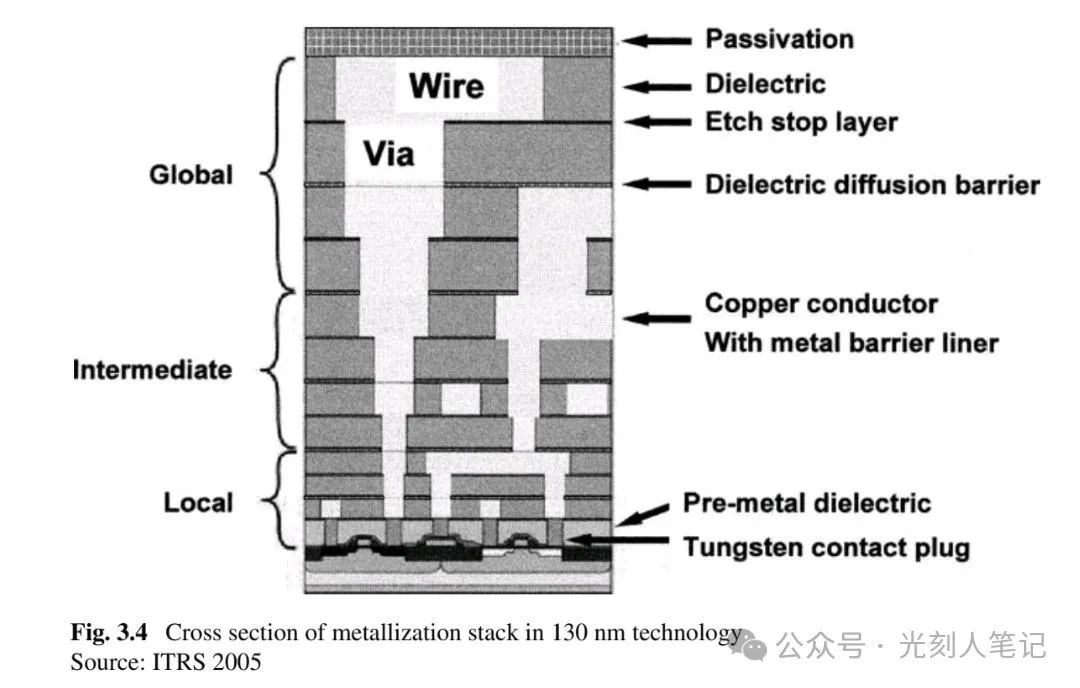

在凸点技术工艺中,铜蚀刻液会同时接触到凸点结构中的铜、镍、锡、银等多种金属镀层 [2] 。一般情况下,凸点结构中电镀铜的横向蚀刻速率要比溅镀(PVD)铜的纵向蚀刻速率快。针对金属蚀刻的各向异性问题,业界已经开展了一定的研究。邢攸美等人 [3] 对蚀刻液的化学组分进行了一系列的分析排查,并收集了改善各向异性蚀刻(指被蚀刻材料在横向与纵向的蚀刻速率之间存在巨大差异的蚀刻)的添加剂种类。刘瑞丰等人 [4] 尝试通过改变工艺条件来优化各向异性蚀刻的效果,并尝试通过整合铜、钛分步蚀刻工艺达到降低铜的横向蚀刻量的目的。陈波等人 [5] 通过研究蚀刻工艺与蚀刻设备条件,优化了蚀刻工艺过程中铜蚀刻的均匀性,从而减少了蚀刻时间,进而降低铜的横向蚀刻量。因此,针对电镀铜蚀刻的研究工作主要是通过改善生产工艺与蚀刻液的蚀刻效果,以降低铜的横向蚀刻量。

在铜蚀刻过程中,因为存在不同金属结构的堆叠,且蚀刻过程均裸露在蚀刻液中,所以凸点结构与蚀刻液将形成微型的原电池。这种微型的原电池将造成凸点结构中电镀铜镀层的加速蚀刻。电镀铜镀层的加速蚀刻将造成凸点结构中电镀铜镀层尺寸的急剧收缩,进而降低凸点结构在封装焊接中的可靠性。在铜蚀刻过程中,由于微型原电池的产生而造成的铜镀层加速蚀刻的腐蚀现象一般称为电偶腐蚀。该类研究很少聚焦多层异种金属堆叠情况下发生的电偶腐蚀。

KEAR 等人 [6] 通过表征铜在电化学腐蚀过程中的阴阳极状态,分析推导了在氯离子环境下的腐蚀电位特性,为研究多层金属中的电偶腐蚀提供了一定的借鉴和参考。在电偶腐蚀研究中,大多倾向于研究宏观结构的金属部件的接触腐蚀现象 [7-9] 。在半导体器件微

观结构的制作过程中也具备了产生电偶腐蚀的条件,但因为微观结构的尺寸过小,难以在凸点蚀刻研究中表征电偶腐蚀的影响。

本文旨在探讨在先进封装的铜蚀刻工艺中凸点结构的电镀铜镀层的电偶腐蚀过程,并分析其产生的原因,尝试通过遴选合适的蚀刻液添加剂,抑制电镀铜镀层的电偶腐蚀,以达到提升封装时凸点结构可靠性的目的。

2 实验材料与方法

2.1 实验材料

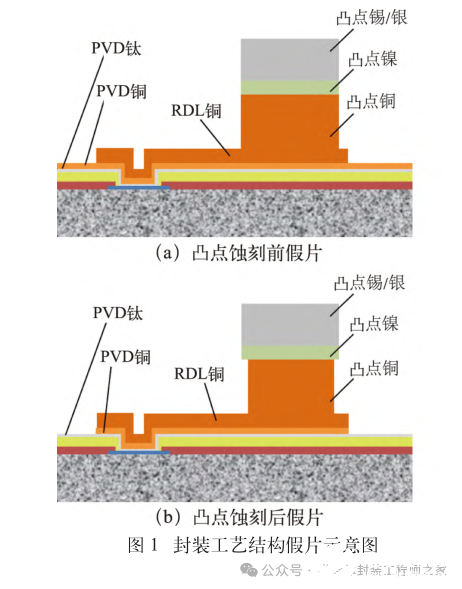

封装工艺结构假片包含:PVD 钛(厚度为 1000魡)、PVD 铜(厚度为 3 000 魡),以及图形化的铜线与凸点结构。图 1 为封装工艺结构假片示意图。

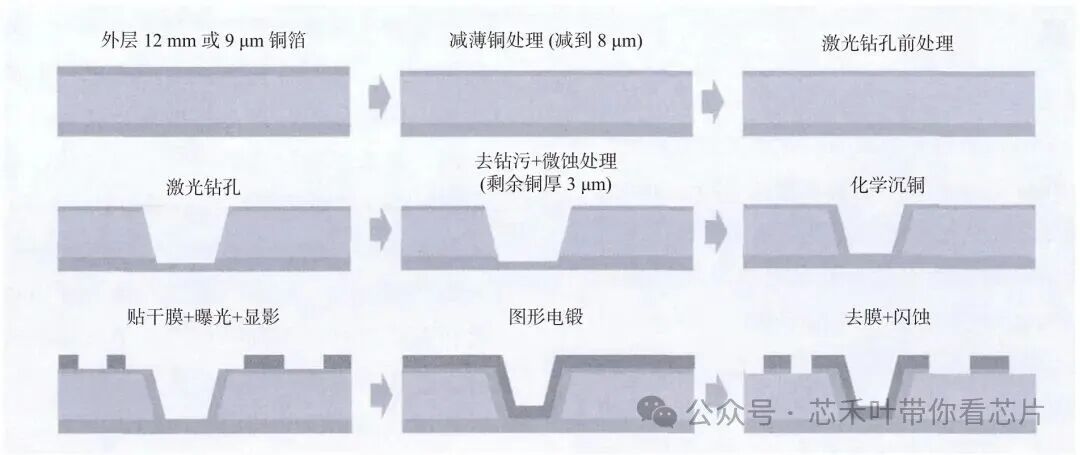

凸点结构的制作工艺流程:1)使用磁控溅射的方法在晶圆表面依次沉积金属钛、铜,为后续电镀线路与结构凸点提供导电的种子层;2)使用光刻胶对需要电镀沉积金属的位置进行图像化开口;3)依次进行铜、镍、锡 / 银合金等金属层的电镀(在进行锡 / 银合金的电镀时,银的质量分数一般控制在 2%左右);4)去除光刻胶,得到实验所需的晶圆。裁剪后,实验晶圆的尺寸为 2 cm×2 cm。

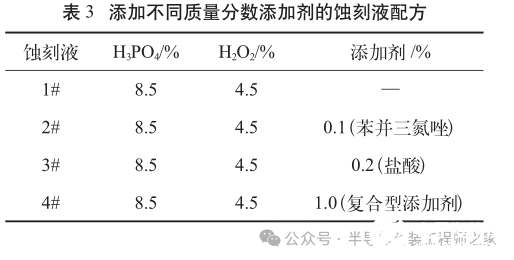

蚀刻液的基本成分如下:质量分数为 8.5%的H 3 PO 4 ,质量分数为 4.5%的 H 2 O 2 ,其余成分为水。在此基础上,添加一定量的盐酸、苯并三氮唑、复合型添加剂来降低电偶腐蚀效应。

2.2 主要仪器与设备

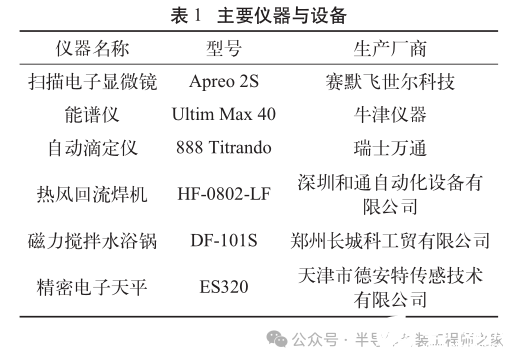

实验使用的主要仪器与设备如表 1 所示。

2.3 实验方法

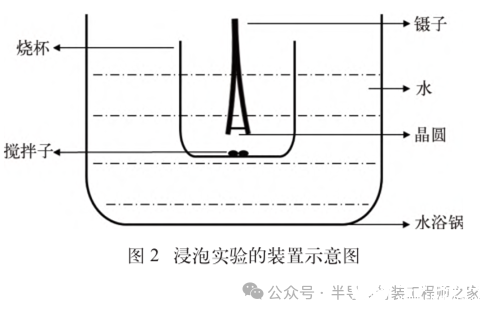

在烧杯中配置实验所需的蚀刻液 100 g,加入衬四氟磁力搅拌子后,将烧杯放入水浴锅进行控温;将磁力搅拌子的转速调节为 50~60 r/min,将水浴锅的温度控制在(23±0.5)℃进行样片的浸泡实验,使用塑料镊子来固定裁剪好的晶圆(2 cm×2 cm)。该晶圆的蚀刻实验使用秒表作为计时工具。图 2 为浸泡实验的装置示意图。

使用结构晶圆进行蚀刻实验,设蚀刻结构假片时通过秒表记录的蚀刻时长为 t 0 。结合实际生产中的工艺窗口需求,在蚀刻 2 倍的 t 0 时长后取出样品。

使用扫描电子显微镜(SEM)拍照并测量样品中的 RDL、凸点上电镀铜镀层的尺寸,分别用 D R 、D 表示蚀刻后的 RDL 中电镀铜镀层(RDL 铜)在水平方向的单侧损失量和凸点上电镀铜镀层(凸点铜)在水平方向的单侧损失量。PVD 铜镀层(PVD 铜)的厚度 D 0 =

3 000 魡。

PVD 铜的平均蚀刻速率 v 0 为

RDL 铜与凸点铜的蚀刻速率分别为 v R 、v P ,v R 与 v P的计算式为

2.4 测量方法

用秒表测量蚀刻过程的时间,使用 SEM 测量蚀刻前后不同结构上金属的尺寸变化和蚀刻后凸点结构的表面形貌,使用能谱仪(EDS)测量凸点结构表面的金属元素组成。

3 实验结果与讨论

3.1 铜蚀刻中的电偶腐蚀实验

电偶腐蚀产生有三个必要条件:1)材料具有不同的腐蚀电位,电偶腐蚀的驱动力是被腐蚀金属与跟其产生电连接的高电位金属或非金属之间产生的电位差;2)存在离子导电支路,电解质必须连续地存在于接触金属之间,构成电偶腐蚀电池的离子导电支路;3)存在电子导电支路,即被腐蚀金属与电位高的金属或非金属之间要么直接接触,要么通过其他电子导体实现电连接,构成腐蚀电池的电子导电支路 [10] 。因此,凸点结构具备产生电偶腐蚀的基本条件。

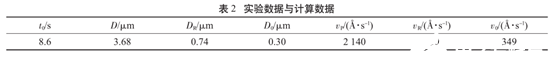

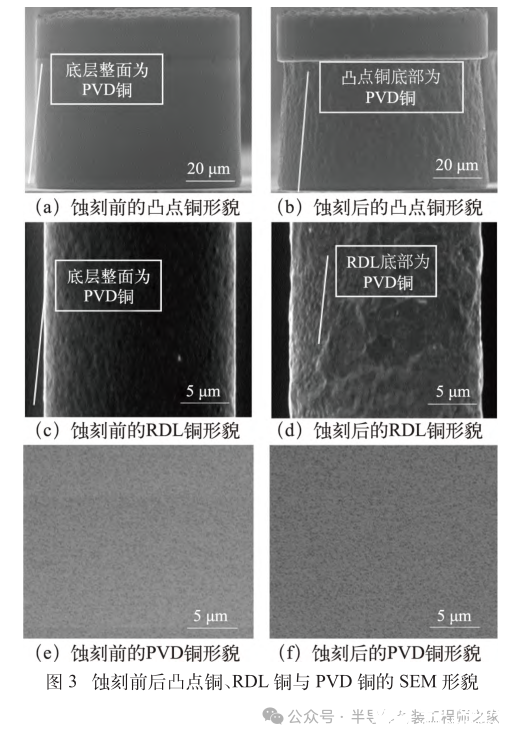

使用铜蚀刻液进行铜蚀刻实验,实验数据以及通过式(1)(2)(3)计算所得的数据如表 2 所示。蚀刻前后凸点铜、RDL 铜与 PVD 铜的 SEM 形貌如图 3 所示。从表 2 可以看出,凸点铜与 RDL 铜的蚀刻速率 v P 与v R 均高于 PVD 铜的蚀刻速率 v 0 。

从图 3(b)(d) 可以看出,对比蚀刻后凸点铜与RDL 铜的表面形貌,RDL 铜有明显的晶格感。从图 3(f)可以看出,蚀刻后的 PVD 铜表面呈现类圆形微颗粒。由此可知,蚀刻后的凸点铜与 RDL 铜产生了更明显的粗糙状态,这将有利于在铜蚀刻过程中增大铜与蚀刻液的接触面积,进而加快蚀刻速率。

基于表 2 数据,同为电镀铜的情况下,凸点铜的蚀刻速率明显高于 RDL 铜的蚀刻速率。对比凸点铜与RDL 铜的结构可知,凸点铜的上层接触多种金属结构。通过观察蚀刻后的凸点铜形貌可以发现,越靠近上层金属镍时,凸点铜的尺寸收缩越大,即蚀刻速率越快,凸点铜的损失量为 3.68 μm。

根据凸点结构的制作过程可知,裸露在蚀刻液中的金属元素分别为银、锡、镍和铜,通过电镀的方式将锡、银沉积在晶圆上,形成的是锡、银混合金属层,而非共晶的合金。在未经过热回流时,锡、银仅以物理堆叠的方式沉积在一起。在这种多层金属结构的蚀刻作业中,非常容易产生电偶腐蚀,即镍、锡、银中的一种或几种元素与凸点铜形成电偶腐蚀。

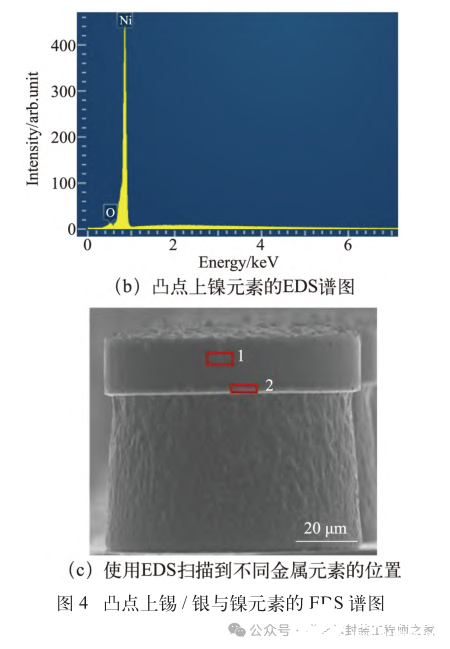

金属按照电势自低到高排序为镍、锡、铜、银。在电偶腐蚀过程中,高电势金属为阴极,且仅作为电极导通电子的传递,并不参与得失电子的反应 [10] 。

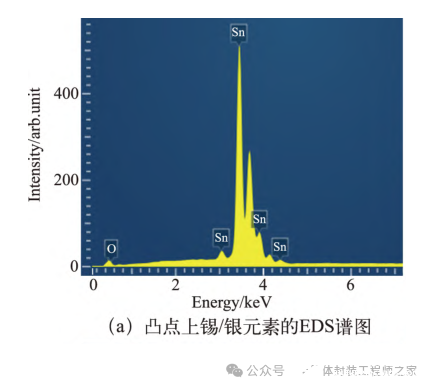

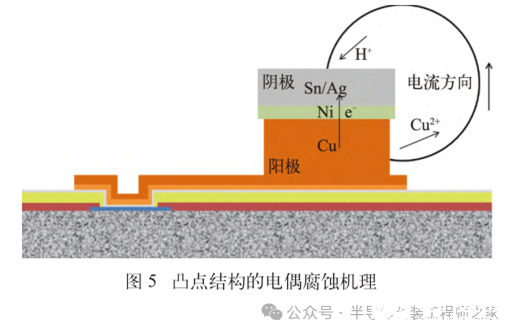

使用 SEM 对蚀刻后的晶圆进行定位,用 EDS 进行元素扫描,图 4(a)为凸点上锡 / 银元素的 EDS 谱图,图 4(b)为凸点上镍元素的 EDS 谱图。使用 EDS 扫描到锡 / 银元素的位置(位置 1)和镍元素的位置(位置2)如图 4(c)所示。

根据 Apreo 2S 的技术参数,当电压为 10 kV 时,SEM 在金属表面的理论扫描深度为 100~500 nm。从图 4(a)可以看出,锡元素的质量分数约为 98.6%,氧元素的质量分数约为 1.4%,未发现银元素。从图 4(b)可以看出,镍元素的质量分数约为 99.7%,氧元素的质量分数约为 0.3%。

根据以上分析数据基本可以判断,在锡 / 银混合金属层中未发现银元素,这说明银元素的分布与含量不足以响应 EDS 的扫描分析。由于 EDS 的分析结果只能定性判断金属表层的元素组成,并不能作为准确定量分析的依据。基于此分析数据,并以氧化锡、氧化镍的元素组成作为表层氧化物质进行估算,锡、镍元素在凸点结构表面的氧化深度应为 1~30 nm。结合蚀刻后的凸点形貌可以观察到,凸点上存在锡元素与镍元素的位置未有明显的蚀刻反应。综合分析以上数据及蚀刻现象,凸点上的锡、镍元素在蚀刻过程中,符合张宝宏等人研究的金属钝化理论 [10] ,即凸点结构中的锡、镍元素因在磷酸、双氧水的蚀刻环境中产生了钝化膜而未被腐蚀,所以在凸点结构的电偶腐蚀中未能参与阳极反应。

据此可以判断,凸点结构中锡、镍元素因钝化作用,很难参与电偶腐蚀的阳极反应,主要是电镀铜作为电偶腐蚀的阳极参与电偶腐蚀反应。所以此结构中,银与铜分别作为阴极与阳极形成电偶腐蚀。凸点结构的电偶腐蚀机理如图 5 所示。

3.2 蚀刻液中的添加剂对电偶腐蚀的影响

凸点结构中的电偶腐蚀是凸点铜产生加速蚀刻的主要原因。抑制凸点中电镀铜的收缩,需要抑制电偶腐蚀的产生或改变电偶腐蚀的电流方向。

缓蚀剂对铜腐蚀的影响研究结果表明,苯并三氮唑(BTA)类含有 N、S、P 等极性基团或不饱和键的有机化合物可以与铜发生配位,从而形成[Cu(I)BTA]类的络合膜层,该膜层可阻断铜的腐蚀反应 [11-13] 。据此,可以通过添加对铜有络合作用的物质,如 BTA 类物质,以减缓或阻碍电偶腐蚀过程中外部离子电路的导通,从而达到抑制电偶腐蚀的目的。

针对电偶腐蚀防护的方法,张文毓提出了阳极牺牲层的保护概念 [14] 。一些研究提出了改变阴阳极面积比例的概念 [15-16] 。改变电偶腐蚀的阳极种类或者减小阴阳极的面积比,可以分摊电偶腐蚀过程中铜的损伤或者降低阴阳极之间的电势差。根据实验结果,可以添加盐酸等对锡、镍氧化膜有破坏作用的物质,以达到破坏阴极或者转移阳极的目的 [17-18] 。

此外,根据材料厂商提供的性能参数,复合型添加剂兼具以上两种功能:一方面通过络合吸附作用阻断铜在电偶腐蚀中的离子传导;另一方面减缓锡、镍元素表面形成钝化膜的速度,防止锡、镍元素表面形成阴极,以达到抑制电偶腐蚀的目的。

选用苯并三氮唑、盐酸以及飞凯材料提供的复合型添加剂进行蚀刻液配制,并进行蚀刻实验。在遴选添加剂比例的实验中发现,苯并三氮唑的添加量过高会导致蚀刻速率过低,无法完成对比实验;添加量过低则起不到保护作用。盐酸的添加量过高则会严重腐蚀锡、镍层,破坏凸点的基本结构;添加量过低则达不到转移阳极的目的。复合型添加剂的添加比例为材料商推荐的比例。据此,遴选合适的添加比例后,对蚀刻效果进行评估。此实验所用的配方如表 3 所示。

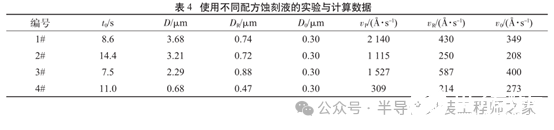

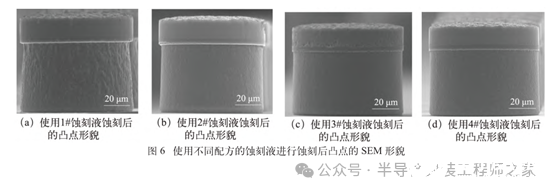

根据第 2 节提出的实验方法与计算方法进行数据收集,在进行蚀刻实验后,使用 SEM 对蚀刻后的凸点进行拍照,实验数据以及通过式(1)(2)(3)计算所得的数据如表 4 所示。使用不同配方的蚀刻液进行蚀刻后凸点的 SEM 形貌如图 6 所示。

从图 6 可见,相较于采用无添加剂的 1# 蚀刻液蚀刻后的凸点形貌,分别添加了三种添加剂的蚀刻液对凸点的电偶腐蚀均有抑制作用。复合型添加剂对电镀铜的保护效果非常明显。

根据 2# 蚀刻液的 v P 、v R 、v 0 可以看出,BTA 对抑制RDL 铜蚀刻与凸点铜蚀刻均有一定作用。使用 2# 蚀刻液蚀刻后的凸点形貌如图 6(b)所示,通过添加铜络合剂有利于保护电镀铜,对抑制电镀铜的电偶腐蚀有正向作用。

对比 2#、3# 蚀刻液的 D 发现,对锡、镍钝化膜有破坏作用的盐酸,其抑制电偶腐蚀的作用比 BTA 更明显。使用 3# 蚀刻液蚀刻后的凸点形貌如图 6(c)所示,3# 蚀刻液抑制电镀铜电偶腐蚀的效果比 2# 蚀刻液更明显,但3#蚀刻液对锡、镍表层有明显腐蚀作用。

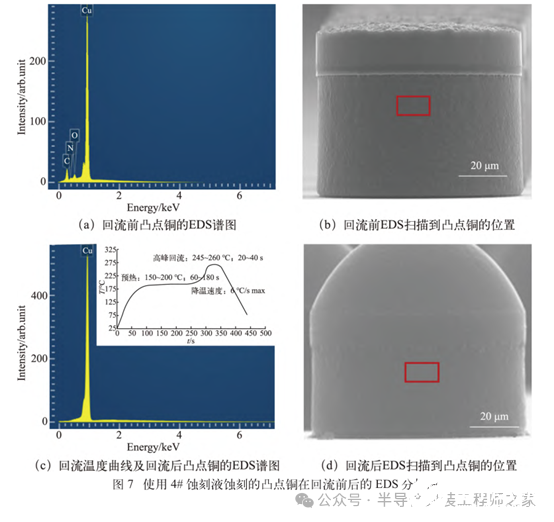

从 4# 蚀刻液的 v P 、v R 、v 0 可以看出,添加了复合型添加剂的蚀刻液在进行 RDL 铜蚀刻时,其 v R 低于v 0 ,这说明复合型添加剂对 v R 的抑制作用大于对 v 0 的抑制作用。使用 4# 蚀刻液时 v P 大于 v R ,说明复合型添加剂不能完全阻断凸点铜的电偶腐蚀反应。使用4# 蚀刻液蚀刻后的凸点形貌如图 6(d)所示,可以看出,复合型添加剂对电偶腐蚀的抑制效果最明显。据此,为验证复合型添加剂对电镀铜的吸附效果以及对凸点结构表面的影响,对蚀刻后的晶圆进行 SEM 定位后使用 EDS 进行元素扫描。图 7(a) 为回流前凸点铜的EDS 谱图,回流前 EDS 扫描到凸点铜的位置(红框位置)如图 7(b)所示。

从图 7(a)可知,凸点铜表面有碳、氮、氧、铜四种元素,碳元素的质量分数为 1.3%,氮元素的质量分数为 0.1%,氧元素的质量分数 0.3%,铜元素的质量分数为 98.3%,这说明 4# 蚀刻液中的添加剂在凸点铜表面可以吸附微量有机物。

为保证有机物不影响凸点与基板的后续焊接工艺,需保证凸点结构在金属回流后,金属表面吸附的添加剂可挥发或者升华。对使用 4# 蚀刻液蚀刻后的晶圆进行高温回流处理,高温回流温度曲线如图 7(c)所示,对回流后的凸点铜表面进行 EDS 扫描,EDS 扫描到凸点铜的位置(红框位置)如图 7(d)所示。根据图7(c)的分析结果可以看出,在凸点铜表面不存在有机物残留峰,即按照凸点工艺的常规条件处理后,可阻断添加剂的有机物对凸点的污染。

4 结论

本文合理解释了凸点铜在磷酸、双氧水蚀刻液中存在的电偶腐蚀现象。凸点铜在此条件下的横向蚀刻量可达 3.68 μm。相同条件下对比 RDL 铜的蚀刻量,因电偶腐蚀造成的横向蚀刻量应为 2.94 μm。据此计算,电偶腐蚀造成的凸点铜蚀刻厚度约为 PVD 铜蚀刻厚度(0.3 μm)的 4.9 倍。

通过分析 EDS 数据、蚀刻后形貌可知,在磷酸、双氧水的蚀刻环境中,凸点结构中的锡、镍两种金属在蚀刻液中形成了具有保护作用的钝化膜,致使锡、镍元素在凸点的电偶腐蚀过程中得到保护。

使用具有络合功能的苯并三氮唑作为添加剂,在添加质量分数为 0.1%的苯并三氮唑时,其对改善电偶腐蚀有明显效果,相较于不含添加剂的蚀刻液,可降低凸点铜的横向蚀刻量约 13%;使用对锡、镍钝化膜有破坏作用的盐酸作为添加剂,在添加质量分数为0.2%的盐酸时,经蚀刻后镍、锡表层有明显腐蚀迹象,降低凸点铜的横向蚀刻量约 38%;添加质量分数为1%的复合型添加剂,蚀刻后凸点的锡、镍表层结构完好,降低凸点铜的横向蚀刻量约 82%,该蚀刻液表现最为优良。

对使用复合型添加剂蚀刻液蚀刻后的凸点进行回流工艺的可靠性验证。使用 EDS 对凸点表面进行元素分析,并未发现其他元素的残留。

近期成为热点的芯粒(Chiplet)技术,是将多个具有特定功能的芯粒,通过先进封装的形式组合在一起,最终形成一个系统芯片的过程。Chiplet 技术对先进封装的工艺技术提出了新的挑战。多芯片组合互联过程所需的 RDL 铜线,在尺寸上会更小(线宽线距为1~2 μm),工艺过程所允许的 RDL 铜尺寸也将更小(0.2 μm 左右)。新技术的应用对蚀刻液提出了更高的要求。后续将针对复合型添加剂在铜表面吸附保护以及减缓锡、镍元素形成钝化膜的作用机理展开深入研究,可以为 Chiplet 技术的应用提供有效的蚀刻技术方案。

审核编辑 黄宇

-

半导体

+关注

关注

339文章

31316浏览量

266957 -

封装

+关注

关注

128文章

9345浏览量

149098 -

电镀

+关注

关注

16文章

478浏览量

25907 -

电偶

+关注

关注

0文章

50浏览量

15579 -

蚀刻

+关注

关注

10文章

431浏览量

16691

发布评论请先 登录

新型HERB技术如何重塑芯片蚀刻工艺

一文详解封装基板的制备工艺

台积电计划建设4座先进封装厂,应对AI芯片需求

【新启航】玻璃晶圆 TTV 厚度在光刻工艺中的反馈控制优化研究

PCB设计避坑指南:死铜残留的危害与实战处理技巧

化圆为方,台积电整合推出最先进CoPoS半导体封装

湿法蚀刻工艺与显示检测技术的协同创新

长电科技江阴成立子公司聚焦先进封装

用于 ARRAY 制程工艺的低铜腐蚀光刻胶剥离液及白光干涉仪在光刻图形的测量

电偶腐蚀对先进封装铜蚀刻工艺的影响

电偶腐蚀对先进封装铜蚀刻工艺的影响

评论