需要带宽的视频流应用程序和 IP 语音 (VoIP) 等对延迟敏感的服务正在扩大网络限制。然而,为各种通信服务增加更多的网络容量将不可避免地转化为巨大的成本和复杂性开销。此外,为满足各种网络元素而专门构建的专有网络服务器也难以管理和维护。如果你为这些单一功能的盒子选择外包路径,你最好开始重新考虑你的预算。

这就是为什么电信运营商、企业网络供应商和系统集成商越来越多地寻求网络边缘的接入解决方案,以减少专用、专有网络设备的数量。

进入软件定义的广域网 (SD-WAN)。

SD-WAN:边缘的 SDN

为了解决上述许多问题,当今的数据中心网络基础设施是围绕 SDN 构建的。通过将虚拟网络功能 (VNF) 从控制平面和数据平面解耦,网络运营商可以采用更通用的设备,这些设备可以重新用于各种服务。除了灵活性之外,这还降低了复杂性和成本。

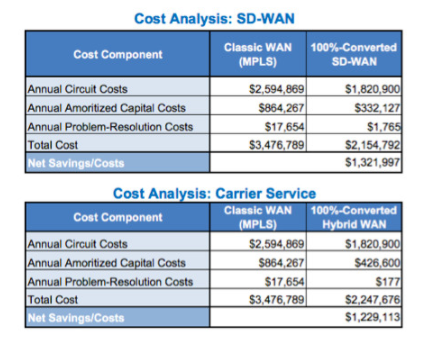

源自 SDN 世界的软件定义广域网 (SD-WAN) 系统还从使用网络的应用程序中抽象出网络硬件和传输特性。只有这些系统是为边缘接入网络设计的。因此,与传统 WAN 相比,SD-WAN 可提高网络敏捷性并降低成本(图 1)。

图 1.与传统 WAN 相比,软件定义的广域网 (SD-WAN) 技术显着降低了成本

同样重要的是,SD-WAN 解决方案使运营商能够为下一代企业和物联网工作负载增加性能和灵活性。当 VNF 可以托管在数据中心并通过网络远程交付到边缘的 SD-WAN 设备时尤其如此。

通用客户端设备 (uCPE) 是 SD-WAN 运行的硬件基础。uCPE 是一种新兴的网络功能支持虚拟化(NFV-enabled)设备,它定义了一套现成的硬件和开放软件技术,提供了一个虚拟化环境,网络服务提供商在该环境之上部署 SDN 和 VNF 功能和服务。

希望使用 uCPE 将类似数据中心的虚拟化功能带入网络边缘的开发人员可以使用 Supermicro 的 SuperServer 5019D-FN8TP等解决方案快速入门。5019D-FN8TP 是一款 uCPE SD-WAN 控制器,能够在网络边缘运行多个 VNF,包括路由、虚拟专用网络 (VPN) 和防火墙。

5019D-FN8TP 基于八核、16 线程Intel® Xeon® D 处理器,并在四个插槽中支持高达 512 GB 的 DDR4 内存。该平台的 M.2 和 Mini-PCIe 插槽还提供额外的存储和网络容量。

5019D-FN8TP 从其他白盒解决方案中脱颖而出的原因在于,它是首批英特尔® uCPE 精选解决方案之一,该程序提供了经过全面测试和验证的网络硬件和软件堆栈,可帮助开发人员轻松集成各种VNF 和 SD-WAN 覆盖架构。

因此,5019D-FN8TP 解决方案使网络设计人员能够通过使用现成的硬件和软件组件包来简化边缘网络,这些组件可以为新的网络服务和功能动态配置。

来自英特尔® 至强® D 的网络辅助

5019D-FN8TP 还支持集成到 Xeon® D 处理器中的补充技术,包括英特尔® 定向 I/O 虚拟化技术(英特尔® VT-d)、英特尔® 数据平面开发套件(英特尔® DPDK)和英特尔® QuickAssist 技术(英特尔® QAT)。例如,英特尔VT-d提供硬件支持,用于隔离和限制设备对管理设备的分区所有者的访问。在 5019D-FN8TP 服务器解决方案中,这确保了通过虚拟网络路由推送数据流量的虚拟机 (VM) 的高效访问。

同样,英特尔DPDK有助于优化特定 VNF 的数据流量,并有效地将它们与 SD-WAN 流集成。DPDK 技术提高了英特尔至强等处理平台的吞吐量和数据包处理性能。

最后,至强处理器中的英特尔QAT通过将数据中心级别的安全性带到边缘来补充软件定义的环境。它通过从主机处理器卸载非对称加密、对称加密和身份验证、数字签名和数据压缩等安全操作来提供硬件加速的性能提升。因此,作为 5019D-FN8TP 等系统核心的 Xeon 处理器内核为 SD-WAN 功能提供了更多的计算能力。

SD-WAN,经过测试和优化

通过 Intel Select Solutions 计划,SuperMicro 的 SuperServer 5019D-FN8TP 已经过验证,可以满足特定的 Xeon D 处理器工作负载优化要求。现成的设计解决方案还在 BIOS、固件、操作系统和 VM 级别由 Supermicro 和英特尔进行了预测试和预验证。

作为一个可部署的参考平台,5019D-FN8TP 使开发人员可以花费更少的时间、精力和费用来评估硬件和软件选项。相反,他们可以专注于部署具有 VNF 的 SD-WAN,以满足其特定的边缘网络用例,从而最大限度地提高带宽、降低成本并启用新的创收服务。

电信运营商、企业服务提供商、网络集成商,甚至物联网组织现在都可以自信地将边缘网络扩展到增强/虚拟现实、5G 等领域。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

20325浏览量

254693 -

操作系统

+关注

关注

37文章

7432浏览量

129597 -

数据中心

+关注

关注

18文章

5754浏览量

75195

发布评论请先 登录

2026年SD-WAN国内厂家有哪些?SD-WAN厂商推荐!

SD-WAN网关是什么、有什么功能和应用场景

SD-WAN技术介绍

SD-WAN 技术深度解析:原理、组成、优势与组网应用

SD-WAN与SASE主要区别是什么?SASE会取代SD-WAN吗?

2025年SD-WAN厂家市场排名,如何选择合适的SD-WAN?

SD-WAN重塑企业网络架构,推动国际化发展

哪些企业适合使用SD-WAN组网?

SD-WAN国际网络专线是什么?适合哪些场景使用?

什么是SD-WAN?它的优势有哪些?如何搭建SD-WAN?

SD-WAN和传统WAN的区别

SD-WAN是什么?SD-WAN专线适用于哪些场景?

国内做SD-WAN公司有哪些?SD-WAN厂商推荐

AI时代的SD-WAN异地组网如何落地?

SD-WAN部署时,如何确保数据安全?

SD-WAN将数据中心级虚拟化带到边缘

SD-WAN将数据中心级虚拟化带到边缘

评论