晶振是个大家族,除了简单封装时钟振荡器(SPXO) 外,更有压控晶体振荡器(VCXO)、温补晶体振荡器(TCXO)、恒温晶体振荡器(OCXO),以及数字补偿晶体振荡器(MCXO或DTCXO),每种类型都有独特的性能,例如相位噪声和抖动(jitter)这两个指标。

什么是相位噪声和抖动?

简单讲,抖动(jitter)是某一事件的时程与理想时程的时间偏差,单位以fs(微微秒、飞秒,即10-15秒),或者ps(皮秒,1ps = 1000fs = 10-12秒)表示。

如果用仪器测量,呈现出的是信号的频域特性,称作“相位噪声(Phase Noise)”。本质上,这两者是一样的,只是表述方式不同而已。

(1)抖动

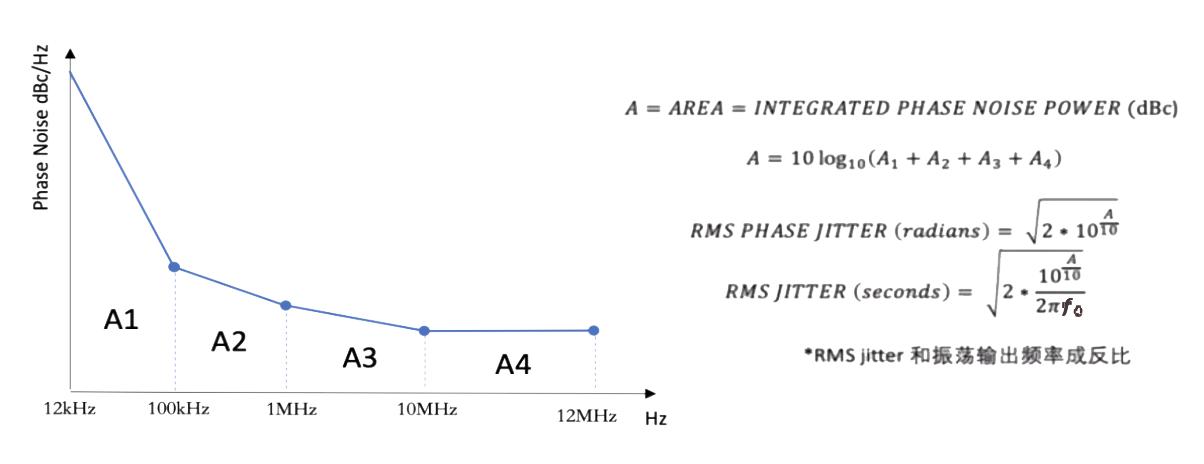

抖动分确定性抖动(Deterministic jitter,DJ)和随机性抖动(Random jitter,RJ)两种。DJ通常幅度有限,以单位时间表示;RJ为高斯分布,以RMS均方根值表示,RMS Jitter值大小与振荡输出频率成反比。

晶体振荡器的RMS Jitter值与输出频率成反比

晶体振荡器的RMS Jitter值与输出频率成反比

晶振的抖动通常由噪声引起,并导致频率不稳定。对于精密电子仪器、无线电定位、高速目标跟踪和宇航通信等应用领域,选择低噪声晶振十分重要。

(2)相位噪声

相位噪声(Phase Noise)是抖动在测量仪器上的表现,通常定义为一个振荡器在某一偏移频率fm处1Hz宽带内的单边信号功率和信号总功率比值,单位是dBc/Hz,通常表示为dBc/Hz@fm。

若没有相位噪声,振荡器的整个功率都集中在f0(10MHz为例),功率频谱就是一条以f0为中心的直线,且信号为纯正的正弦波。但是任何信号都有不稳定性,从而产生了边带sideband。

相位噪声的来源主要有三方面:

(1)晶体品质Q值。高频晶体有很高的近载波相位噪声(Close-in Phase Noise), 因为他们有低的Q值和更宽的边带。

(2)晶体外围电路:包括包括IC、RC元件、引脚等。

(3)信号输出(白噪声)。

高速系统对晶振相位噪声的要求

在通信网络、无线传输、ATM和SONET等高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。不仅如此,它还会导致通信链路的误码率增大,甚至限制A/D转换器的动态范围。有资料表明,在3GHz以上的系统中,时间抖动(jitter)会导致码间干扰(ISI),造成传输误码率上升,这就要求晶振选型必须满足严格的抖动指标。

如果需要设备即开即用,就必须选用VCXO或温补晶振;如果要求稳定度在0.5ppm以上,则需选择数字温补晶振(MCXO)。模拟温补晶振适用于稳定度要求在5ppm~0.5ppm之间的需求。VCXO只适合于稳定度要求在5ppm以下的产品。在不需要即开即用的环境下,如果需要信号稳定度超过0.1ppm的,可选用OCXO。

面向高速通讯应用的高频低噪声晶体振荡器

面向高速通讯应用的高频低噪声晶体振荡器

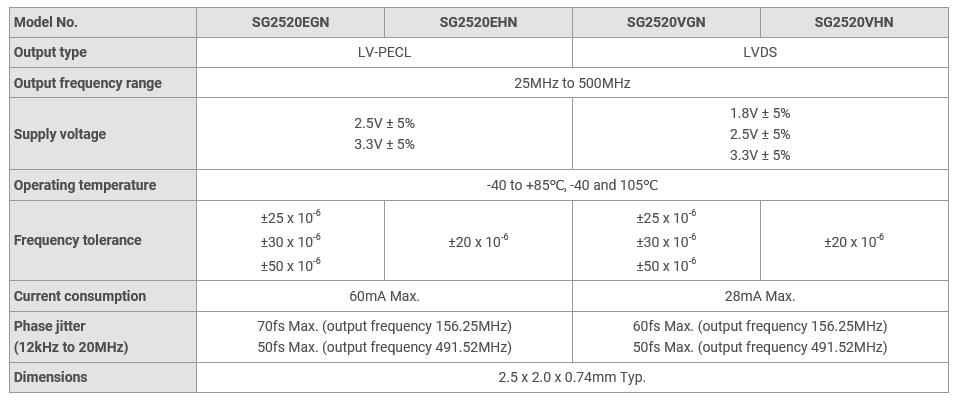

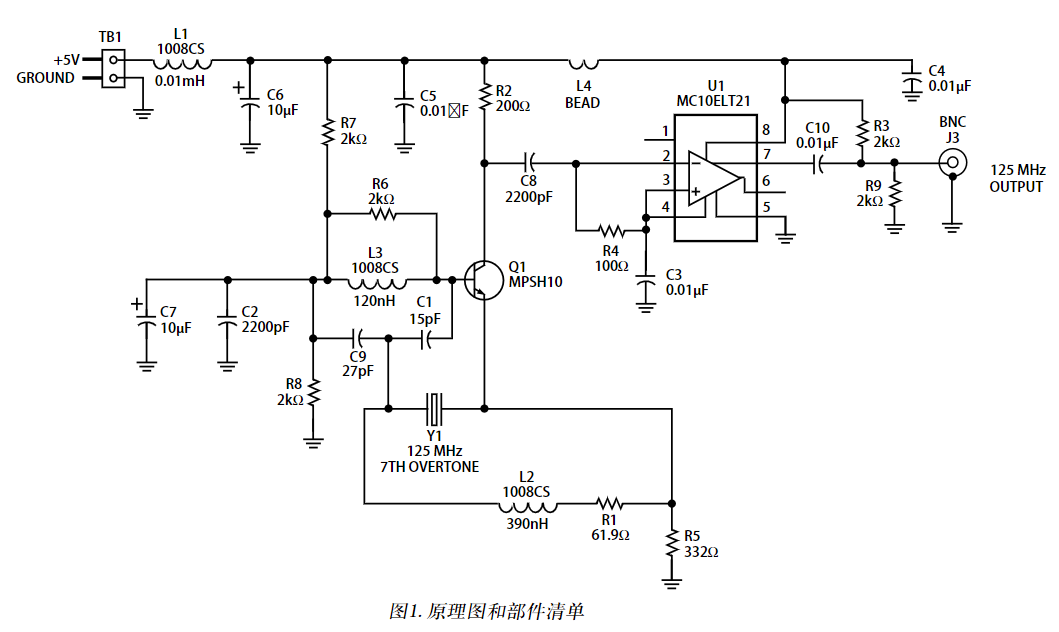

一般来说,晶体振荡器的相位噪声在远离中心频率的频率下有所改善。TCXO和OCXO振荡器以及其它利用基波或谐波方式的晶体振荡器具有最好的相位噪声性能。采用锁相环合成器产生输出频率的振荡器比采用非锁相环技术的振荡器一般呈现较差的相位噪声性能。例如,对于需要低噪声、稳定和精确时钟源的工业级设备(比如收发器模块或数据中心),可选择150fs小型塑封石英PLL振荡器;而通讯、导航、雷达应用领域的要求会有更高如50fs,这需要将100MHz以上基波起振的高频石英晶体单元与噪音特性优越的振荡IC相组合。

审核编辑:汤梓红

-

晶振

+关注

关注

35文章

3442浏览量

72651 -

抖动

+关注

关注

1文章

70浏览量

19332 -

相位噪声

+关注

关注

2文章

191浏览量

23637

发布评论请先 登录

相位噪声测试:为什么专用分析仪优于通用仪器

O-CS-22低相位噪声晶体振荡器

是德示波器相位噪声测试

完整的直接数字频率合成器 AD9850 的分立、低相位噪声、125MHz 晶振解决方案

相位噪声和抖动的定义 高速系统对晶振相位噪声的要求

相位噪声和抖动的定义 高速系统对晶振相位噪声的要求

评论